# LME49710 High Performance, High Fidelity Audio Operational Amplifier

#### **General Description**

The LME49710 is part of the ultra-low distortion, low noise, high slew rate operational amplifier series optimized and fully specified for high performance, high fidelity applications. Combining advanced leading-edge process technology with state-of-the-art circuit design, the LME49710 audio operational amplifiers deliver superior audio signal amplification for outstanding audio performance. The LME49710 combines a very high slew rate with vanishingly low THD+N to easily satisfy the most demanding audio applications. To ensure that the most challenging loads are driven without compromise, the LME49710 has a high slew rate of  $\pm 20V/\mu$ s and an output current capability of  $\pm 26$ mA. Further, dynamic range is maximized by an output stage that drives  $2k\Omega$  loads to within 1V of either power supply voltage and to within 1.4V when driving  $600\Omega$  loads.

The LME49710 has a wide supply range of  $\pm 2.5V$  to  $\pm 17V$ . Over this supply range the LME49710's input circuitry maintains excellent common-mode and power supply rejection, as well as maintaining its low input bias current. The LME49710 is unity gain stable. It retains its outstanding performance while driving difficult capacitive loads with values as high as 100pF.

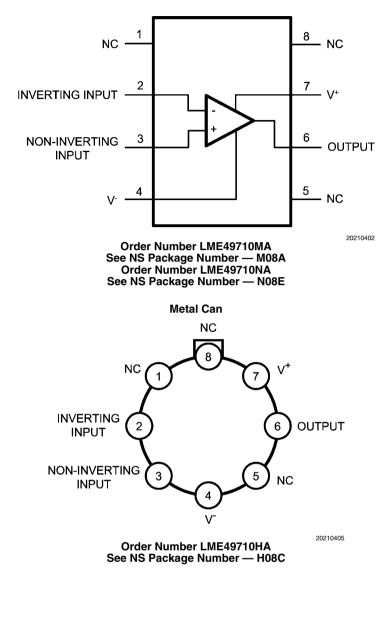

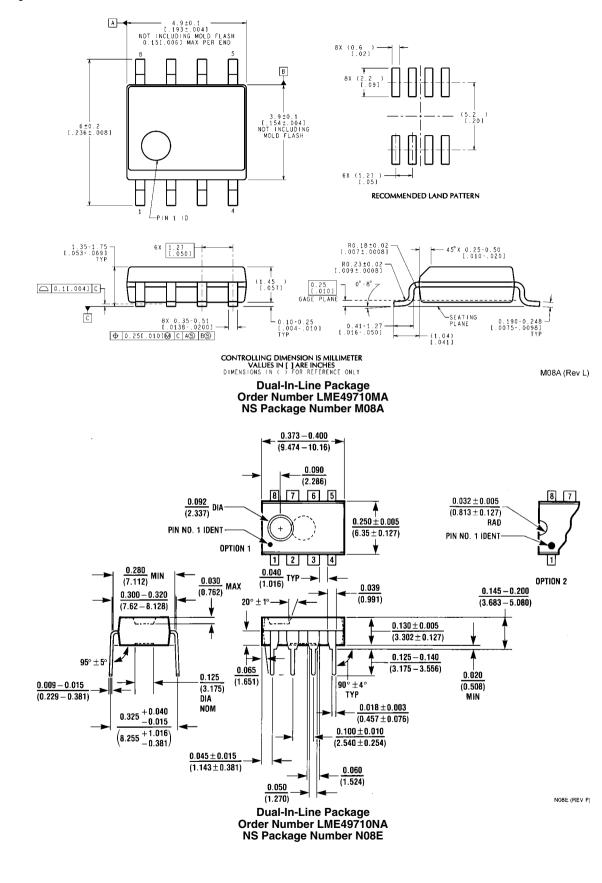

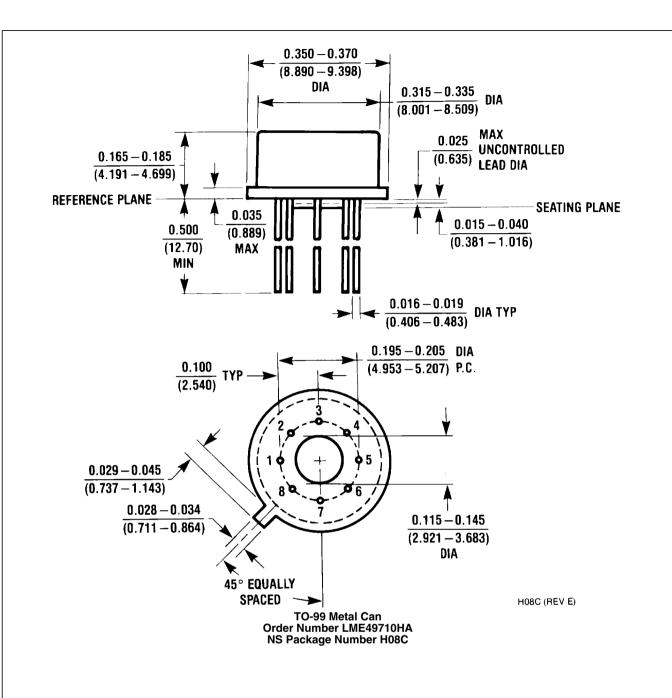

The LME49710 is available in 8–lead narrow body SOIC, 8– lead plastic DIP, and 8–lead metal can TO-99. Demonstration boards are available for each package.

### **Key Specifications**

| • •                                                          |                                 |  |  |  |

|--------------------------------------------------------------|---------------------------------|--|--|--|

| Power Supply Voltage Range                                   | ±2.5V to ±17V                   |  |  |  |

| THD+N ( $A_V = 1$ , $V_{OUT} = 3V_{RMS}$ , $f_{IN} = 1$ kHz) |                                 |  |  |  |

| $R_L = 2k\Omega$                                             | 0.00003% (typ)                  |  |  |  |

| R <sub>L</sub> = 600Ω                                        | 0.00003% (typ)                  |  |  |  |

| Input Noise Density                                          | 2.5nV/ $\sqrt{\text{Hz}}$ (typ) |  |  |  |

| Slew Rate                                                    | ±20V/μs (typ)                   |  |  |  |

| Gain Bandwidth Product                                       | 55MHz (typ)                     |  |  |  |

| ■ Open Loop Gain (R <sub>L</sub> = 600Ω)                     | 140dB (typ)                     |  |  |  |

|                                                              |                                 |  |  |  |

- Input Bias Current 7nA (typ)

- Input Offset Voltage 0.05mV (typ)

#### **Features**

- Easily drives 600Ω loads

- Optimized for superior audio signal fidelity

- Output short circuit protection

- PSRR and CMRR exceed 110dB (typ)

- SOIC, DIP, TO-99 metal can packages

### Applications

- Ultra high quality audio amplification

- High fidelity preamplifiers

- High fidelity multimedia

- State of the art phono pre amps

- High performance professional audio

- High fidelity equalization and crossover networks

- High performance line drivers

- High performance line receivers

- High fidelity active filters

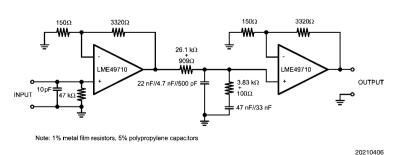

### **Typical Application**

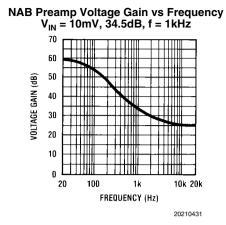

#### FIGURE 1. Passively Equalized RIAA Phono Preamplifier

November 2006

# **Connection Diagrams**

# Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Distributors for availability a                     | nd specifications.         | θ <sub>JA</sub> (SO)          | 145°C                          |

|-----------------------------------------------------|----------------------------|-------------------------------|--------------------------------|

| Power Supply Voltage                                |                            | θ <sub>JA</sub> (NA)          | 102°C                          |

| (V <sub>S</sub> = V <sup>+</sup> - V <sup>-</sup> ) | 36V                        | θ <sub>JA</sub> (HA)          | 150°C                          |

| Storage Temperature                                 | –65°C to 150°C             | θ <sub>.IC</sub> (HA)         | 35°C                           |

| Input Voltage                                       | (V-) - 0.7V to (V+) + 0.7V | Temperature Range             |                                |

| Output Short Circuit (Note 3)                       | Continuous                 | $T_{MIN} \le T_A \le T_{MAX}$ | –40°C ≤ T₄ ≤ 85°C              |

| Power Dissipation                                   | Internally Limited         | Supply Voltage Range          | 71                             |

| ESD Susceptibility (Note 4)                         | 2000V                      | Cupply Vollage Hange          | $\pm 2.5V \le V_S \le \pm 17V$ |

ESD Susceptibility (Note 5)

Junction Temperature

Thermal Resistance

### **Electrical Characteristics**

|                         |                                                               |                                                                                                                                              | LME            | LME49710               |                    |

|-------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|--------------------|

| Symbol                  | Parameter                                                     | Conditions                                                                                                                                   | Typical Limit  |                        | Units              |

|                         |                                                               |                                                                                                                                              | (Note 6)       | (Notes 7, 8)           | (Limits)           |

|                         |                                                               | $A_V = 1, V_{OUT} = 3V_{RMS}$                                                                                                                |                |                        |                    |

| THD+N                   | Total Harmonic Distortion + Noise                             | $R_L = 2k\Omega$                                                                                                                             | 0.00003        |                        | % (max)            |

|                         |                                                               | R <sub>L</sub> = 600Ω                                                                                                                        | 0.00003        | 0.00009                | % (max)            |

| IMD                     | Intermodulation Distortion                                    | A <sub>V</sub> = 1, V <sub>OUT</sub> = 3V <sub>RMS</sub><br>Two-tone, 60Hz & 7kHz 4:1<br>V <sub>IN</sub> = 1V <sub>P-P</sub> , 1kHz residual | 0.00005        |                        | % (max)            |

| GBWP                    | Gain Bandwidth Product                                        |                                                                                                                                              | 55             | 45                     | MHz (min)          |

| SR                      | Slew Rate                                                     |                                                                                                                                              | ±20            | ±15                    | V/µs (min)         |

| FPBW                    | Full Power Bandwidth                                          | $V_{OUT} = 1V_{P-P}$ , -3dB<br>referenced to output magnitude<br>at f = 1kHz                                                                 | 10             |                        | MHz                |

| t <sub>s</sub>          | Settling time                                                 | $A_V = 1$ , 10V step, $C_L = 100 pF$<br>0.1% error range                                                                                     | 1.2            |                        | μs                 |

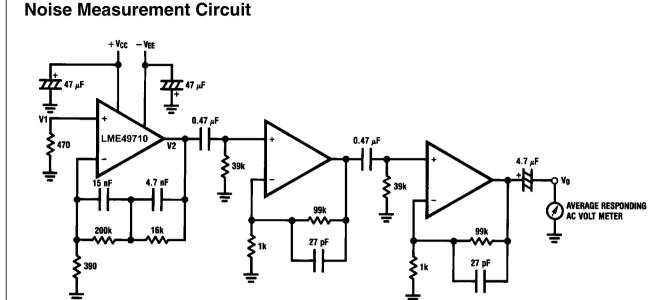

|                         | Equivalent Input Noise Voltage                                | f <sub>BW</sub> = 20Hz to 20kHz                                                                                                              | 0.34           | 0.65                   | μV <sub>RMS</sub>  |

| e <sub>n</sub>          | Equivalent Input Noise Density                                | f = 1kHz<br>f = 10Hz                                                                                                                         | 2.5<br>6.4     | 4.7                    | nV/√Hz<br>nV/√Hz   |

| i <sub>n</sub>          | Current Noise Density                                         | f = 1kHz<br>f = 10Hz                                                                                                                         | 1.6<br>3.1     |                        | pA/√Hz<br>pA/√Hz   |

| V <sub>OS</sub>         | Offset Voltage                                                |                                                                                                                                              | ±0.05          | ±0.7                   | mV (max)           |

| ΔV <sub>OS</sub> /ΔTemp | Average Input Offset Voltage Drift vs<br>Temperature          | 40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                                                 | 0.2            |                        | μV/°C              |

| PSRR                    | Average Input Offset Voltage Shift vs<br>Power Supply Voltage | $\Delta V_{\rm S} = 20 V \text{ (Note 9)}$                                                                                                   | 125            | 110                    | dB (min)           |

| I <sub>B</sub>          | Input Bias Current                                            | $V_{CM} = 0V$                                                                                                                                | 7              | 72                     | nA (max)           |

| ΔI <sub>OS</sub> /ΔTemp | Input Bias Current Drift vs<br>Temperature                    | –40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                                                | 0.1            |                        | nA/°C              |

| I <sub>os</sub>         | Input Offset Current                                          | $V_{CM} = 0V$                                                                                                                                | 5              | 65                     | nA (max)           |

| V <sub>IN-CM</sub>      | Common-Mode Input Voltage Range                               |                                                                                                                                              | +14.1<br>-13.9 | (V+) - 20<br>(V-) + 20 | V (min)<br>V (min) |

| CMRR                    | Common-Mode Rejection                                         | -10V <v<sub>CM&lt;10V</v<sub>                                                                                                                | 120            | 110                    | dB (min)           |

| 7                       | Differential Input Impedance                                  |                                                                                                                                              | 30             |                        | kΩ                 |

| Z <sub>IN</sub>         | Common Mode Input Impedance                                   | -10V <v<sub>CM&lt;10V</v<sub>                                                                                                                | 10             |                        | MΩ                 |

|                         |                                                               | –10V <v<sub>OUT&lt;10V, R<sub>L</sub> = 600Ω</v<sub>                                                                                         | 140            |                        | dB                 |

| A <sub>VOL</sub>        | Open Loop Voltage Gain                                        | $-10V < V_{OUT} < 10V, R_L = 2k\Omega$                                                                                                       | 140            |                        | dB                 |

|                         |                                                               | $-10V < V_{OUT} < 10V, R_{L} = 10k\Omega$                                                                                                    | 140            |                        | dB                 |

LME49710

200V 150°C

| 0 |

|---|

| - |

| ~ |

| ດ |

| 4 |

| Щ |

|   |

| < |

|   |

|                     | Parameter                    | Conditions                                   | LME      | LME49710     |                   |

|---------------------|------------------------------|----------------------------------------------|----------|--------------|-------------------|

| Symbol              |                              |                                              | Typical  | Limit        | Units<br>(Limits) |

|                     |                              |                                              | (Note 6) | (Notes 7, 8) |                   |

|                     | Maximum Output Voltage Swing | R <sub>L</sub> = 600Ω                        | 13.6     | ±12.5        | V                 |

| V <sub>OUTMAX</sub> |                              | $R_L = 2k\Omega$                             | 14.0     |              | V                 |

|                     |                              | $R_L = 10k\Omega$                            | 14.1     |              | V                 |

| I <sub>OUT</sub>    | Output Current               | R <sub>L</sub> = 600Ω, V <sub>S</sub> = ±17V | ±26      | ±23          | mA (min)          |

| 1                   | Short Circuit Current        |                                              | +53      |              | mA                |

| OUT-CC              |                              |                                              | -42      |              | mA                |

|                     | Output Impedance             | f <sub>IN</sub> = 10kHz                      |          |              |                   |

| R <sub>OUT</sub>    |                              | Closed-Loop                                  | 0.01     |              | Ω                 |

|                     |                              | Open-Loop                                    | 13       |              | Ω                 |

| C <sub>LOAD</sub>   | Capacitive Load Drive        | Overshoot                                    |          |              |                   |

|                     |                              | 10%                                          | 100      |              | pF                |

|                     |                              | 25%                                          | 200      |              | pF                |

| I <sub>S</sub>      | Quiescent Current            | I <sub>OUT</sub> = 0mA                       | 4.8      | 5.5          | mA (max)          |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 3: Amplifier output connected to GND, any number of amplifiers within a package.

Note 4: Human body model, 100pF discharged through a  $1.5 k\Omega$  resistor.

Note 5: Machine Model ESD test is covered by specification EIAJ IC-121-1981. A 200pF cap is charged to the specified voltage and then discharged directly into the IC with no external series resistor (resistance of discharge path must be under 50 $\Omega$ ).

Note 6: Typical specifications are specified at +25°C and represent the most likely parametric norm.

Note 7: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 9: PSRR is measured as follows:  $V_{OS}$  is measured at two supply voltages, ±5V and ±15V. PSRR =  $|20log(\Delta V_{OS}/\Delta V_S)|$ .

### **Application Hints**

The LME49710 is a high speed op amp with excellent phase margin and stability. Capacitive loads up to 100pF will cause little change in the phase characteristics of the amplifiers and are therefore allowable.

#### Capacitive loads greater than 100pF must be isolated from the output. The most straight forward way to do this is to put a resistor in series with the output. This resistor will also prevent excess power dissipation if the output is accidentally shorted.

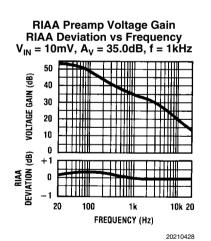

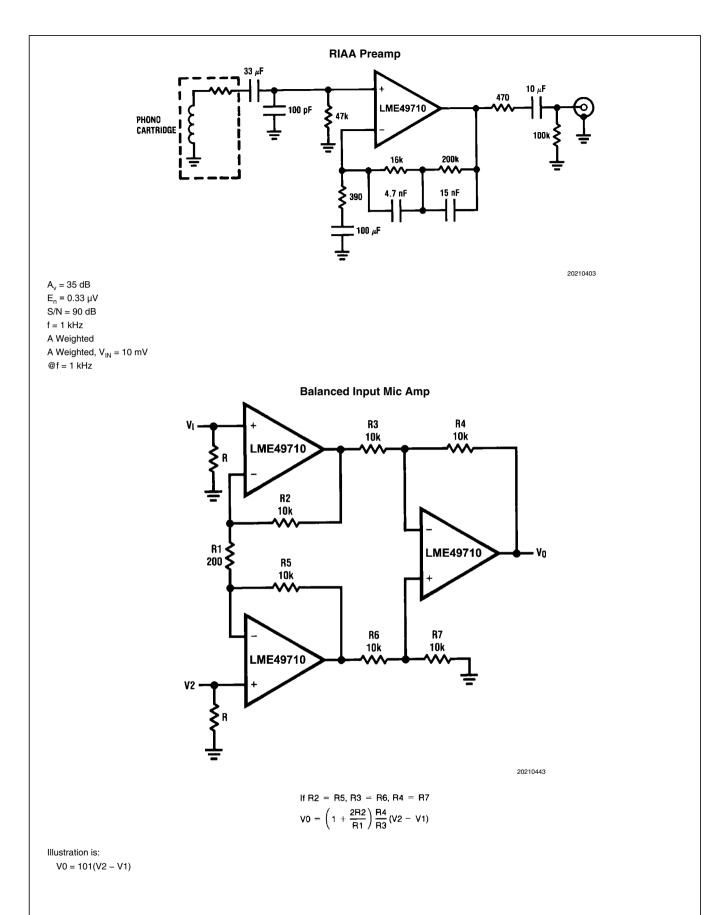

RIAA PREAMP 35 dB, 1=1 kHz

20210427

#### Complete shielding is required to prevent induced pick up from external sources. Always check with oscilloscope for power line noise.

Total Gain: 115 dB at f = 1 kHz

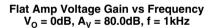

FLAT AMP. 40 dB + 40 dB

www.national.com

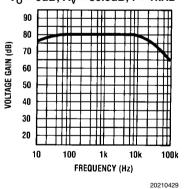

# **Typical Applications**

$A_{V} = 34.5$ . F = 1 kHz E<sub>n</sub> = 0.38 μV A Weighted

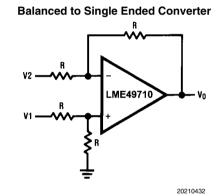

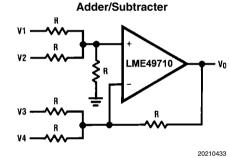

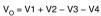

$V_0 = V1 - V2$

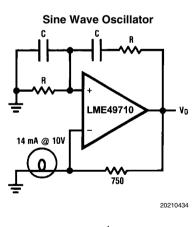

$f_0 = \frac{1}{2\pi RC}$

Illustration is  $f_0 = 1 \text{ kHz}$ , Q = 10,  $A_{BP} = 1$

### **Application Information**

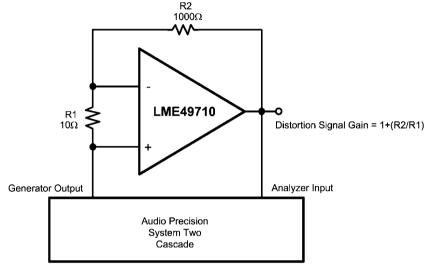

#### DISTORTION MEASUREMENTS

The vanishingly low residual distortion produced by LME49710 is below the capabilities of all commercially available equipment. This makes distortion measurements just slightly more difficult than simply connecting a distortion meter to the amplifier's inputs and outputs. The solution, however, is quite simple: an additional resistor. Adding this resistor extends the resolution of the distortion measurement equipment.

The LME49710's low residual distortion is an input referred internal error. As shown in Figure 1, adding the  $10\Omega$  resistor connected between the amplifier's inverting and non-inverting

inputs changes the amplifier's noise gain. The result is that the error signal (distortion) is amplified by a factor of 101. Although the amplifier's closed-loop gain is unaltered, the feedback available to correct distortion errors is reduced by 101, which means that measurement resolution increases by 101. To ensure minimum effects on distortion measurements, keep the value of R1 low as shown in Figure 1.

This technique is verified by duplicating the measurements with high closed loop gain and/or making the measurements at high frequencies. Doing so produces distortion components that are within the measurement equipment's capabilities. This datasheet's THD+N and IMD values were generated using the above described circuit connected to an Audio Precision System Two Cascade.

Actual Distortion = AP Value/100

20210407

#### FIGURE 2. THD+N and IMD Distortion Test Circuit

| Revision History |          |                  |  |  |

|------------------|----------|------------------|--|--|

| Rev              | Date     | Description      |  |  |

| 1.0              | 11/16/07 | Initial release. |  |  |

#### Physical Dimensions inches (millimeters) unless otherwise noted

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2006 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560