This synchronous 4-bit binary counter features an internal carry look-ahead to application in high-speed counting designs. Synchronous operation is provided by having all flipflops clock simultaneously so that the outputs change coincident with each other when so instructed by the countenable inputs and internal gating. This mode of operation eliminates the output counting spikes that are normally associated with asynchronous (ripple clock) counters. A buffered clock input triggers the four flip-flops on the rising (positivegoing) edge of the clock input waveform. This counter is fully programmable; that is, the outputs may be preset to either level. As presetting is synchronous, setting up a low level at the load input disables the counter and causes the outputs to agree with the setup data after the next clock pulse regardless of the levels of the enable inputs. Low-to-high transitions at the load input would be avoided when the clock is low if the enable inputs are high at or before the transition. The clear function is asynchronous and a low level at the clear input sets all four of the flip-flop outputs low after the next clock pulse. regardless of the levels of the enable inputs. This synchronous clear allows the count length to be modified easily as decoding the maximum count desired can be accomplished with one external NAND gate.

The gate output is connected to the clear input to synchronously clear the counter to LLLL. Low-to-high transitions at the clear input should be avoided when the clock is low if the enable and load inputs are high at or before the transition. The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications without additional gating.

Instrumental in accomplishing this function are two countenable inputs and a ripple carry output. Both count-enable inputs (P and T) must be high to count, and input T is fed forward to enable the ripple carry output. The ripple carry output thus enabled will produce a high-level output pulse with a duration approximately equal to the high-level portion of the  $\mathbf{Q}_{\mathbf{A}}$  output.

This high-level overflow ripple carry pulse can be used to enable successive cascaded stages. High-to-low-level transitions at the enable P or T inputs should occur only when the clock input is high.

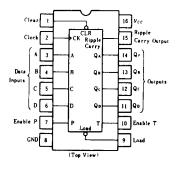

#### **PPIN ARRANGEMENT**

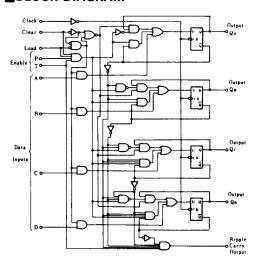

#### **BLOCK DIAGRAM**

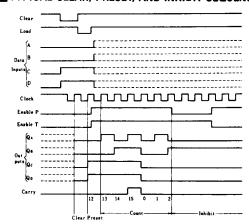

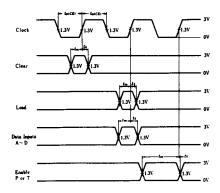

#### **TYPICAL CLEAR, PRESET, AND INHIBIT SEQUENCE**

#### **■ RECOMMENDED OPERATING CONDITIONS**

| Ite                                                 | em          | Symbol  | min | typ | max | Unit |  |

|-----------------------------------------------------|-------------|---------|-----|-----|-----|------|--|

| Clock frequency Clock pulse width Clear pulse width |             | frlack  | 0   | _   | 25  | MHz  |  |

|                                                     |             | tie(CK) | 25  | -   | -   | ns   |  |

|                                                     |             | le(CLR) | 20  | _   |     | ns   |  |

| Setup time                                          | A, B, C, D  |         | 20  |     |     | ns   |  |

|                                                     | Enable P, T | 1.      | 20  | -   | -   | ns   |  |

|                                                     | Load        | 1 800   | 20  | _   | _   | ns   |  |

|                                                     | Clear       | 1       | 20  | _   | -   | ns   |  |

| Hold time                                           |             | th      | 5   | _   | -   | ns   |  |

## **ETIMING DEFINITION**

# **TELECTRICAL CHARACTERISTICS** ( $Ta = -20 \sim +75$ °C )

| Item                         |                          | Symbol | Test Condition                                    | ns                        | min  | typ* | max  | Unit |

|------------------------------|--------------------------|--------|---------------------------------------------------|---------------------------|------|------|------|------|

| Input voltage                |                          | VIH    |                                                   |                           | 2.0  | -    | -    | V    |

|                              |                          | VIL    |                                                   |                           | -    | _    | 0.8  | V    |

| Output voltage               |                          | Von    | $V_{CC} = 4.75V$ , $V_{IH} = 2V$ , $V_{IL} = 0$ . | 8V, $I_{OH} = -400 \mu A$ | 2.7  | _    | -    | V    |

|                              |                          | Vol    | $V_{CC} = 4.75V, V_{IH} = 2V$                     | $I_{OL} = 4 \text{mA}$    |      |      | 0.4  | V    |

|                              |                          |        | $\dot{V}_{IL} = 0.8 \text{V}$                     | <i>Io L</i> = 8m A        |      | -    | 0.5  | V    |

| Input current                | Data, Enable P           |        |                                                   |                           |      | _    | 20   |      |

|                              | Load, Clock,<br>Enable T | Іін    | $V_{CC} = 5.25 \text{V}, V_I = 2.7 \text{V}$      | _                         | -    | 40   | μA   |      |

|                              | Clear                    | 1      |                                                   | _                         | -    | 40   |      |      |

|                              | Data, Enable P           |        |                                                   |                           | _    | -0.4 |      |      |

|                              | Load, Clock.<br>Enable T | 111.   | $V_{CC} = 5.25 \text{V}, \ V_I = 0.4 \text{V}$    |                           |      |      | -0.8 | mΑ   |

|                              | Clear                    |        |                                                   | _                         | _    | -0.8 |      |      |

|                              | Data, Enable P           |        |                                                   | _                         | _    | 0.1  | mA   |      |

|                              | Load, Clock,<br>Enable T | Iı .   | $V_{CC} = 5.25 \text{V}, V_I = 7 \text{V}$        | -                         | -    | 0.2  |      |      |

|                              | Clear                    | 1      |                                                   |                           | _    | 0.2  |      |      |

| Short-circuit output current |                          | los    | V <sub>CC</sub> = 5.25V                           |                           | - 20 | _    | -100 | mA   |

| Supply current**             |                          | Ісен   | $V_{CC} = 5.25 \text{V}$                          |                           |      | 18   | 31   | mA   |

|                              |                          | lcc1.  | $V_{CC} = 5.25 \text{V}$                          |                           |      | 19   | 32   | mA   |

| Input clamp voltage          |                          | Vik    | $V_{CC} = 4.75 \text{V}, I_{IN} = -18 \text{mA}$  |                           | -    | _    | -1.5 | V    |

<sup>\*</sup> VCC=5V, Ta=25°C

# **ESWITCHING CHARACTERISTICS** ( $V_{CC} = 5V$ , $T_{a} = 25^{\circ}C$ )

| Item                    | Symbol | Inputs     | Outputs        | Test Conditions                                      | min | typ | max | Unit |

|-------------------------|--------|------------|----------------|------------------------------------------------------|-----|-----|-----|------|

| Maximum clock frequency | fmax   | Clock      | $Q_A \sim Q_D$ |                                                      | 25  | 32  | -   | MHz  |

| Propagation delay time  | tpl.H  | a          | Ripple         |                                                      | -   | 20  | 35  | ns   |

|                         | tphi.  | Clock      | Carry          |                                                      | -   | 18  | 35  | ns   |

|                         | tela   | Clock      | $Q_A \sim Q_D$ |                                                      | _   | 13  | 24  | ns   |

|                         | teni.  | (Load="H") |                | $C_L = 15 \mathrm{pF}$ , $R_L = 2 \mathrm{k} \Omega$ | -   | 18  | 27  | ns   |

|                         | ter.n  | Clock      | $Q_A = Q_D$    |                                                      |     | 13  | 24  | ns   |

|                         | tphi.  | (Load="L") |                |                                                      |     | 18  | 27  | ns   |

|                         | tPLH   |            | Ripple         |                                                      | -   | 9   | 14  | ns   |

|                         | trui.  | Enable T   | Carry          |                                                      | -   | 9   | 14  | ns   |

|                         | tphi.  | Clear      | $Q_A \sim Q_D$ |                                                      | -   | 20  | 28  | ns   |

<sup>\*\*</sup> I<sub>CCH</sub> is measured with the load input high, then again with the load input low, with all other inputs high and all outputs open.

I<sub>CCL</sub> is measured with the clock input high, then again with the clock input low, with all other inputs low and all outputs open.

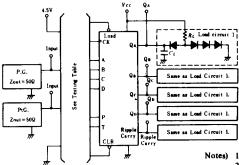

## **ETESTING METHOD**

#### 1) Test Circuit

Notes) 1.  $C_L$  includes probe and jig capacitance. 2. All diodes are 1S2074 H.

#### 2) Testing Table

| Item           | From input to      | Inputs |      |        |      |       |      |      |      |      | Outputs        |     |     |        |       |

|----------------|--------------------|--------|------|--------|------|-------|------|------|------|------|----------------|-----|-----|--------|-------|

|                |                    | Clear  | Load | Enable |      | C     | Data |      |      |      |                |     |     | Ripple |       |

|                | output             |        |      | P      | T    | Clock | A    | В    | С    | D    | Q <sub>A</sub> | Qв  | Qc  | Qυ     | Carry |

| f≡ax           |                    | 4.5V   | 4.5V | 4.5V   | 4.5V | IN    | GND  | GND  | GND  | GND  | OUT            | OUT | OUT | OUT    | OUT   |

| tpi.н<br>tpнi. | CK→Ripple<br>Carry | 4.5V   | 4.5V | 4.5V   | 4.5V | IN    | GND  | GND  | GND  | GND  | _              | _   |     | -      | OUT   |

|                | CK→Q               | 4.5V   | 4.5V | 4.5V   | 4.5V | IN    | GND  | GND  | GND  | GND  | OUT            | OUT | OUT | OUT    | _     |

|                | CK→Q               | 4.5V   | GND  | GND    | GND  | IN    | IN*  | IN*  | IN*  | IN*  | OUT            | OUT | OUT | OUT    |       |

|                | Enable T→Ripple    | 4.5V   | GND  | 4.5V   | IN   | IN*   | 4.5V | 4.5V | 4.5V | 4.5V | _              | _   |     | -      | OUT   |

|                | CLR→Q              | IN     | GND  | GND    | GND  | IN*   | 4.5V | 4.5V | 4.5V | 4.5V | OUT            | OUT | OUT | OUT    |       |

<sup>\*</sup> For initialized

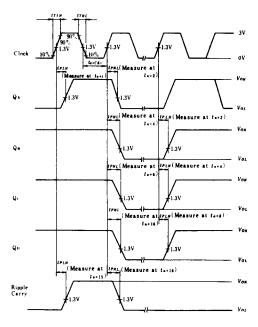

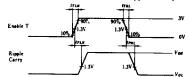

## Waveform-1 fmax, tPLH, tPHL (Clock-Q, Ripple Carry)

Notes) 1. Clock input pulse:  $t_{TLH} \le 15 \text{ns}$ ,  $t_{THL} \le 6 \text{ns}$ , PRR = 1 MHz, duty cycle=50% and: for  $f_{max}$ ,  $t_{TLH} = t_{THL} \le 2.5 \text{ns}$ .

2.  $t_n$  is reference bit time when all outputs are low.

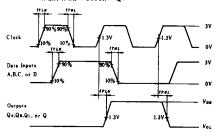

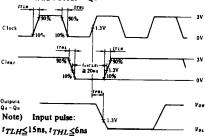

#### Waveform-2 tPLH, tPHL (Clock→Q)

Notes) Input pulse:  $t_{TLH} \le 15$ ns,  $t_{THL} \le 6$ ns, Clock input: PRR = 1MHz, duty cycle 50%, Data input: PRR = 500kHz, duty cycle 50%

## Waveform-3 tplH, tpHL (Enable T→Ripple Carry)

Note) Input pulse:  $t_{TLH} \le 15 \text{ ns}$ ,  $t_{THL} \le 6 \text{ ns}$ , PRR = 1 MHz

#### Waveform-4 tPHL (Clear→Q)

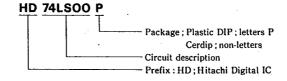

# **PACKAGING INFORMATIONS**

Factory orders for circuits described in this databook should include a three-part type number as explained in the following example.

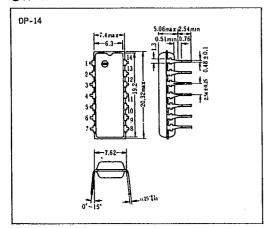

## ■Plastic DIP

## ●14 Pin

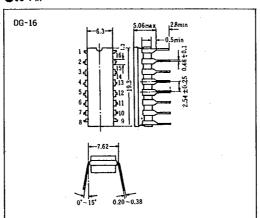

## ●16 Pin

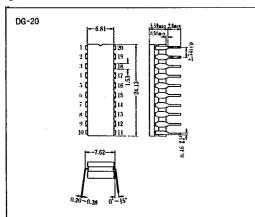

## ●20 Pin

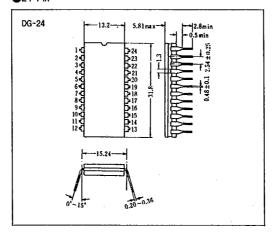

●24 Pin

## **PACKAGING INFORMATIONS**

## **■**Cerdip

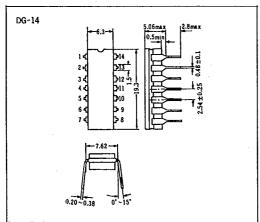

●14 Pin

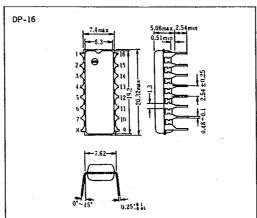

# ●16 Pin

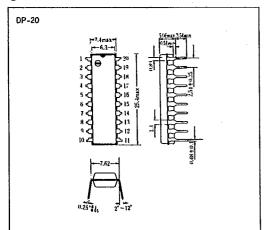

## ●20 Pin

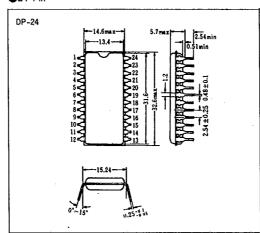

## ●24 Pin