# National Semiconductor

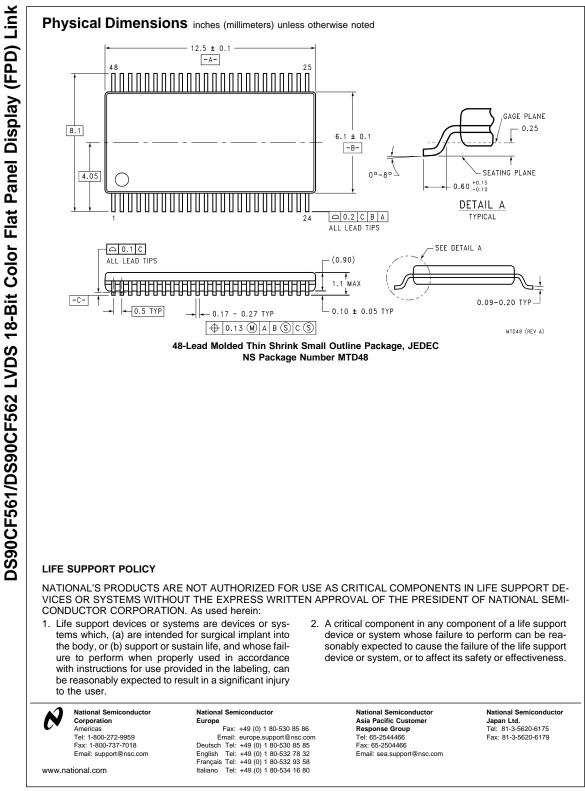

## DS90CF561/DS90CF562 LVDS 18-Bit Color Flat Panel Display (FPD) Link

#### **General Description**

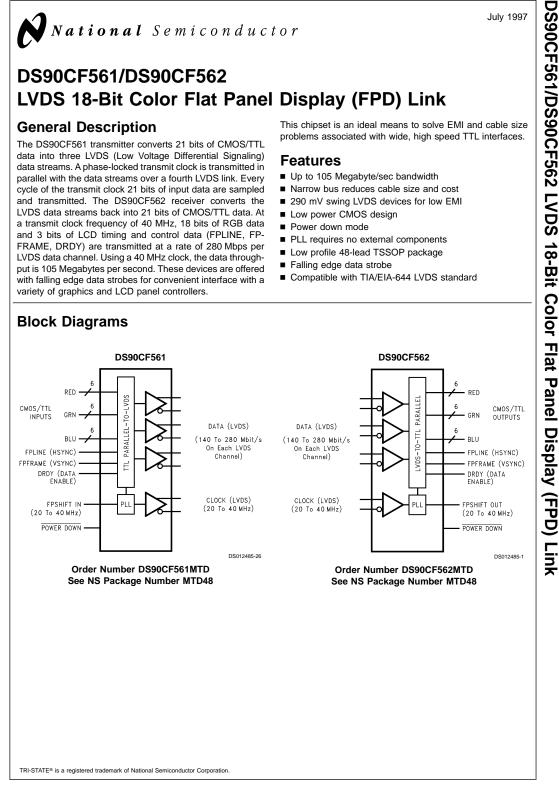

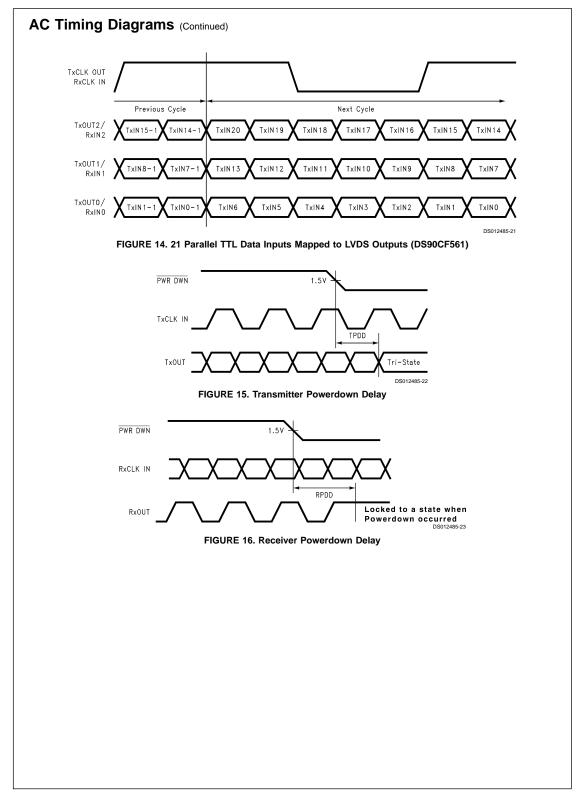

The DS90CF561 transmitter converts 21 bits of CMOS/TTL data into three LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fourth LVDS link. Every cycle of the transmit clock 21 bits of input data are sampled and transmitted. The DS90CF562 receiver converts the LVDS data streams back into 21 bits of CMOS/TTL data. At a transmit clock frequency of 40 MHz, 18 bits of RGB data and 3 bits of LCD timing and control data (FPLINE, FP-FRAME, DRDY) are transmitted at a rate of 280 Mbps per LVDS data channel. Using a 40 MHz clock, the data throughput is 105 Megabytes per second. These devices are offered with falling edge data strobes for convenient interface with a variety of graphics and LCD panel controllers.

This chipset is an ideal means to solve EMI and cable size problems associated with wide, high speed TTL interfaces.

July 1997

#### Features

- Up to 105 Megabyte/sec bandwidth

- Narrow bus reduces cable size and cost

- 290 mV swing LVDS devices for low EMI

- Low power CMOS design

- Power down mode

- PLL requires no external components

- Low profile 48-lead TSSOP package

- Falling edge data strobe

- Compatible with TIA/EIA-644 LVDS standard

© 1998 National Semiconductor Corporation DS012485

2

#### Absolute Maximum Ratings (Note 1)

.

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> ) | -0.3V to +6V                      |

|-----------------------------------|-----------------------------------|

| CMOS/TTL Input Voltage            | -0.3V to (V <sub>CC</sub> + 0.3V) |

| CMOS/TTL Ouput Voltage            | -0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Receiver Input Voltage       | –0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Driver Output Voltage        | –0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Output                       |                                   |

| Short Circuit Duration            | continuous                        |

| Junction Temperature              | +150°C                            |

| Storage Temperature Range         | –65°C to +150°C                   |

| Lead Temperature                  |                                   |

| (Soldering, 4 sec.)               | +260°C                            |

| Maximum Power Dissipation @ +25   | °C                                |

| MTD48 (TSSOP) Package:            |                                   |

| Maximum Power Dissipation @ +25   |                                   |

DS90CF561

1.98W

DS90CF562

1.89W

Package Derating:

DS90CF561

DS90CF561

16 mW/°C above +25°C

DS90CF562

15 mW/°C above +25°C

This device does not meet 2000V ESD rating (Note 4).

### Recommended Operating Conditions

|                                         | Min | Nom | Max | Units             |

|-----------------------------------------|-----|-----|-----|-------------------|

| Supply Voltage (V <sub>CC</sub> )       | 4.5 | 5.0 | 5.5 | V                 |

| Operating Free Air                      |     |     |     |                   |

| Temperature (T <sub>A</sub> )           | -10 | +25 | +70 | °C                |

| Receiver Input Range                    | 0   |     | 2.4 | V                 |

| Supply Noise Voltage (V <sub>CC</sub> ) |     |     | 100 | mV <sub>P-P</sub> |

#### **Electrical Characteristics**

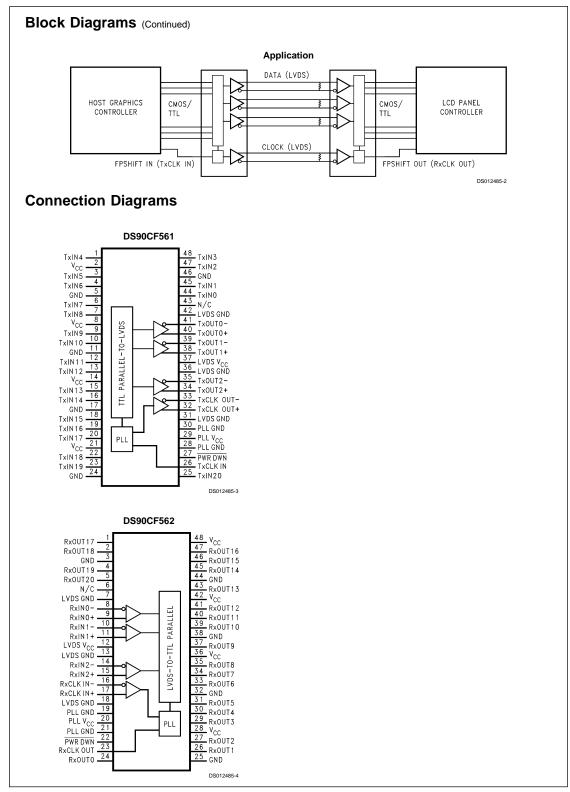

Over recommended operating supply and temperature ranges unless otherwise specified Parameter Conditions Min Units Symbol Тур Max **CMOS/TTL DC SPECIFICATIONS** High Level Input Voltage 2.0 V<sub>cc</sub> V VIH VIL Low Level Input Voltage GND 0.8 ٧ V<sub>OH</sub>  $I_{OH} = -0.4 \text{ mA}$ High Level Output Voltage 3.8 4.9 V  $I_{OL} = 2 \text{ mA}$ Low Level Output Voltage 0.1 0.3 V VOL  $I_{CL} = -18 \text{ mA}$ Input Clamp Voltage -0.79 -1.5 V  $V_{CL}$  $V_{IN} = V_{CC}$ , GND, 2.5V or 0.4V Input Current ±5.1 ±10 μΑ  $I_{IN}$ Output Short Circuit Current  $V_{OUT} = 0V$ -120 mΑ los LVDS DRIVER DC SPECIFICATIONS  $V_{OD}$ Differential Output Voltage  $R_L = 100\Omega$ 250 290 450 m٧ Change in V<sub>OD</sub> between  $\Delta V_{OD}$ 35 m٧ Complimentary Output States Common Mode Voltage 1.25 1.375 V  $V_{CM}$ 1.1 mν Change in  $V_{\rm CM}$  between  $\Delta V_{CM}$ 35 Complimentary Output States V<sub>он</sub> High Level Output Voltage 1.3 1.6 ٧ VOL Low Level Output Voltage 0.9 1.01 V Output Short Circuit Current  $V_{OUT} = 0V, R_L = 100\Omega$ -2.9 -5 mΑ los Output TRI-STATE® Current  $\overline{\text{Power Down}}$  = 0V, V<sub>OUT</sub> = 0V or V<sub>CC</sub> ±1 ±10 μΑ loz LVDS RECEIVER DC SPECIFICATIONS Differential Input High Threshold +100 V<sub>TH</sub>  $V_{CM} = +1.2V$ mV  $V_{TL}$ Differential Input Low Threshold -100 m٧  $I_{\rm IN}$ Input Current  $V_{IN} = +2.4V$  $V_{CC} = 5.5V$ ±10 μA  $V_{IN} = 0V$ ±10 μA TRANSMITTER SUPPLY CURRENT  $R_{L} = 100\Omega, C_{L} = 5 \text{ pF},$ Transmitter Supply Current, f = 32.5 MHz 34 51 I<sub>CCTW</sub> mΑ Worst Case Worst Case Pattern (Figure 1, Figure 3) f = 37.5 MHz 36 53 mΑ Transmitter Supply Current,  $R_1 = 100\Omega, C_1 = 5 \text{ pF},$ f = 32.5 MHz 27 47 mΑ  $I_{CCTG}$ 16 Grayscale Grayscale Pattern (Figure 2, Figure 3) f = 37.5 MHz 28 48 mΑ

| Elec                                                       | trical Characteristics                    | (Continued)                                    |                    |     |     |     |       |

|------------------------------------------------------------|-------------------------------------------|------------------------------------------------|--------------------|-----|-----|-----|-------|

| Over ree                                                   | commended operating supply and            | temperature ranges unless o                    | therwise specified |     |     |     |       |

| Symbol                                                     | Parameter                                 | Conditio                                       | ons                | Min | Тур | Max | Units |

| TRANSM                                                     | ITTER SUPPLY CURRENT                      |                                                |                    |     |     |     |       |

| I <sub>CCTZ</sub>                                          | Transmitter Supply Current,<br>Power Down | Power Down = Low                               |                    |     | 1   | 25  | μA    |

| RECEIVE                                                    | R SUPPLY CURRENT                          |                                                |                    |     |     |     |       |

| I <sub>CCRW</sub>                                          | Receiver Supply Current,<br>Worst Case    | $C_{L} = 8 \text{ pF},$<br>Worst Case Pattern  | f = 32.5 MHz       |     | 55  | 75  | mA    |

|                                                            |                                           | (Figure 1, Figure 4)                           | f = 37.5 MHz       |     | 60  | 80  | mA    |

| I <sub>CCRG</sub> Receiver Supply Current,<br>16 Grayscale |                                           | C <sub>L</sub> = 8 pF,<br>16 Grayscale Pattern | f = 32.5 MHz       |     | 35  | 55  | mA    |

|                                                            |                                           | (Figure 2, Figure 4)                           | f = 37.5 MHz       |     | 37  | 58  | mA    |

| I <sub>CCRZ</sub>                                          | Receiver Supply Current,<br>Power Down    | Power Down = Low                               |                    |     | 1   | 10  | μA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

Note 2: Typical values are given for V<sub>CC</sub> = 5.0V and T<sub>A</sub> = +25°C.

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except  $V_{OD}$  and  $\Delta V_{OD}$ ).

Note 4: ESD Rating:

•

HBM (1.5 kΩ, 100 pF)

PLL V  $_{CC} \ge 1000V$

All other pins  $\ge 2000V$ EIAJ (0Ω, 200 pF) ≥ 150V

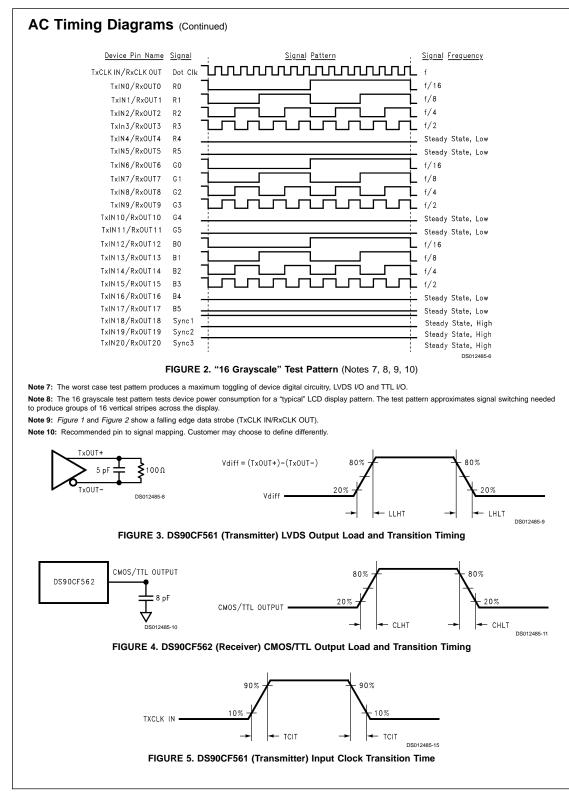

Transmitter Switching Characteristics Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol | Parameter                                               | Min        | Тур   | Max  | Units |    |

|--------|---------------------------------------------------------|------------|-------|------|-------|----|

| LLHT   | LVDS Low-to-High Transition Time (Figure 3)             |            | 0.75  | 1.5  | ns    |    |

| LHLT   | LVDS High-to-Low Transition Time (Figure 3)             |            |       | 0.75 | 1.5   | ns |

| TCIT   | TxCLK IN Transition Time (Figure 5)                     |            |       |      | 8     | ns |

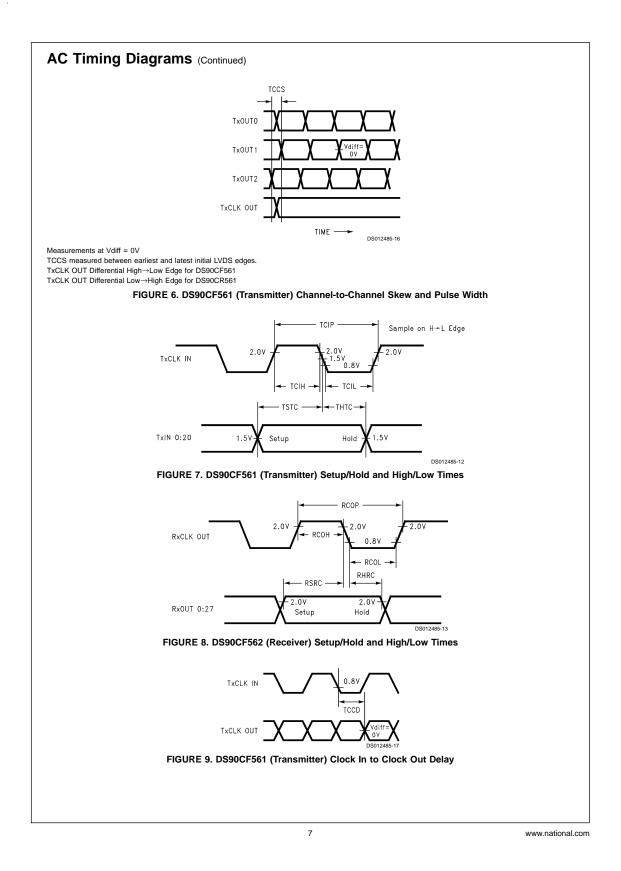

| TCCS   | TxOUT Channel-to-Channel Skew (Note 5) (Figure 6)       |            |       |      | 350   | ps |

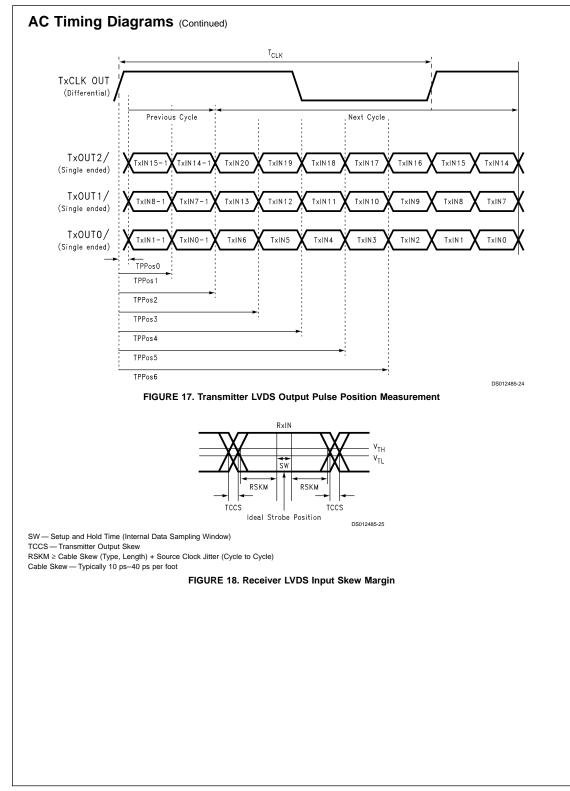

| TPPos0 | Transmitter Output Pulse Position for Bit 0 (Figure 17) | f = 20 MHz | -200  | 150  | 350   | ps |

| TPPos1 | Transmitter Output Pulse Position for Bit 1             |            | 6.3   | 7.2  | 7.5   | ns |

| TPPos2 | Transmitter Output Pulse Position for Bit 2             |            | 12.8  | 13.6 | 14.6  | ns |

| TPPos3 | Transmitter Output Pulse Position for Bit 3             |            | 20    | 20.8 | 21.5  | ns |

| TPPos4 | Transmitter Output Pulse Position for Bit 4             |            | 27.2  | 28   | 28.5  | ns |

| TPPos5 | Transmitter Output Pulse Position for Bit 5             | 34.5       | 35.2  | 35.6 | ns    |    |

| TPPos6 | Transmitter Output Pulse Position for Bit 6             | 42.2       | 42.6  | 42.9 | ns    |    |

| TPPos0 | Transmitter Output Pulse Position for Bit 0 (Figure 16) | f = 40 MHz | -100  | 100  | 300   | ps |

| TPPos1 | Transmitter Output Pulse Position for Bit 1             |            | 2.9   | 3.3  | 3.9   | ns |

| TPPos2 | Transmitter Output Pulse Position for Bit 2             |            | 6.1   | 6.6  | 7.1   | ns |

| TPPos3 | Transmitter Output Pulse Position for Bit 3             |            | 9.7   | 10.2 | 10.7  | ns |

| TPPos4 | Transmitter Output Pulse Position for Bit 4             |            | 13    | 13.5 | 14.1  | ns |

| TPPos5 | Transmitter Output Pulse Position for Bit 5             |            | 17    | 17.4 | 17.8  | ns |

| TPPos6 | Transmitter Output Pulse Position for Bit 6             |            | 20.3  | 20.8 | 21.4  | ns |

| TCIP   | TxCLK IN Period (Figure 7)                              | T          | 25    | Т    | 50    | ns |

| TCIH   | TxCLK IN High Time (Figure 7)                           |            | 0.35T | 0.5T | 0.65T | ns |

| TCIL   | TxCLK IN Low Time (Figure 7)                            |            | 0.35T | 0.5T | 0.65T | ns |

| TSTC   | TxIN Setup to TxCLK IN (Figure 7)                       | f = 20 MHz | 14    |      |       | ns |

|        |                                                         | f = 40 MHz | 8     |      |       | ns |

| THTC   | TxIN Hold to TxCLK IN (Figure 7)                        | ·          | 2.5   | 2    |       | ns |

| Over rec              | commended operating supply and temperature ranges unless otherwise specifie                                                                                                                                                                                                         | a                |     |           |          |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----------|----------|

| Symbol                | Parameter                                                                                                                                                                                                                                                                           | Min              | Тур | Max       | Units    |

| TCCD                  | TxCLK IN to TxCLK OUT Delay @ 25°C,                                                                                                                                                                                                                                                 | 5                |     | 9.7       | ns       |

|                       | $V_{CC} = 5.0V (Figure 9)$                                                                                                                                                                                                                                                          |                  |     |           |          |

| TPLLS                 | Transmitter Phase Lock Loop Set (Figure 11)                                                                                                                                                                                                                                         |                  |     | 10        | ms       |

| TPDD                  | Transmitter Powerdown Delay (Figure 15)                                                                                                                                                                                                                                             |                  |     | 100       | ns       |

|                       | eiver Switching Characteristics<br>commended operating supply and temperature ranges unless otherwise specifie                                                                                                                                                                      | d                |     |           |          |

| Symbol                | Parameter                                                                                                                                                                                                                                                                           | Min              | Тур | Max       | Units    |

| CLHT                  | CMOS/TTL Low-to-High Transition Time (Figure 4)                                                                                                                                                                                                                                     |                  | 3.5 | 6.5       | ns       |

| CHLT                  | CMOS/TTL High-to-Low Transition Time (Figure 4)                                                                                                                                                                                                                                     |                  | 2.7 | 6.5       | ns       |

| RCOP                  | RxCLK OUT Period (Figure 8)                                                                                                                                                                                                                                                         | 25               | Т   | 50        | ns       |

| RSKM                  |                                                                                                                                                                                                                                                                                     | 0 MHz 1.1        |     |           | ns       |

|                       |                                                                                                                                                                                                                                                                                     | 0 MHz 700        |     |           | ps       |

| RCOH                  |                                                                                                                                                                                                                                                                                     | 0 MHz 21.5       |     |           | ns       |

|                       |                                                                                                                                                                                                                                                                                     | 0 MHz 10.5       |     |           | ns       |

| RCOL                  |                                                                                                                                                                                                                                                                                     | 0 MHz 19         |     |           | ns       |

|                       |                                                                                                                                                                                                                                                                                     | 0 MHz 6          |     |           | ns       |

| RSRC                  |                                                                                                                                                                                                                                                                                     | 0 MHz 14         |     |           | ns       |

|                       |                                                                                                                                                                                                                                                                                     | 0 MHz 4.5        |     |           | ns       |

| RHRC                  |                                                                                                                                                                                                                                                                                     | 0 MHz 16         |     |           | ns       |

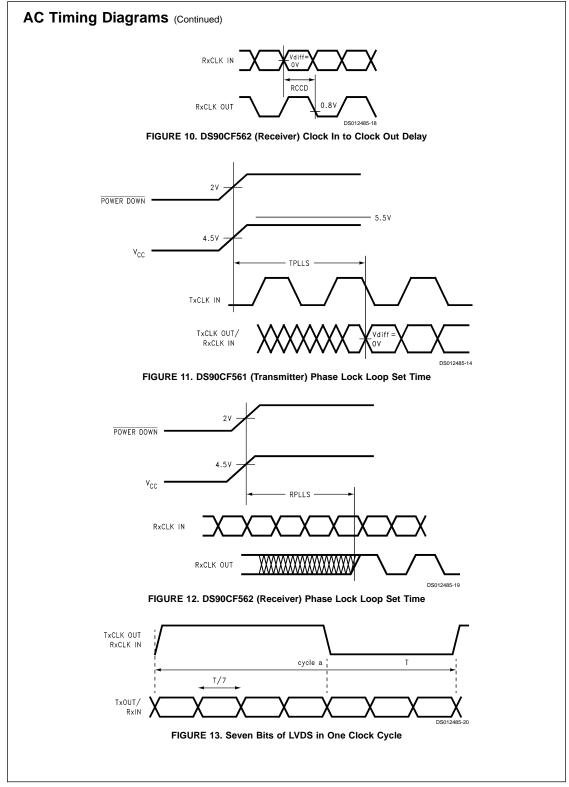

| RCCD                  | RxCLK IN to RxCLK OUT Delay @ 25°C,                                                                                                                                                                                                                                                 | 0 MHz 6.5<br>7.6 |     | 11.9      | ns<br>ns |

| ROOD                  | $V_{\rm CC} = 5.0V$ (Figure 10)                                                                                                                                                                                                                                                     | 7.0              |     | 11.5      | 113      |

| RPLLS                 | Receiver Phase Lock Loop Set ( <i>Figure 12</i> )                                                                                                                                                                                                                                   |                  |     | 10        | ms       |

| RPDD                  | Receiver Powerdown Delay ( <i>Figure 16</i> )                                                                                                                                                                                                                                       |                  |     | 1         | μs       |

| and the s<br>RSKM ≥ o | Receiver Skew Margin is defined as the valid data sampling region at the receiver inputs. This margin ta<br>ietup and hold time (internal data sampling window), allowing LVDS cable skew dependent on type/ler<br>cable skew (type, length) + source clock jitter (cycle to cycle) |                  |     |           | (ICCS)   |

|                       |                                                                                                                                                                                                                                                                                     |                  |     |           |          |

|                       | ODD TxIN/RxOUT                                                                                                                                                                                                                                                                      |                  |     |           |          |

|                       | EVEN TXIN/RXOUT                                                                                                                                                                                                                                                                     |                  |     |           |          |

|                       | FIGURE 1. "Worst Case" Test Pattern                                                                                                                                                                                                                                                 |                  | DS  | 8012485-5 |          |

|                       |                                                                                                                                                                                                                                                                                     |                  |     |           |          |

. .

8

| Pin Name             | I/O | No. | Description                                                                                                                                              |

|----------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxIN                 | 1   | 21  | TTL level input. This includes: 6 Red, 6 Green, 6 Blue, and 3 control lines (FPLINE, FPFRAME, DRDY). (Also referred to as HSYNC, VSYNC and DATA ENABLE.) |

| TxOUT+               | 0   | 3   | Positive LVDS differential data output                                                                                                                   |

| TxOUT–               | 0   | 3   | Negative LVDS differential data output                                                                                                                   |

| FPSHIFT IN           | I   | 1   | TTL level clock input. The falling edge acts as data strobe.                                                                                             |

| TxCLK OUT+           | 0   | 1   | Positive LVDS differential clock output                                                                                                                  |

| TxCLK OUT-           | 0   | 1   | Negative LVDS differential clock output                                                                                                                  |

| PWR DOWN             | I   | 1   | TTL level input. Assertion (low input) TRI-STATES the outputs, ensuring low current at power down.                                                       |

| V <sub>cc</sub>      | I   | 4   | Power supply pins for TTL inputs                                                                                                                         |

| GND                  | I   | 5   | Ground pins for TTL inputs                                                                                                                               |

| PLL V <sub>CC</sub>  | Ι   | 1   | Power supply pin for PLL                                                                                                                                 |

| PLL GND              | Ι   | 2   | Ground pins for PLL                                                                                                                                      |

| LVDS V <sub>CC</sub> | I   | 1   | Power supply pin for LVDS outputs                                                                                                                        |

| LVDS GND             | 1   | 3   | Ground pins for LVDS outputs                                                                                                                             |

## DS90CF562 Pin Description—FPD Link Receiver

| Pin Name             | I/O | No. | Description                                                                                                                                                     |

|----------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxIN+                | Ι   | 3   | Positive LVDS differential data inputs                                                                                                                          |

| RxIN-                | I   | 3   | Negative LVDS differential data inputs                                                                                                                          |

| RxOUT                | 0   | 21  | TTL level data outputs. This includes: 6 Red, 6 Green, 6 Blue, and 3 control lines (FPLINE, FPFRAME, DRDY). (Also referred to as HSYNC, VSYNC and DATA ENABLE.) |

| RxCLK IN+            | Ι   | 1   | Positive LVDS differential clock input                                                                                                                          |

| RxCLK IN-            | Ι   | 1   | Negative LVDS differential clock input                                                                                                                          |

| FPSHIFT OUT          | 0   | 1   | TTL level clock output. The falling edge acts as data strobe.                                                                                                   |

| PWR DOWN             | I   | 1   | TTL level input. Assertion (low input) maintains the receiver outputs in the previous state                                                                     |

| V <sub>cc</sub>      | Ι   | 4   | Power supply pins for TTL outputs                                                                                                                               |

| GND                  | Ι   | 5   | Ground pins for TTL outputs                                                                                                                                     |

| PLL V <sub>CC</sub>  | Ι   | 1   | Power supply for PLL                                                                                                                                            |

| PLL GND              | Ι   | 2   | Ground pin for PLL                                                                                                                                              |

| LVDS V <sub>CC</sub> | Ι   | 1   | Power supply pin for LVDS inputs                                                                                                                                |

| LVDS GND             | 1   | 3   | Ground pins for LVDS inputs                                                                                                                                     |