ABOV SEMICONDUCTOR Co., Ltd. 8-BIT MICROCONTROLLERS

# MC96F6432

# User's Manual (Ver. 1.2)

# **REVISION HISTORY**

## VERSION 0.0 (January 14, 2011)

#### VERSION 1.0 (June 27, 2011)

Change 'Typ/Max' to "LVR/LVI level" in LVR/LVI electrical characteristics.

Change '600/1200/2000 k $\Omega$  (Min/Typ/Max)' to "RX1" in DC electrical characteristics.

Change '3/6/9 kHz (Min/Typ/Max)' to "f<sub>WDTRC</sub>" in INTERNAL WATCH-DOG RC OSCILLATION characteristics.

Remove WDTRC Current Max value at INTERNAL WATCH-DOG RC OSCILLATION characteristics.

Add '1.0 µA (Typ)' to "I<sub>WDTRC</sub>" in INTERNAL WATCH-DOG RC OSCILLATION characteristics.

Add NOTE at 'T4CK[3:0] bits description'.

Change 'cleared by software(S/W)' in TIMER 3/4 BIOCK DIAGRAM.

Deleted AN15 Function in 12-bit A/D converter.

Added VDD18 Function in 12-bit A/D converter

Change '2500/5000/10000 k $\Omega$  (Min/Typ/Max)' to "RX2" in DC electrical characteristics.

Change '8.0/12.0 uA (Typ/Max) to "Current consumption(one of two)" in LVR/LVI characteristics.

Change '10.0/15.0 uA (Typ/Max) to "Current consumption(both)" in LVR/LVI characteristics.

Change '±3 (Max)' to "ILE" in ADC characteristics.

EXTRF/LVRF initial value changed '0' to 'unknown'.

Add NOTE 3 at LVRF description.

#### VERSION 1.1 (July 14, 2011)

Added AN15 Function in 12-bit A/D converter.

Deleted VDD18 Function in 12-bit A/D converter

Change '2/5/10 kHz (Min/Typ/Max)' to "f<sub>WDTRC</sub>" in INTERNAL WATCH-DOG RC OSCILLATION characteristics.

Change temperature condition of HIGH FREQUENCY INTERNAL RC OSCILLATOR characteristics.

#### VERSION 1.2 (July 20, 2011) This book

The MC96F6232M device name is changed 'MC96F6232M' to 'MC96F6332M'.

#### Version 1.2 Published by FAE Team ©2011 ABOV Semiconductor Co.,Ltd. All rights reserved.

Additional information of this manual may be served by ABOV Semiconductor offices in Korea or Distributors.

ABOV Semiconductor reserves the right to make changes to any information here in at any time without notice.

The information, diagrams and other data in this manual are correct and reliable; however, ABOV Semiconductor is in no way responsible for any violations of patents or other rights of the third party generated by the use of this manual.

# **Table of Contents**

| 1. | Overview                                                        | . 11 |

|----|-----------------------------------------------------------------|------|

|    | 1.1 Description                                                 |      |

|    | 1.2 Features                                                    | . 12 |

|    | 1.3 Ordering Information                                        | . 13 |

|    | 1.4 Development Tools                                           | . 14 |

| 2. | Block Diagram                                                   | . 16 |

| 3. | Pin Assignment                                                  | . 17 |

| 4. | Package Diagram                                                 | . 19 |

| 5. | Pin Description                                                 | . 22 |

| 6. | Port Structures                                                 | . 27 |

|    | 6.1 General Purpose I/O Port                                    | . 27 |

|    | 6.2 External Interrupt I/O Port                                 | . 28 |

| 7. | Electrical Characteristics                                      |      |

|    | 7.1 Absolute Maximum Ratings                                    | . 29 |

|    | 7.2 Recommended Operating Conditions                            | . 29 |

|    | 7.3 A/D Converter Characteristics                               | . 30 |

|    | 7.4 Power-On Reset Characteristics                              | . 30 |

|    | 7.5 Low Voltage Reset and Low Voltage Indicator Characteristics | . 31 |

|    | 7.6 High Internal RC Oscillator Characteristics                 | . 32 |

|    | 7.7 Internal Watch-Dog Timer RC Oscillator Characteristics      | . 32 |

|    | 7.8 LCD Voltage Characteristics                                 | . 33 |

|    | 7.9 DC Characteristics                                          | . 34 |

|    | 7.10 AC Characteristics                                         | . 36 |

|    | 7.11 SPI0/1/2 Characteristics                                   | . 37 |

|    | 7.12 UART0/1 Characteristics                                    | . 38 |

|    | 7.13 I2C0/1 Characteristics                                     | . 39 |

|    | 7.14 Data Retention Voltage in Stop Mode                        | . 40 |

|    | 7.15 Internal Flash Rom Characteristics                         | . 41 |

|    | 7.16 Input/Output Capacitance                                   | . 41 |

|    | 7.17 Main Clock Oscillator Characteristics                      | . 42 |

|    | 7.18 Sub Clock Oscillator Characteristics                       | . 43 |

|    | 7.19 Main Oscillation Stabilization Characteristics             | . 44 |

|    | 7.20 Sub Oscillation Characteristics                            | . 44 |

|    | 7.21 Operating Voltage Range                                    | . 45 |

|    | 7.22 Recommended Circuit and Layout                             |      |

|    | 7.23 Typical Characteristics                                    | . 47 |

|    |                                                                 |      |

| 8. Memory                                             |                        |

|-------------------------------------------------------|------------------------|

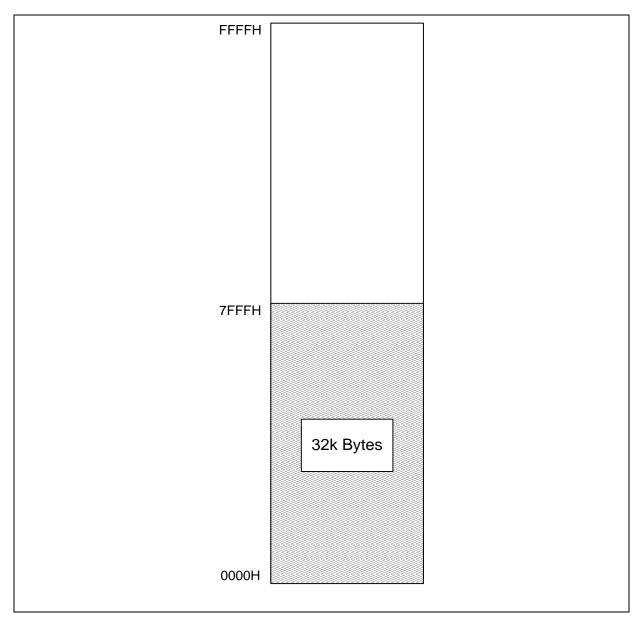

| 8.1 Program Memory                                    |                        |

| 8.2 Data Memory                                       |                        |

| 8.3 XRAM Memory                                       | 54                     |

| 8.4 SFR Map                                           |                        |

| ). I/O Ports                                          |                        |

| 9.1 I/O Ports                                         | 64                     |

| 9.2 Port Register                                     |                        |

| 9.3 P0 Port                                           |                        |

| 9.4 P1 Port                                           |                        |

| 9.5 P2 Port                                           |                        |

| 9.6 P3 Port                                           | 71                     |

| 9.7 P4 Port                                           |                        |

| 9.8 P5 Port                                           |                        |

| 9.9 Port Function                                     | 74                     |

| 0. Interrupt Controller                               |                        |

| 10.1 Overview                                         |                        |

| 10.2 External Interrupt                               |                        |

| 10.3 Block Diagram                                    |                        |

| 10.4 Interrupt Vector Table                           |                        |

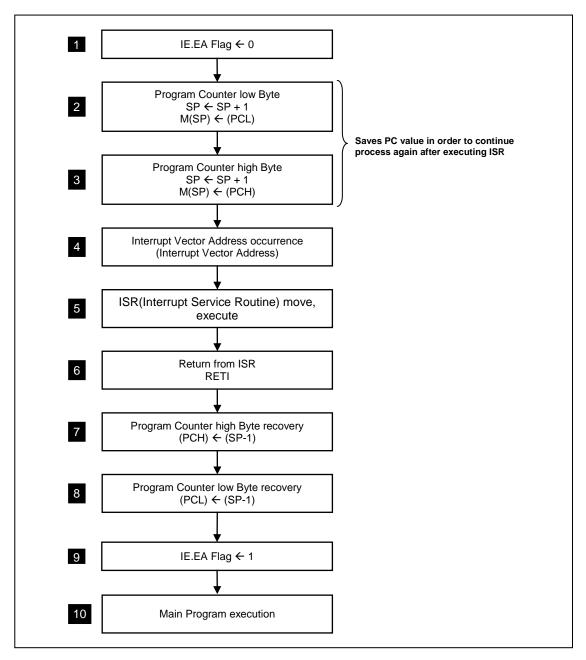

| 10.5 Interrupt Sequence                               |                        |

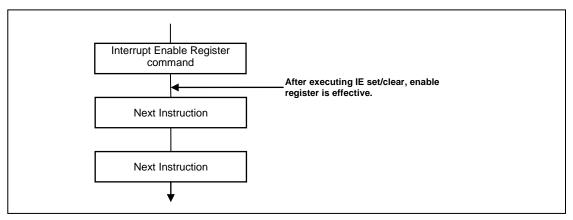

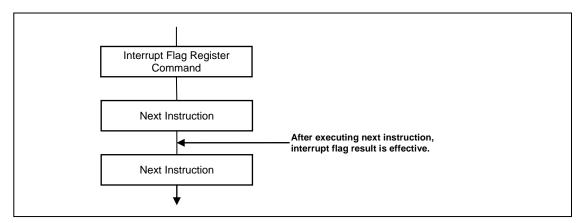

| 10.6 Effective Timing after Controlling Interrupt Bit |                        |

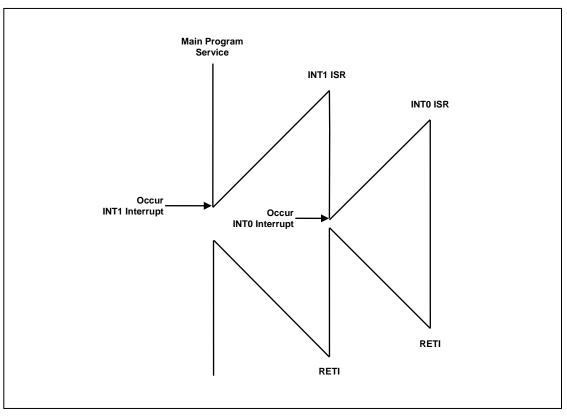

| 10.7 Multi Interrupt                                  |                        |

| 10.8 Interrupt Enable Accept Timing                   |                        |

| 10.9 Interrupt Service Routine Address                |                        |

| 10.10 Saving/Restore General-Purpose Registers        |                        |

| 10.10 Saving Rescore General-1 upose Registers        |                        |

| 10.12 Interrupt Register Overview                     |                        |

| 10.12 Interrupt Register Description                  |                        |

| 1. Peripheral Hardware                                |                        |

| -                                                     |                        |

| 11.1 Clock Generator                                  |                        |

| 11.2 Basic Interval Timer                             |                        |

| 11.3 Watch Dog Timer                                  |                        |

| 11.4 Watch Timer                                      |                        |

| 11.5 Timer 0                                          |                        |

| 11.6 Timer 1                                          |                        |

| 11.7 Timer 2                                          |                        |

| 11.8 Timer 3, 4                                       |                        |

| 11.9 Buzzer Driver                                    |                        |

| 11.10 SPI 2                                           |                        |

| 11.11 12-Bit A/D Converter                            |                        |

| 11.12 USI0 (UART + SPI + I2C)                         |                        |

| 11.13 USI1 (UART + SPI + I2C)                         |                        |

| 11.15 LCD Driver                                      |                        |

| 2. Power Down Operation                               |                        |

| 12.1 Overview                                         |                        |

| 12.2 Peripheral Operation in IDLE/STOP Mode           |                        |

| 12.3 IDLE Mode                                        |                        |

| 12.4 STOP Mode                                        |                        |

| 12.5 Release Operation of STOP Mode                   |                        |

| 13. RESET                                             |                        |

| 13.1 Overview                                         |                        |

| 13.2 Reset Source                                     |                        |

| 4                                                     | July 20, 2011 Ver. 1.2 |

| 13.3 RESET Block Diagram          |     |

|-----------------------------------|-----|

| 13.4 RESET Noise Canceller        |     |

| 13.5 Power on RESET               | 278 |

| 13.6 External RESETB Input        |     |

| 13.7 Brown Out Detector Processor |     |

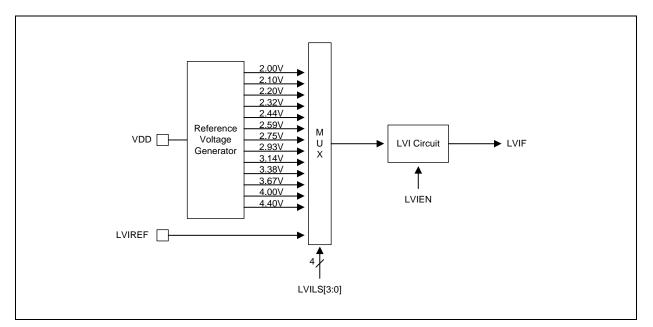

| 13.8 LVI Block Diagram            |     |

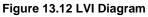

| 14. On-chip Debug System          |     |

| 14.1 Overview                     |     |

| 14.2 Two-Pin External Interface   |     |

| 15. Flash Memory                  | 293 |

| 15.1 Overview                     | 293 |

| 16. Configure Option              |     |

| 16.1 Configure Option Control     |     |

| 17. APPENDIX                      |     |

# **List of Figures**

| Figure 1.1 OCD Debugger and Pin Description                        | 14 |

|--------------------------------------------------------------------|----|

| Figure 1.2 PGMplusUSB (Single Writer)                              | 15 |

| Figure 1.3 StandAlone PGMplus (Single Writer)                      | 15 |

| Figure 1.4 StandAlone Gang8 (for Mass Production)                  | 15 |

| Figure 2.1 Block Diagram                                           | 16 |

| Figure 3.1 MC96F6432Q 44MQFP-1010 Pin Assignment                   | 17 |

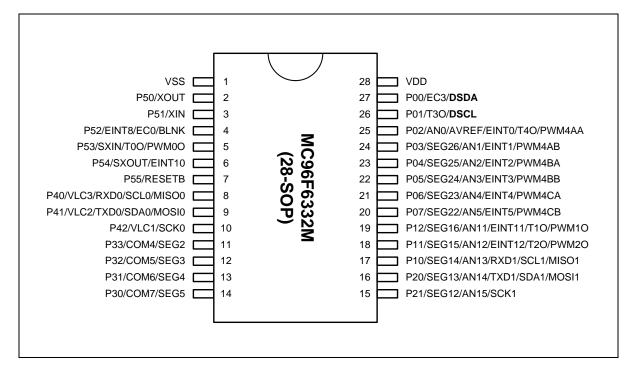

| Figure 3.2 MC96F6332D 32SOP Pin Assignment                         | 18 |

| Figure 3.3 MC96F6332M 28SOP Pin Assignment                         | 18 |

| Figure 4.1 44-Pin MQFP Package                                     | 19 |

| Figure 4.2 32-Pin SOP Package                                      | 20 |

| Figure 4.3 28-Pin SOP Package                                      | 21 |

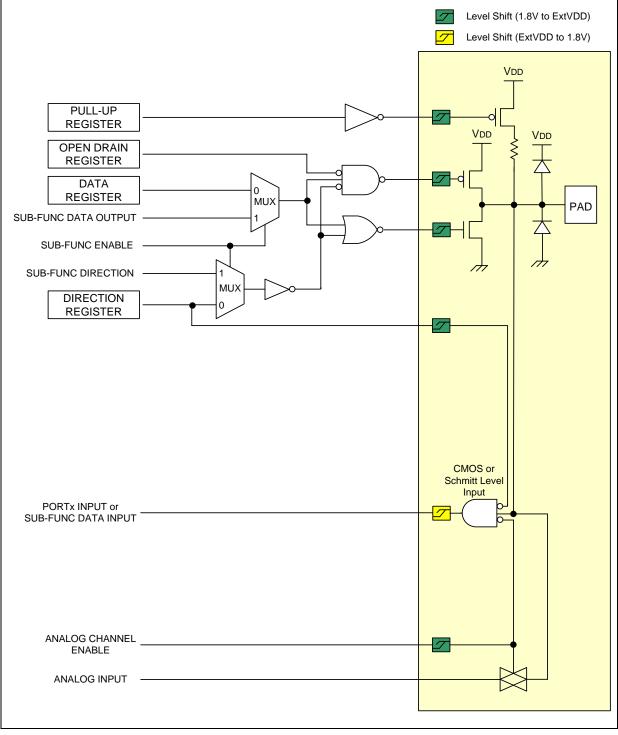

| Figure 6.1 General Purpose I/O Port                                | 27 |

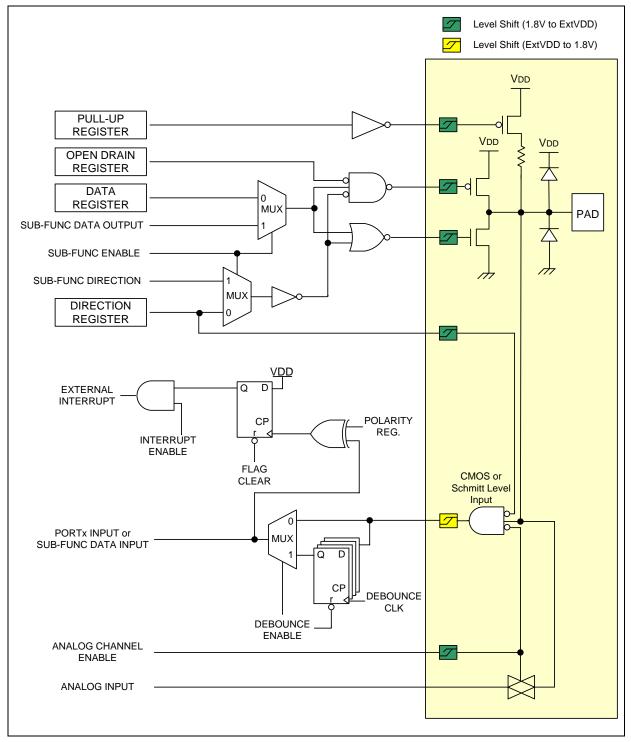

| Figure 6.2 External Interrupt I/O Port                             |    |

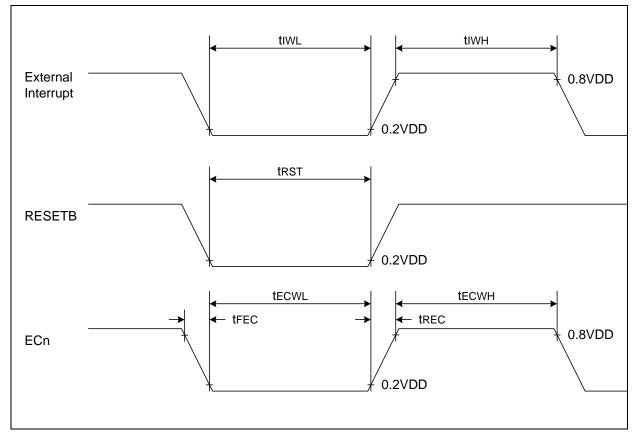

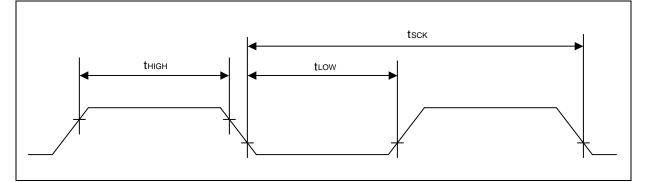

| Figure 7.1 AC Timing                                               | 36 |

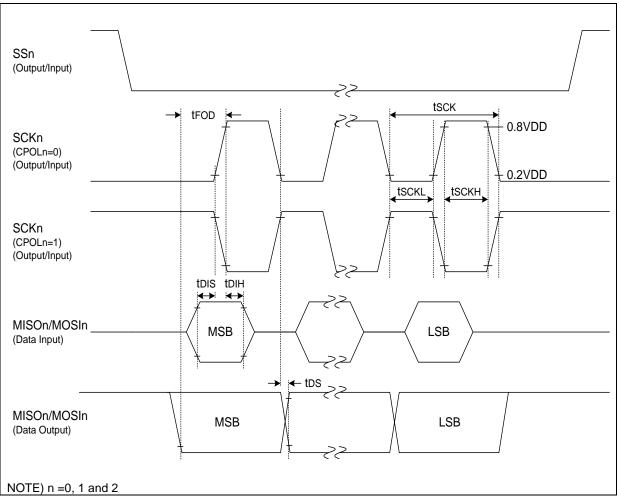

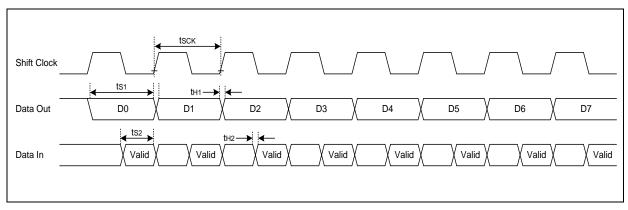

| Figure 7.2 SPI0/1/2 Timing                                         | 37 |

| Figure 7.3 Waveform for UART0/1 Timing Characteristics             | 38 |

| Figure 7.4 Timing Waveform for the UART0/1 Module                  |    |

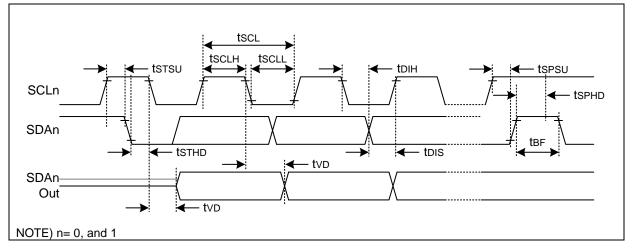

| Figure 7.5 I2C0/1 Timing                                           | 39 |

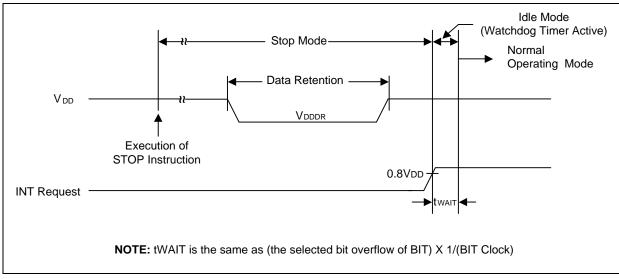

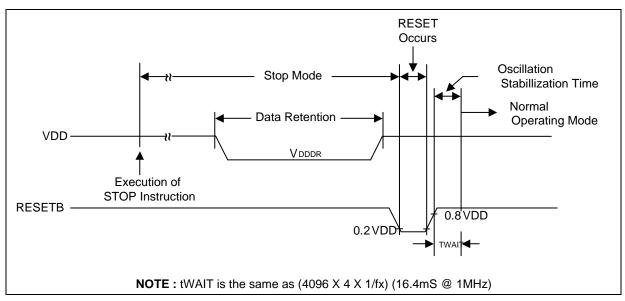

| Figure 7.6 Stop Mode Release Timing when Initiated by an Interrupt | 40 |

| Figure 7.7 Stop Mode Release Timing when Initiated by RESETB       | 40 |

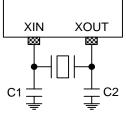

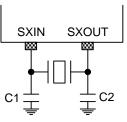

| Figure 7.8 Crystal/Ceramic Oscillator                              | 42 |

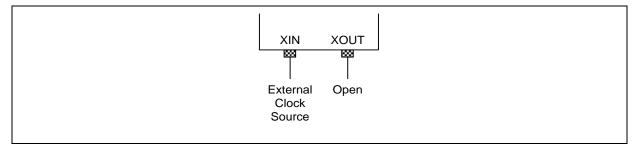

| Figure 7.9 External Clock                                          | 42 |

| Figure 7.10 Crystal Oscillator                                     | 43 |

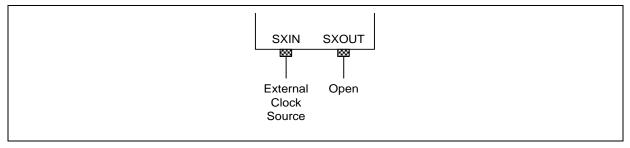

| Figure 7.11 External Clock                                         | 43 |

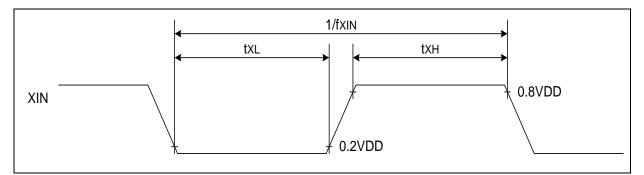

| Figure 7.12 Clock Timing Measurement at XIN                        | 44 |

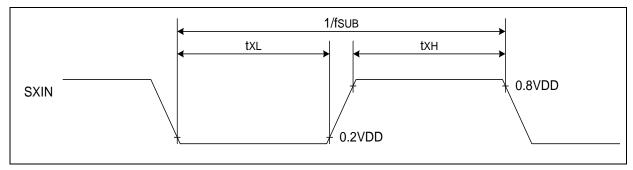

| Figure 7.13 Clock Timing Measurement at SXIN                       | 44 |

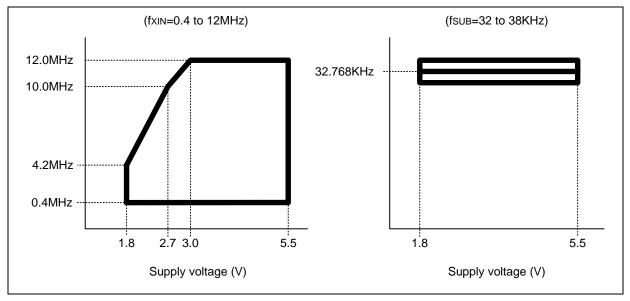

| Figure 7.14 Operating Voltage Range                                | 45 |

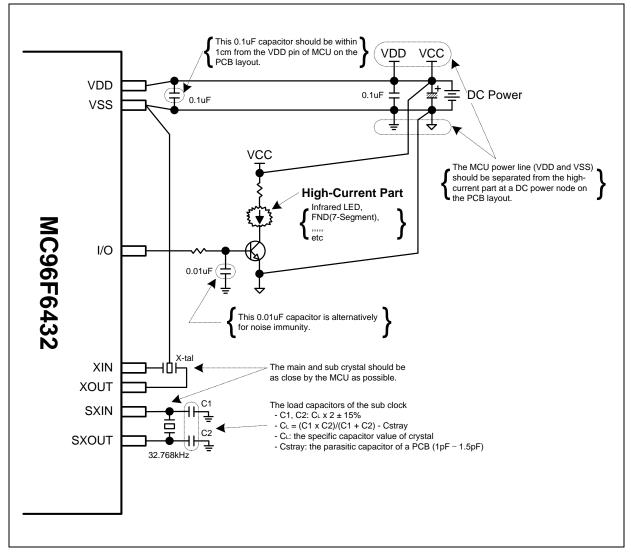

| Figure 7.15 Recommended Circuit and Layout                         | 46 |

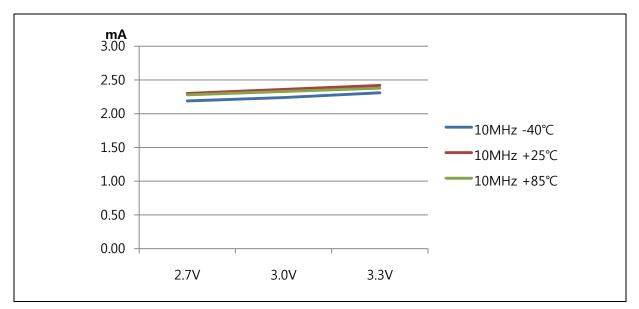

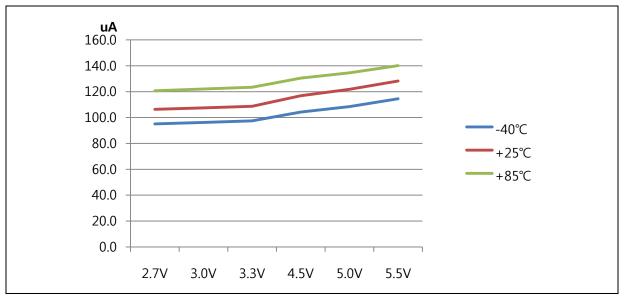

| Figure 7.16 RUN (IDD1 ) Current                                    | 47 |

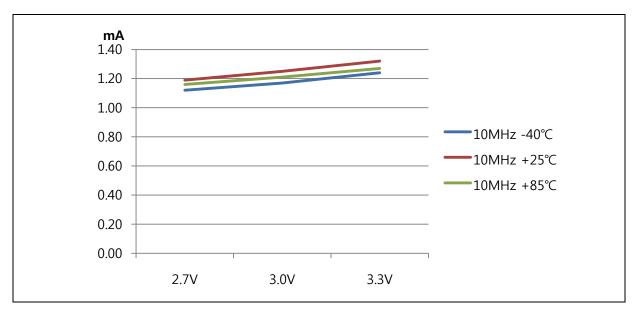

| Figure 7.17 IDLE (IDD2) Current                                    | 47 |

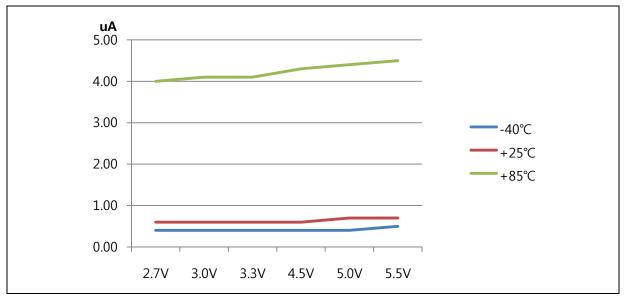

| Figure 7.18 SUB RUN (IDD3) Current                                 | 48 |

| Figure 7.19 SUB IDLE (IDD4) Current                                | 48 |

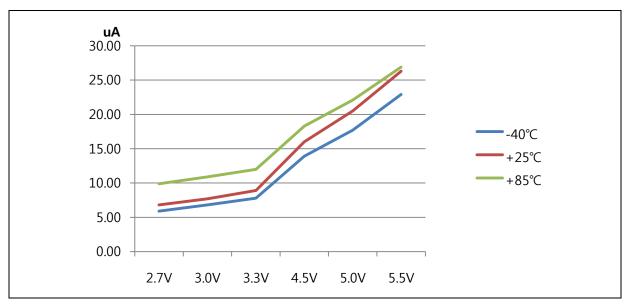

| Figure 7.20 STOP (IDD5) Current                                                      | 49  |

|--------------------------------------------------------------------------------------|-----|

| Figure 8.1 Program Memory                                                            | 51  |

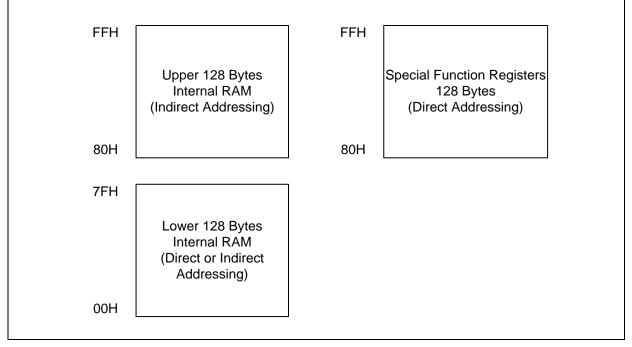

| Figure 8.2 Data Memory Map                                                           | 52  |

| Figure 8.3 Lower 128 Bytes RAM                                                       | 53  |

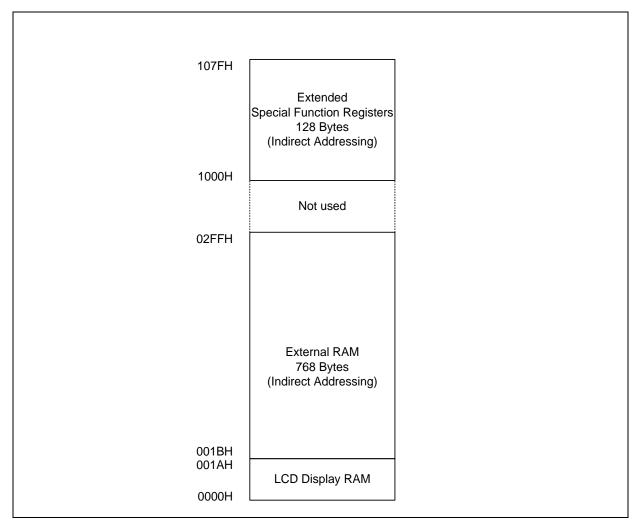

| Figure 8.4 XDATA Memory Area                                                         | 54  |

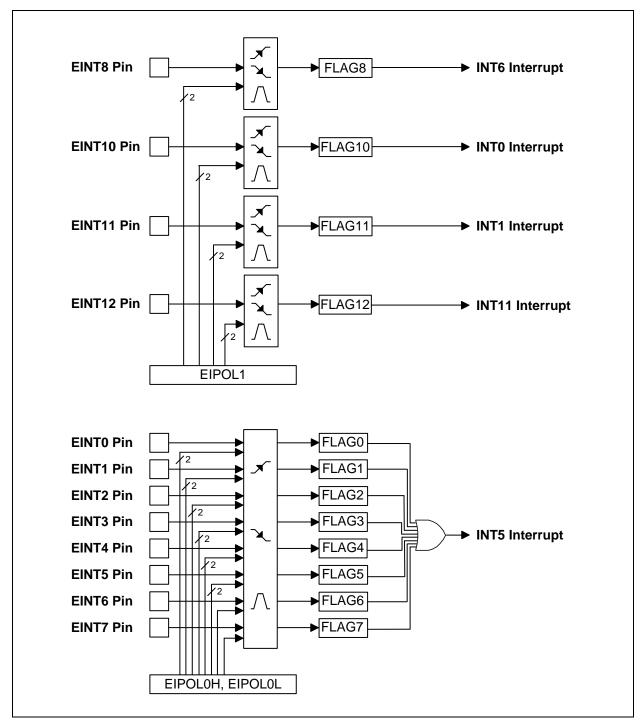

| Figure 10.1 External Interrupt Description                                           | 84  |

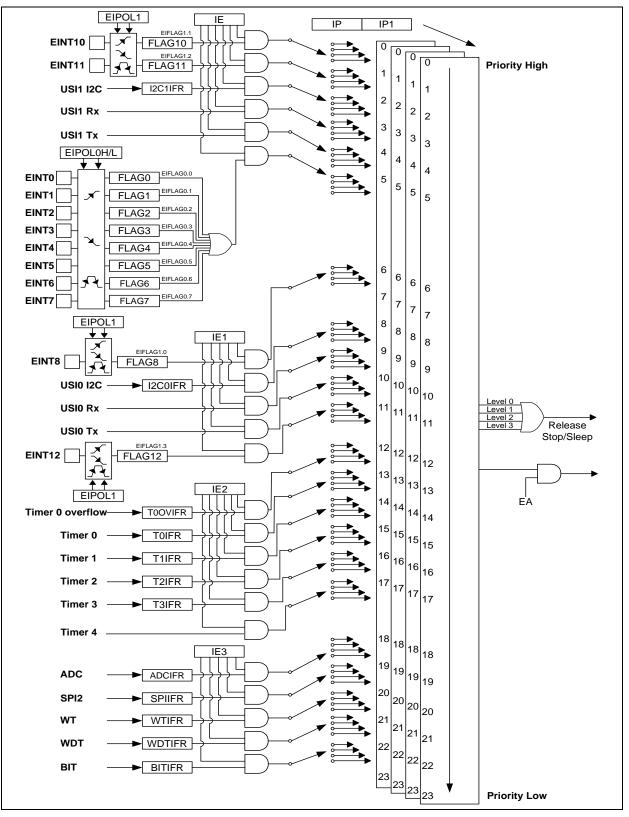

| Figure 10.2 Block Diagram of Interrupt                                               | 85  |

| Figure 10.3 Interrupt Vector Address Table                                           | 87  |

| Figure 10.4 Effective Timing of Interrupt Enable Register                            | 88  |

| Figure 10.5 Effective Timing of Interrupt Flag Register                              | 88  |

| Figure 10.6 Effective Timing of Interrupt                                            | 89  |

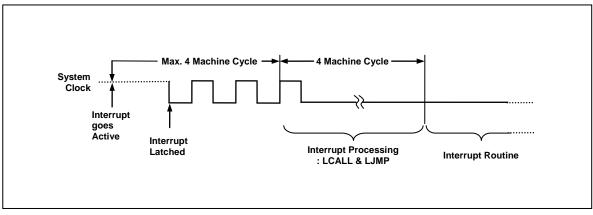

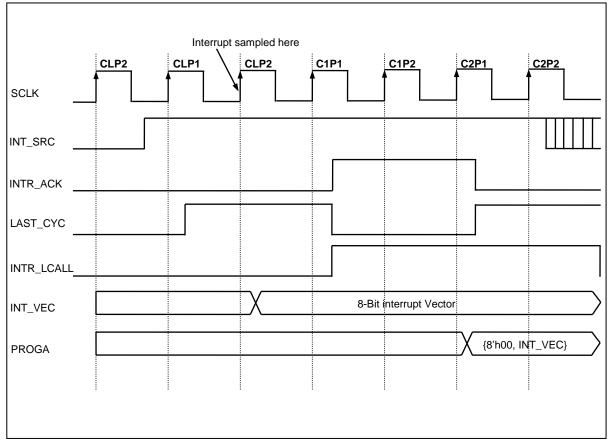

| Figure 10.7 Interrupt Response Timing Diagram                                        | 90  |

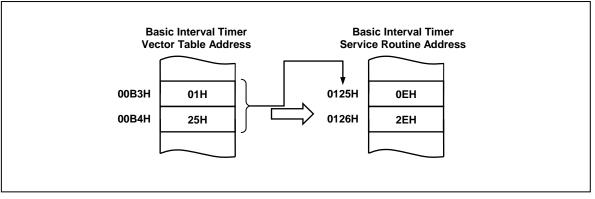

| Figure 10.8 Correspondence between Vector Table Address and the Entry Address of ISP | 90  |

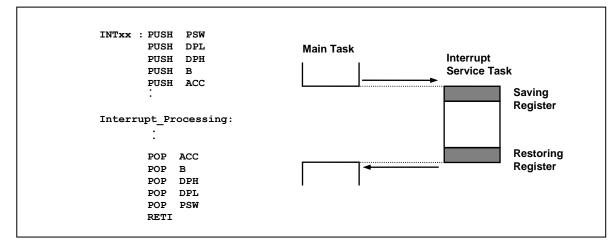

| Figure 10.9 Saving/Restore Process Diagram and Sample Source                         | 90  |

| Figure 10.10 Timing Chart of Interrupt Acceptance and Interrupt Return Instruction   |     |

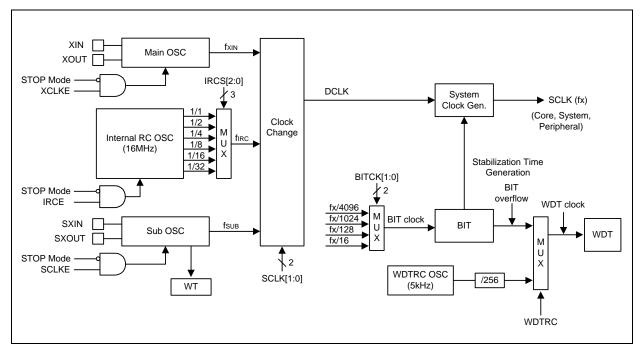

| Figure 11.1 Clock Generator Block Diagram                                            | 100 |

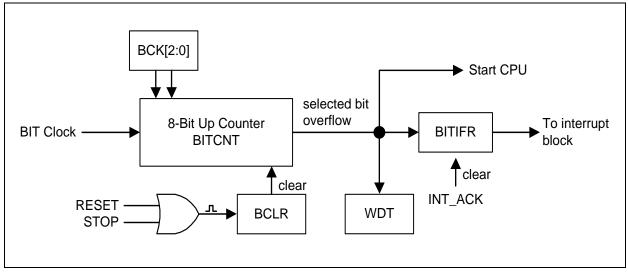

| Figure 11.2 Basic Interval Timer Block Diagram                                       | 103 |

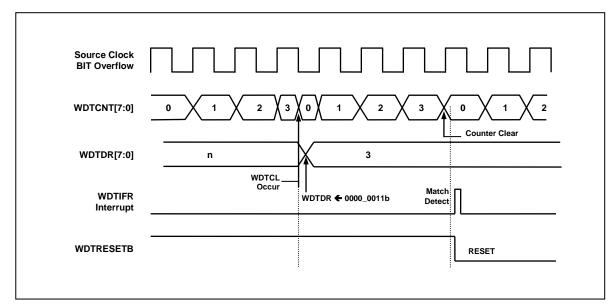

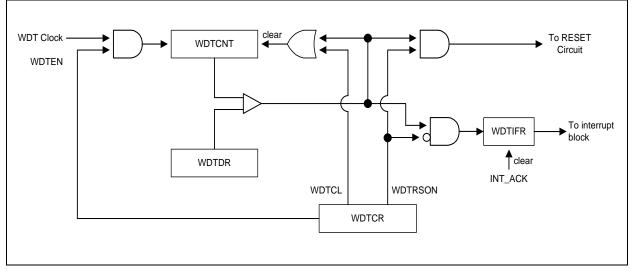

| Figure 11.3 Watch Dog Timer Interrupt Timing Waveform                                | 106 |

| Figure 11.4 Watch Dog Timer Block Diagram                                            | 107 |

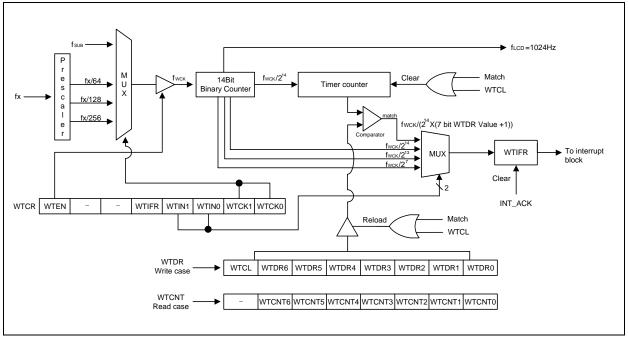

| Figure 11.5 Watch Timer Block Diagram                                                | 109 |

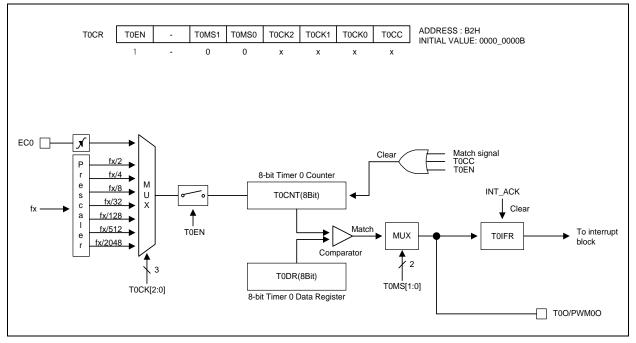

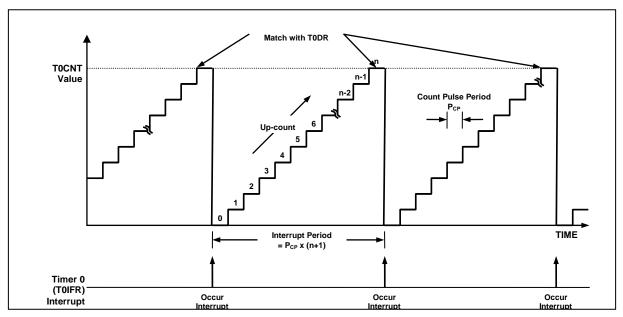

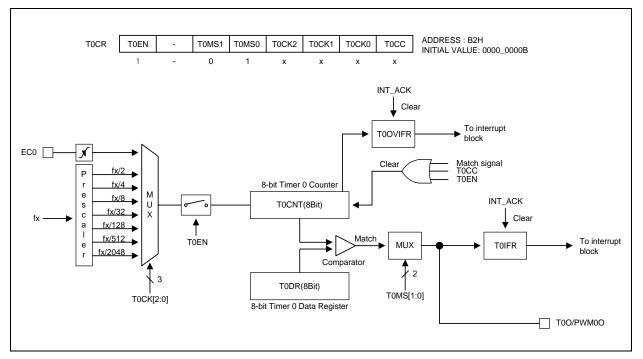

| Figure 11.6 8-Bit Timer/Counter Mode for Timer 0                                     | 113 |

| Figure 11.7 8-Bit Timer/Counter 0 Example                                            | 113 |

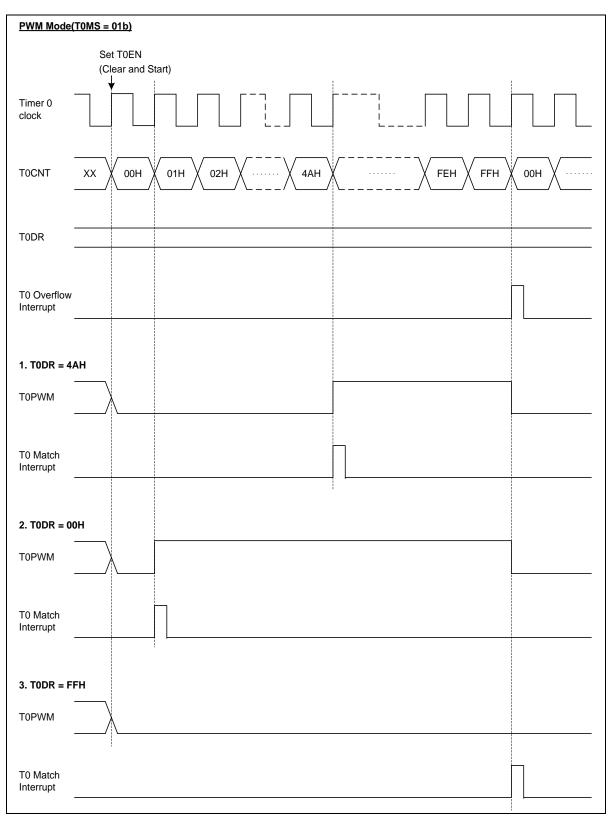

| Figure 11.8 8-Bit PWM Mode for Timer 0                                               | 114 |

| Figure 11.9 PWM Output Waveforms in PWM Mode for Timer 0                             | 115 |

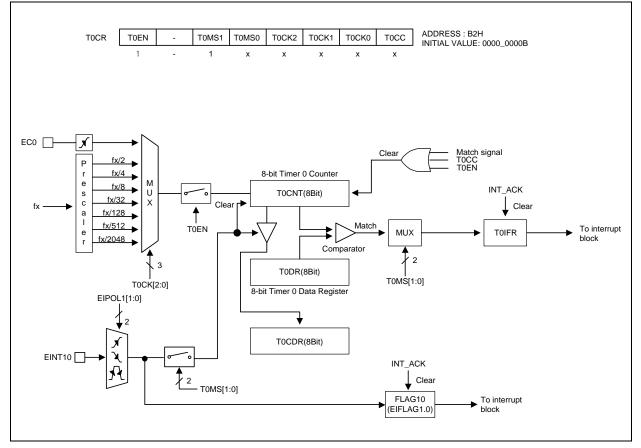

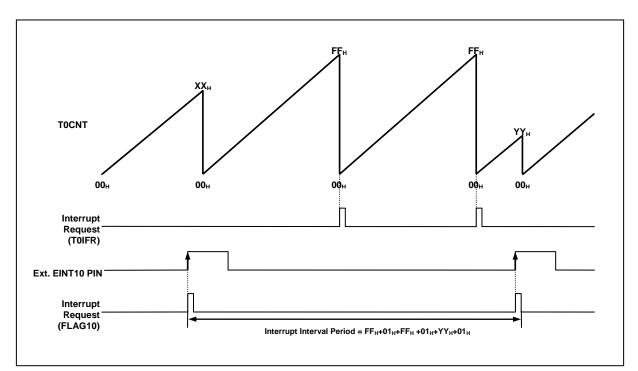

| Figure 11.10 8-Bit Capture Mode for Timer 0                                          | 116 |

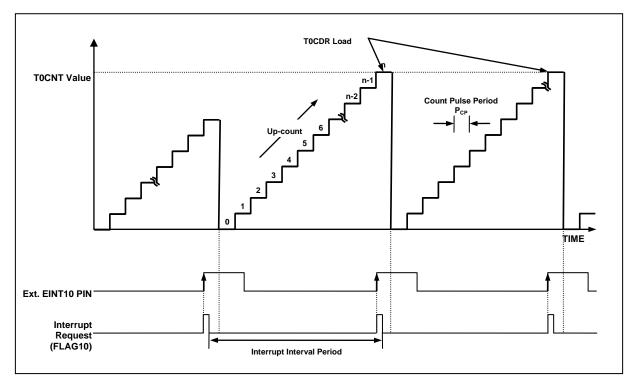

| Figure 11.11 Input Capture Mode Operation for Timer 0                                | 117 |

| Figure 11.12 Express Timer Overflow in Capture Mode                                  | 117 |

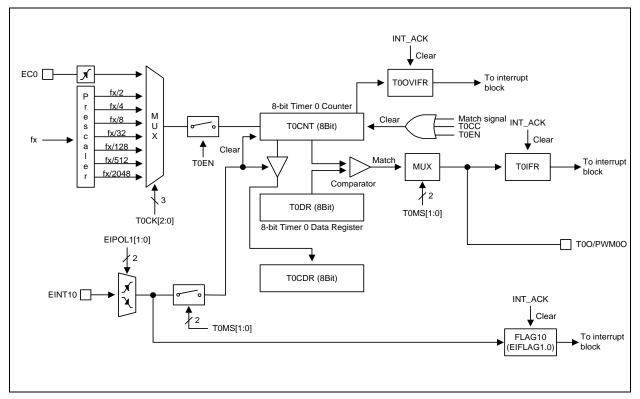

| Figure 11.13 8-Bit Timer 0 Block Diagram                                             | 118 |

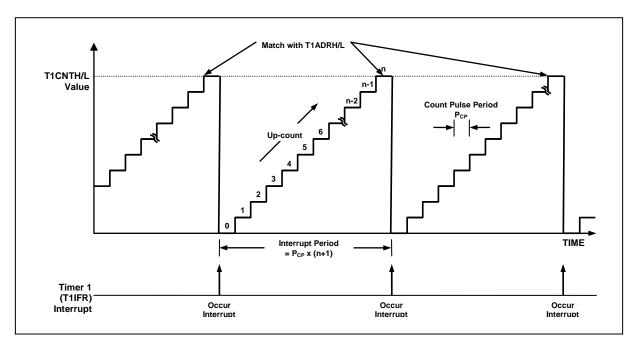

| Figure 11.14 16-Bit Timer/Counter Mode for Timer 1                                   | 122 |

| Figure 11.15 16-Bit Timer/Counter 1 Example                                          | 122 |

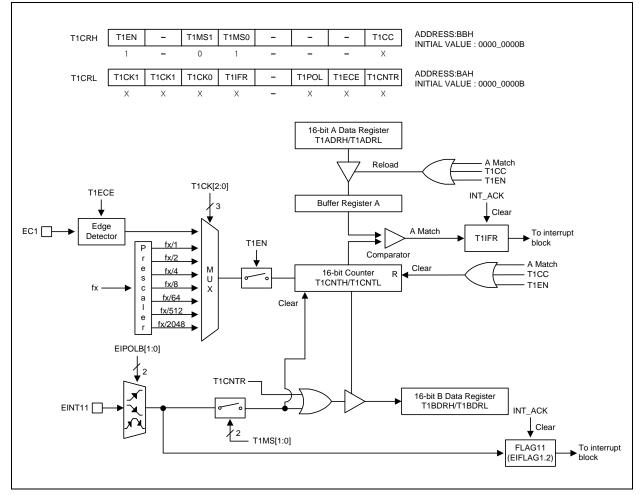

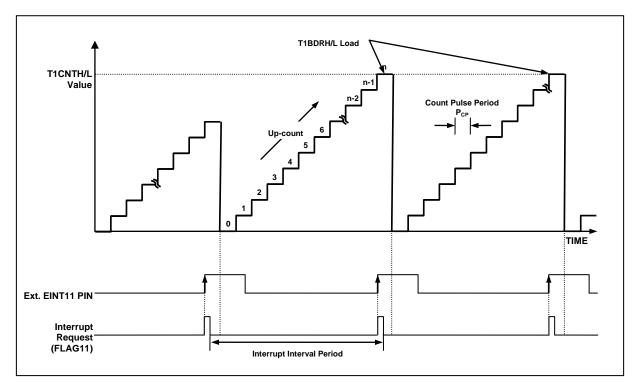

| Figure 11.16 16-Bit Capture Mode for Timer 1                                         |     |

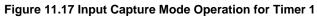

| Figure 11.17 Input Capture Mode Operation for Timer 1                                | 124 |

| Figure 11.18 Express Timer Overflow in Capture Mode                                  |     |

| Figure 11.19 16-Bit PPG Mode for Timer 1                                             |     |

| Figure 11.20 16-Bit PPG Mode Timming chart for Timer 1                               | 126 |

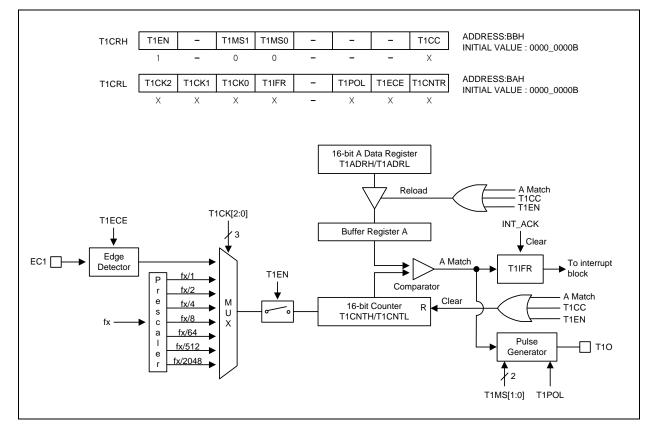

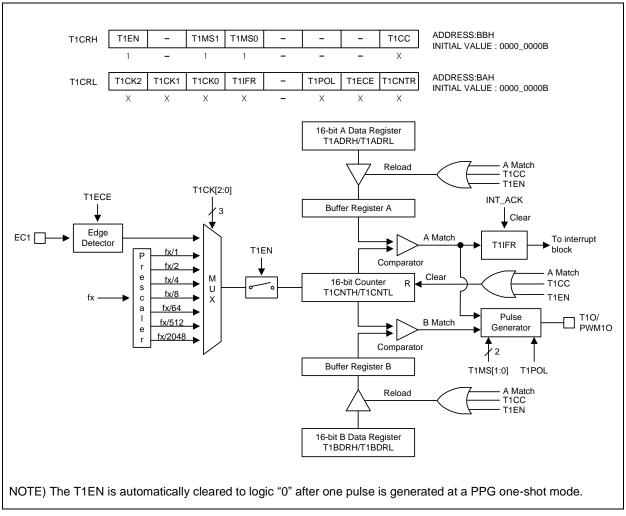

| Figure 11.21 16-Bit Timer/Counter Mode for Timer 1 and Block Diagram                 | 127 |

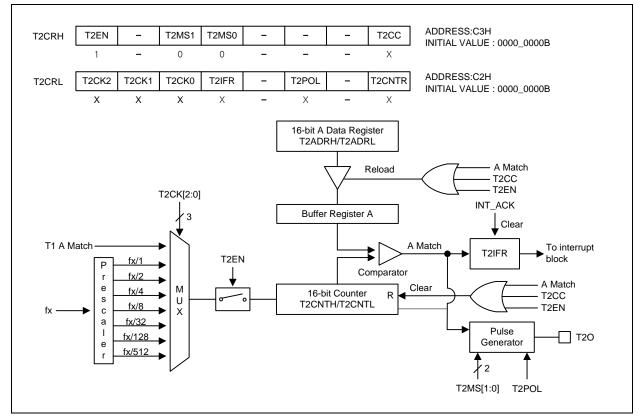

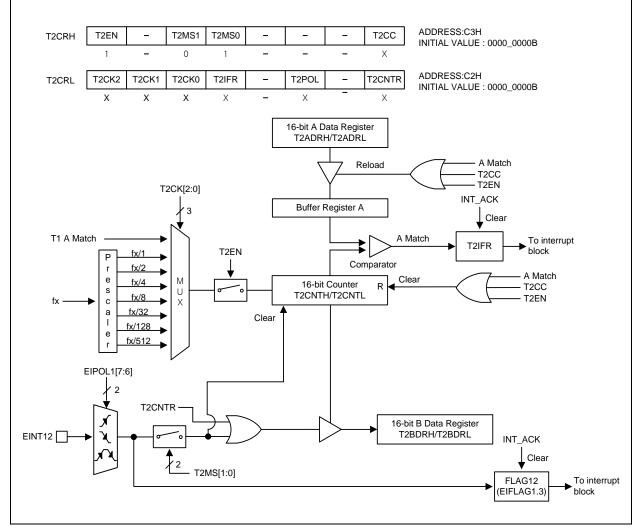

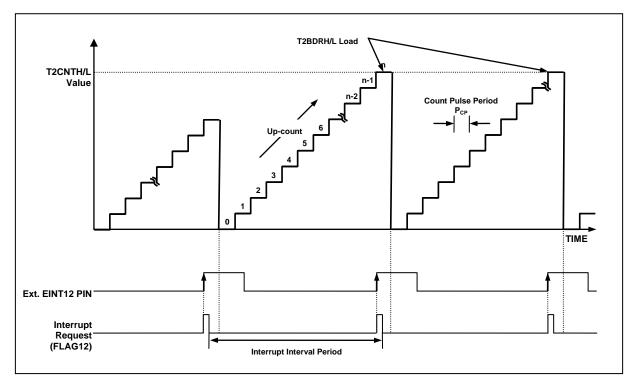

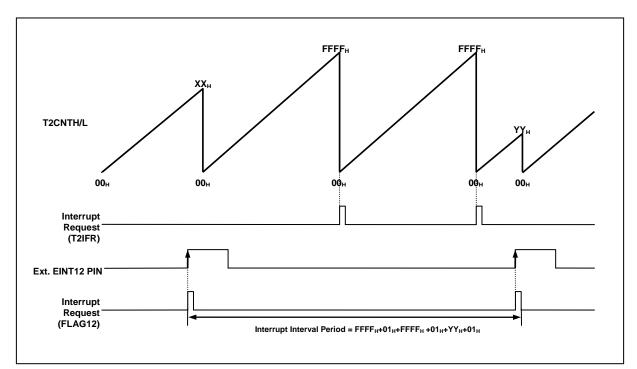

| Figure 11.22 16-Bit Timer/Counter Mode for Timer 2                                   | 132 |

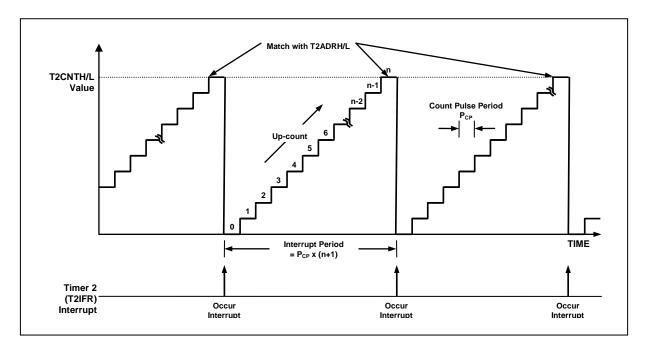

| Figure 11.23 16-Bit Timer/Counter 2 Example                                          |     |

| Figure 11.24 16-Bit Capture Mode for Timer 2                                         |     |

| Figure 11.25 Input Capture Mode Operation for Timer 2                                |     |

| Figure 11.26 Express Timer Overflow in Capture Mode                                  |     |

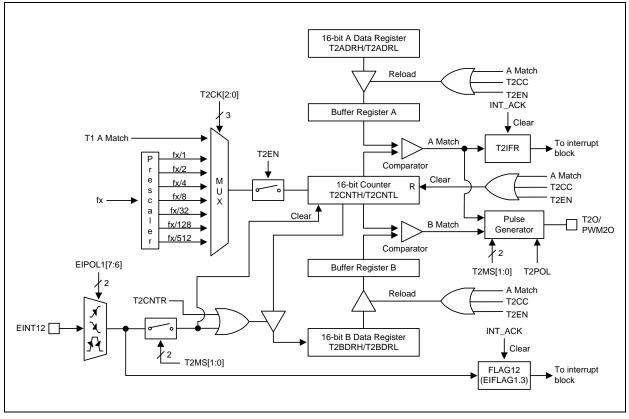

| Figure 11.27 16-Bit PPG Mode for Timer 2                                             |     |

| Figure 11.28 16-Bit PPG Mode Timming chart for Timer 2                               |     |

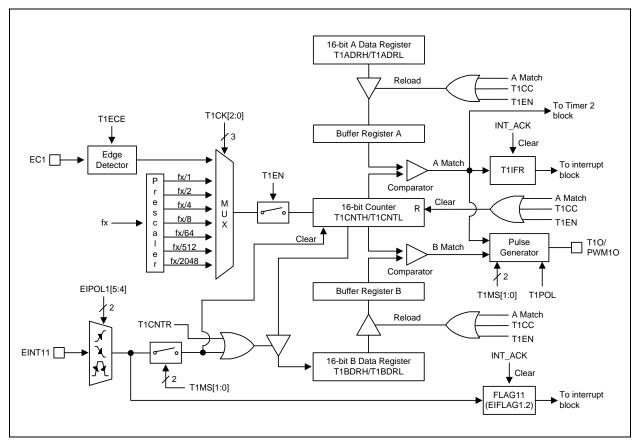

| Figure 11.29 16-Bit Timer/Counter Mode for Timer 2 and Block Diagram                 |     |

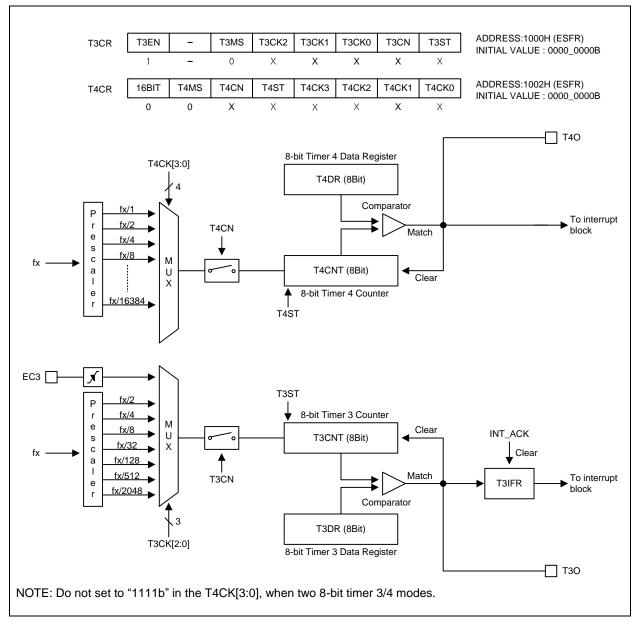

| Figure 11.30 8-Bit Timer/Counter Mode for Timer 3, 4                                 |     |

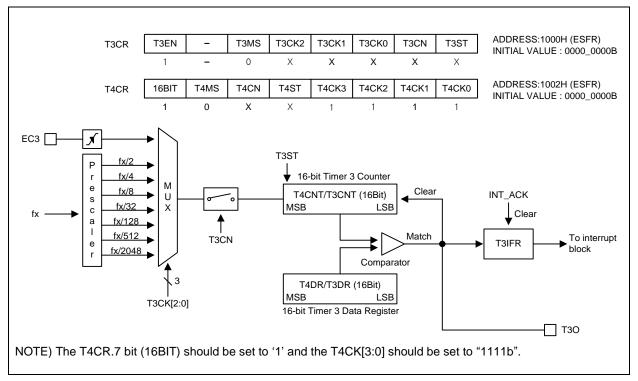

| Figure 11.31 16-Bit Timer/Counter Mode for Timer 3                                   |     |

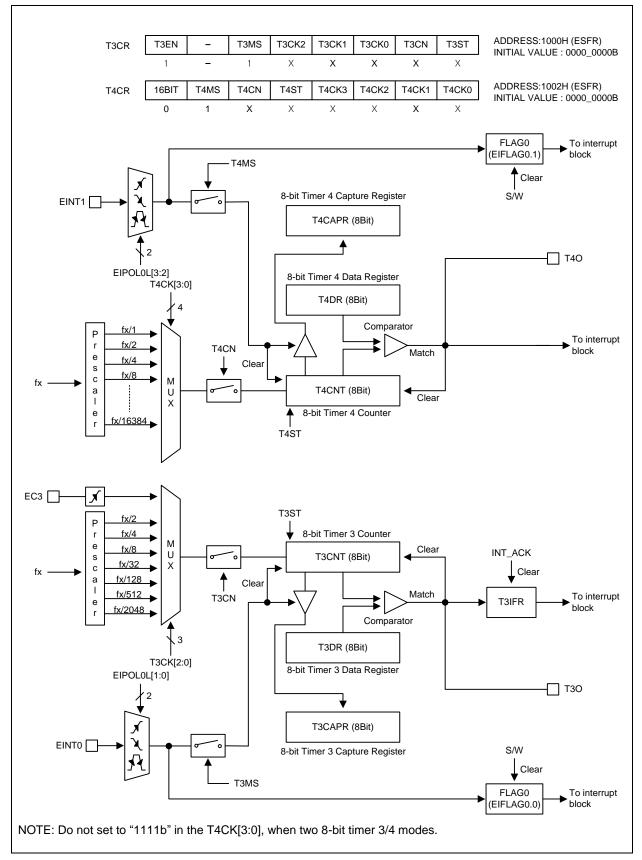

| Figure 11.32 8-Bit Capture Mode for Timer 3, 4                                       |     |

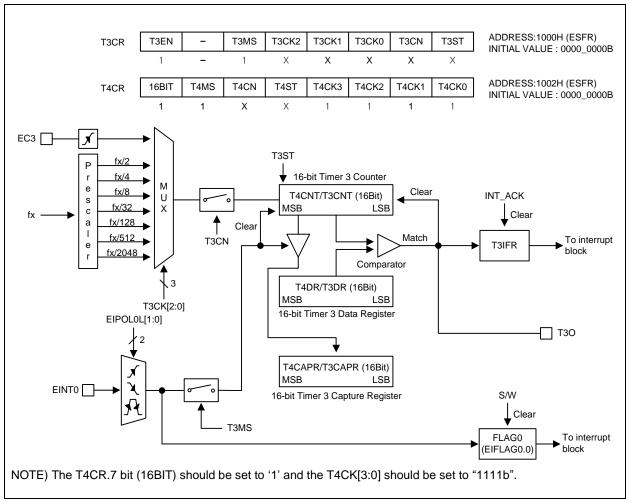

| Figure 11.33 16-Bit Capture Mode for Timer 3                                         |     |

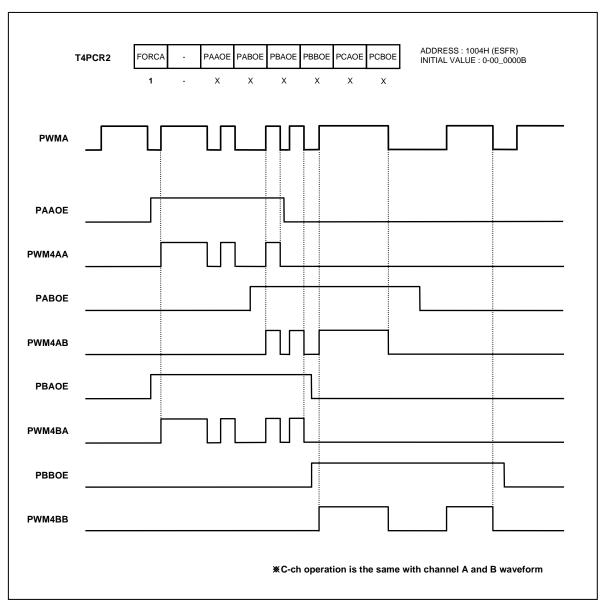

| Figure 11.34 10-Bit PWM Mode (Force 6-ch)                                            | 149 |

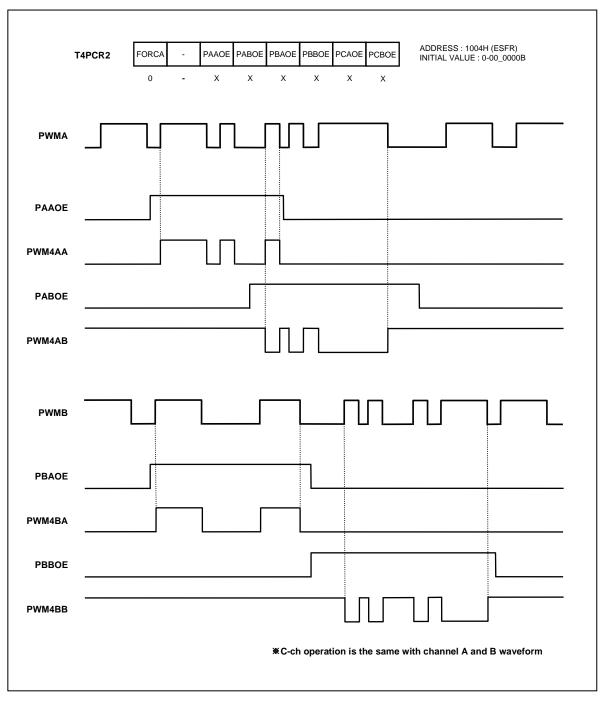

| Figure 11.35 10-Bit PWM Mode (Force All-ch)                                 | 150 |

|-----------------------------------------------------------------------------|-----|

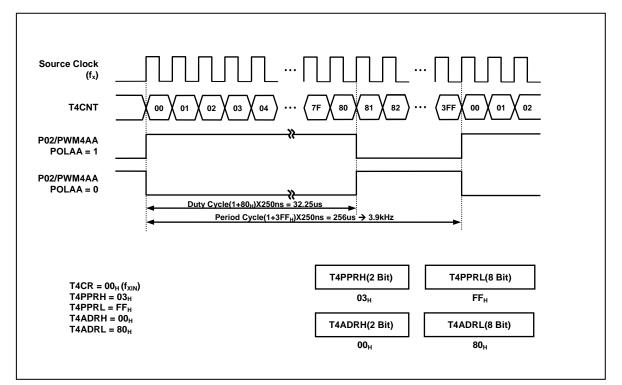

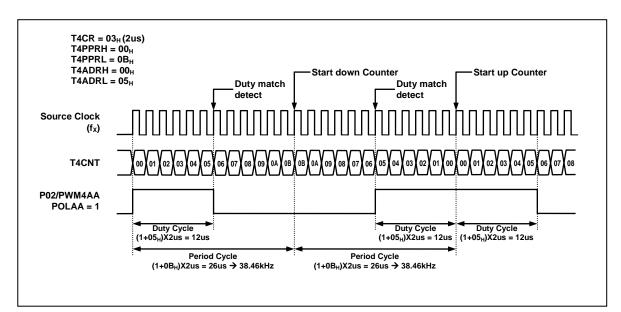

| Figure 11.36 Example of PWM at 4 MHz                                        | 151 |

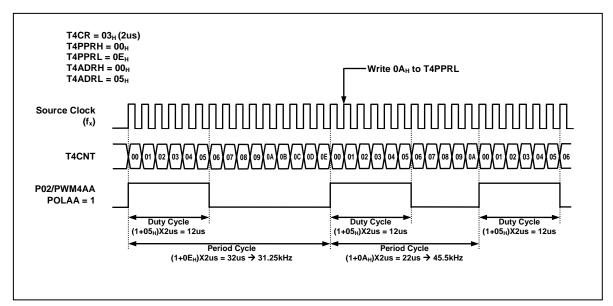

| Figure 11.37 Example of Changing the Period in Absolute Duty Cycle at 4 MHz | 151 |

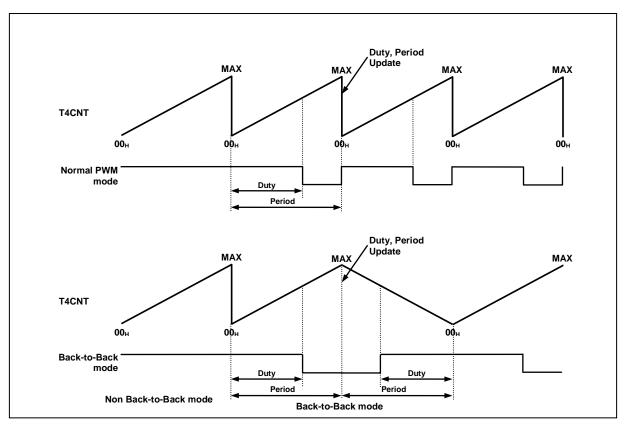

| Figure 11.38 Example of PWM Output Waveform                                 | 152 |

| Figure 11.39 Example of PWM waveform in Back-to-Back mode at 4 MHz          | 152 |

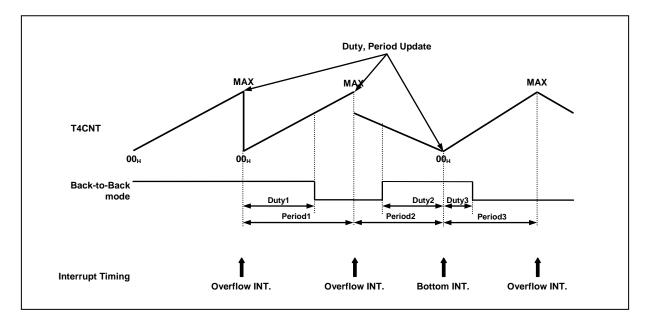

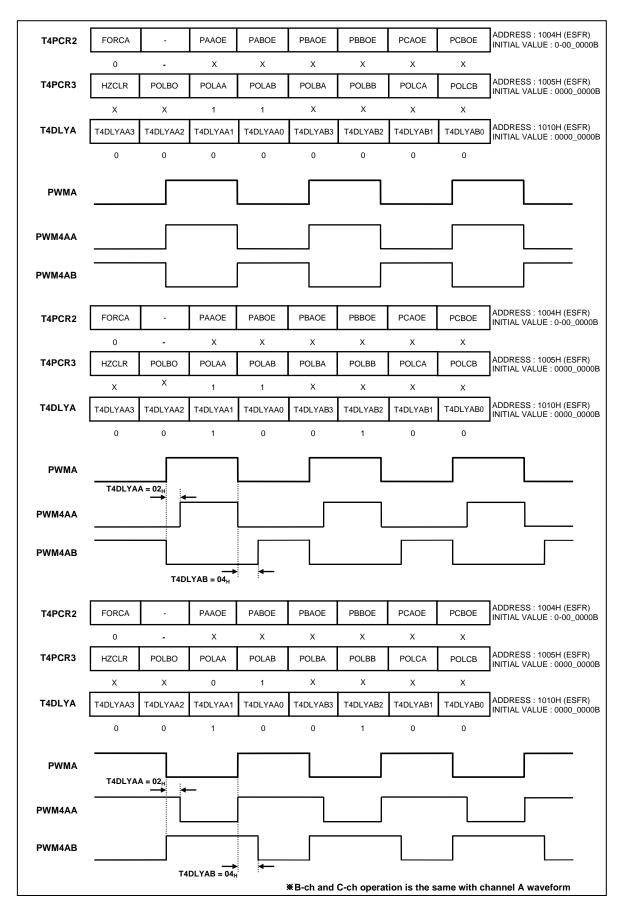

| Figure 11.40 Example of Phase Correction and Frequency correction of PWM    | 153 |

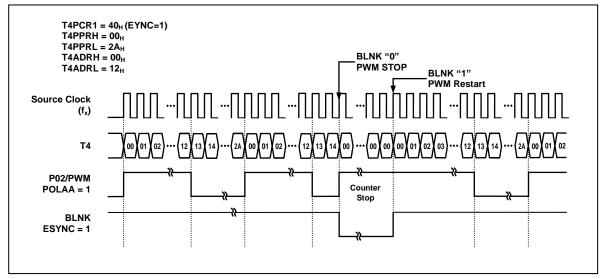

| Figure 11.41 Example of PWM External Synchronization with BLNK Input        | 153 |

| Figure 11.42 Example of Force Drive All Channel with A-ch                   | 154 |

| Figure 11.43 Example of Force Drive 6-ch Mode                               |     |

| Figure 11.44 Example of PWM Delay                                           |     |

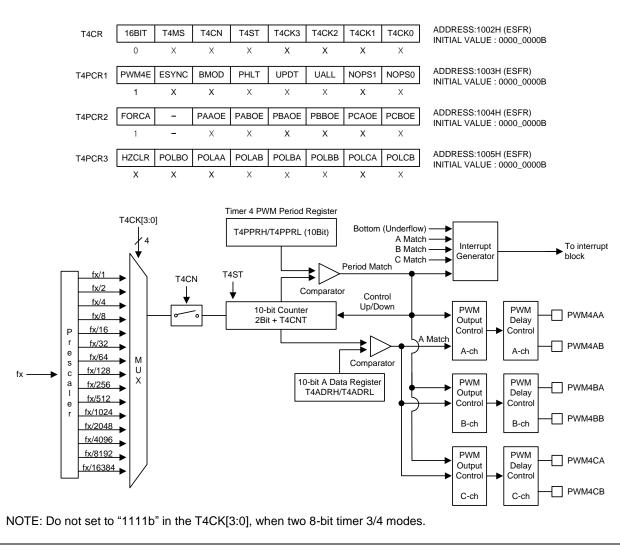

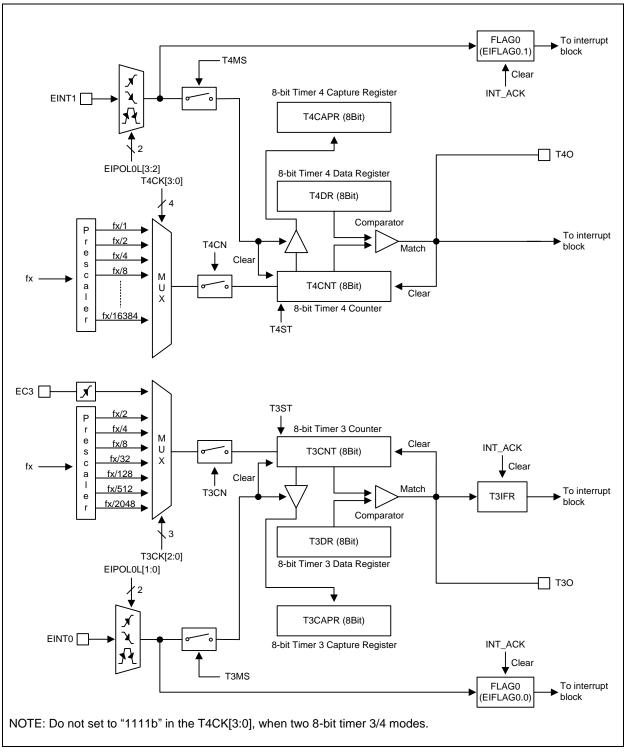

| Figure 11.45 Two 8-Bit Timer 3, 4 Block Diagram                             |     |

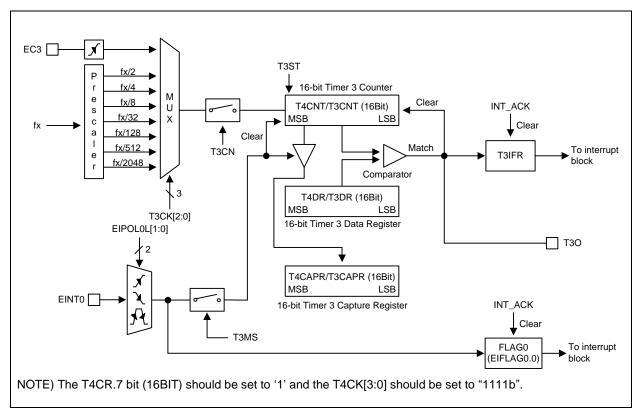

| Figure 11.46 16-Bit Timer 3 Block Diagram                                   | 159 |

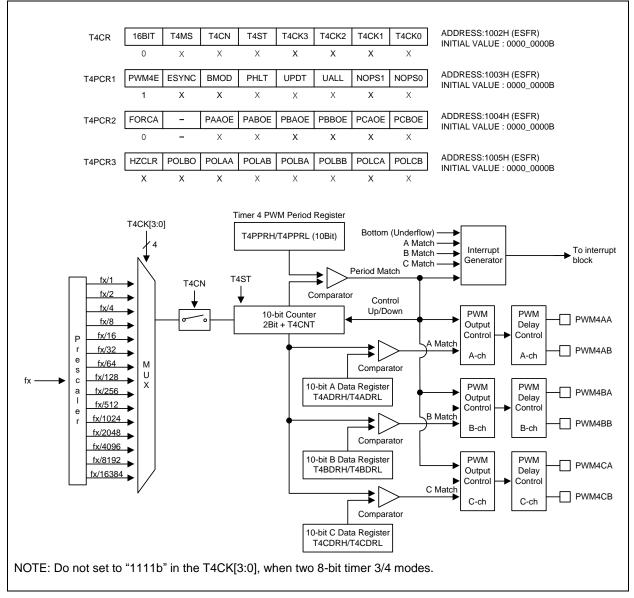

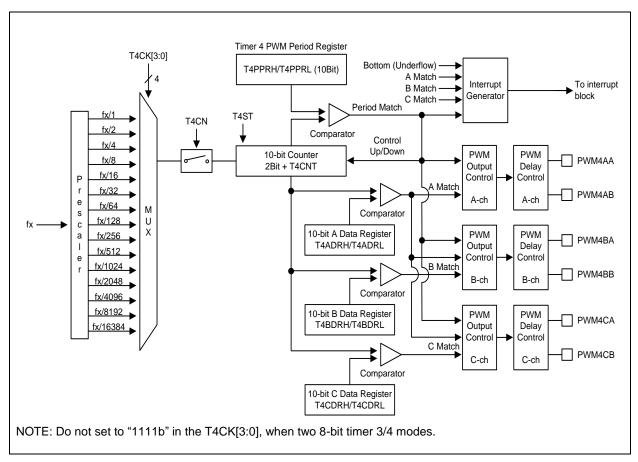

| Figure 11.47 10-Bit PWM Timer 4 Block Diagram                               | 159 |

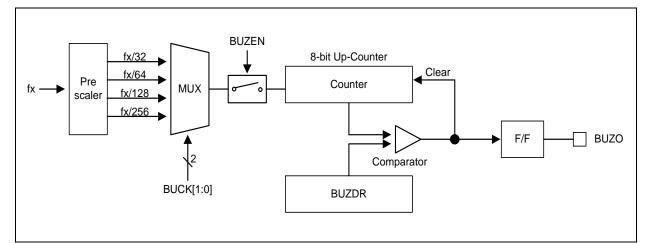

| Figure 11.48 Buzzer Driver Block Diagram                                    |     |

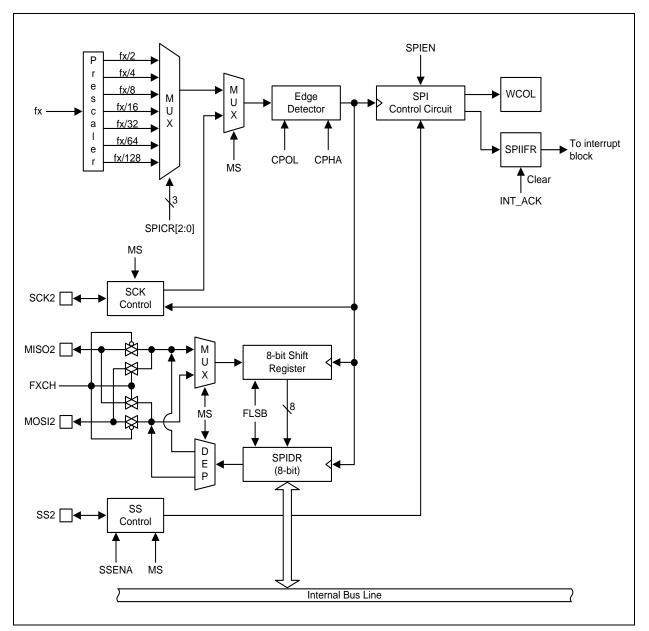

| Figure 11.49 SPI 2 Block Diagram                                            | 173 |

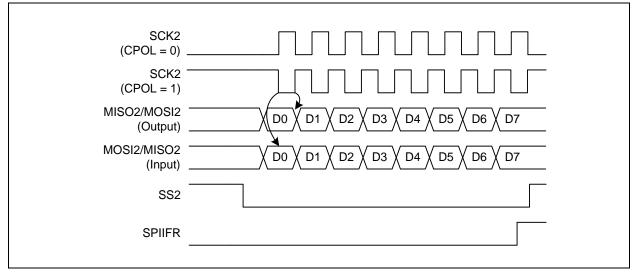

| Figure 11.50 SPI 2 Transmit/Receive Timing Diagram at CPHA = 0              |     |

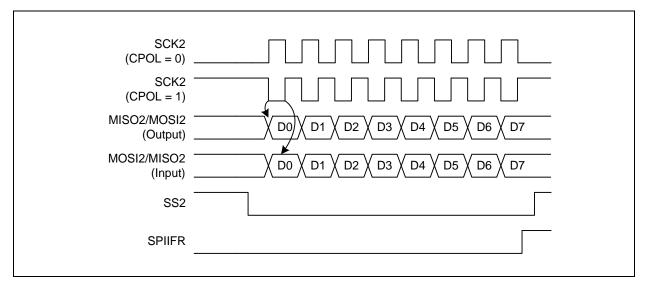

| Figure 11.51 SPI 2 Transmit/Receive Timing Diagram at CPHA = 1              | 175 |

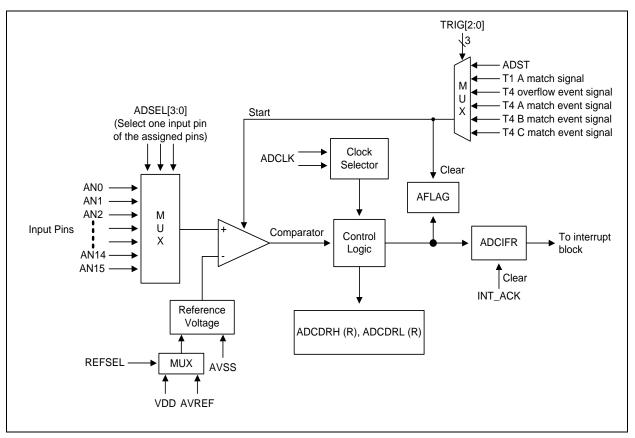

| Figure 11.52 12-bit ADC Block Diagram                                       | 180 |

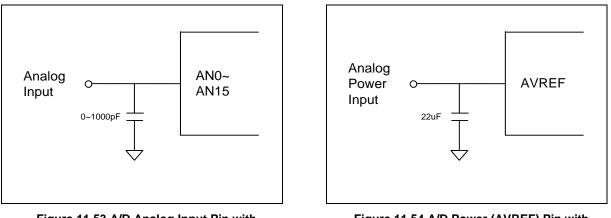

| Figure 11.53 A/D Analog Input Pin with Capacitor                            | 180 |

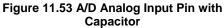

| Figure 11.54 A/D Power (AVREF) Pin with Capacitor                           |     |

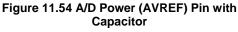

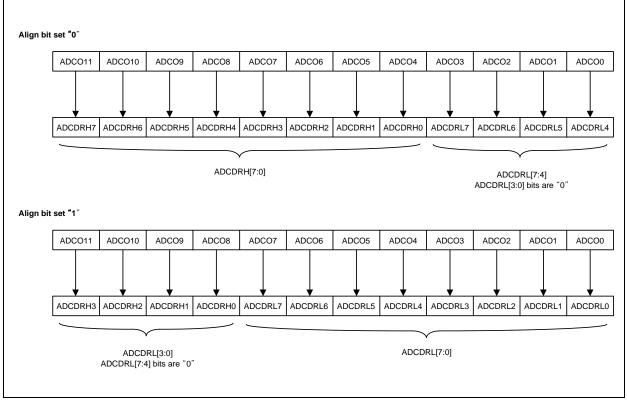

| Figure 11.55 ADC Operation for Align Bit                                    | 181 |

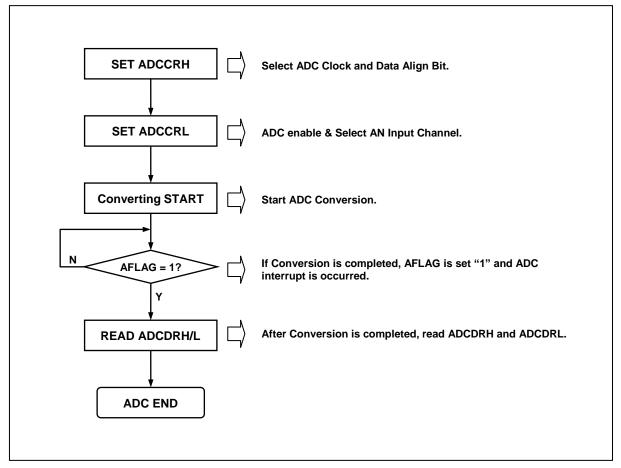

| Figure 11.56 A/D Converter Operation Flow                                   | 182 |

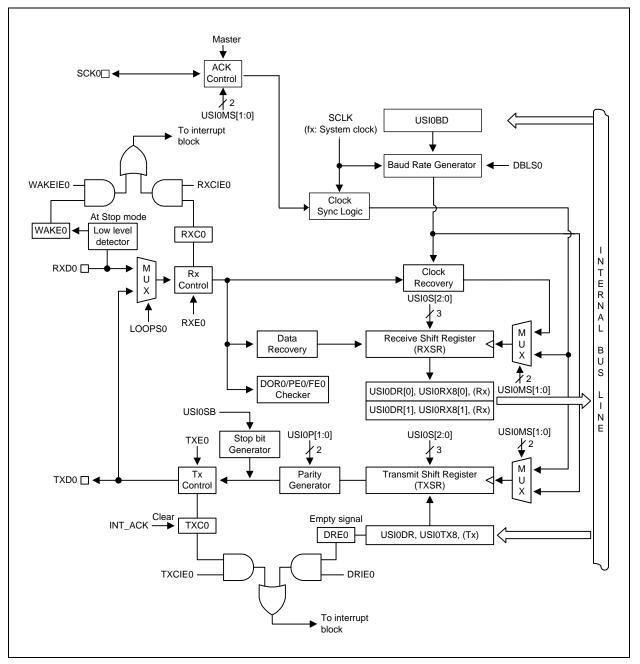

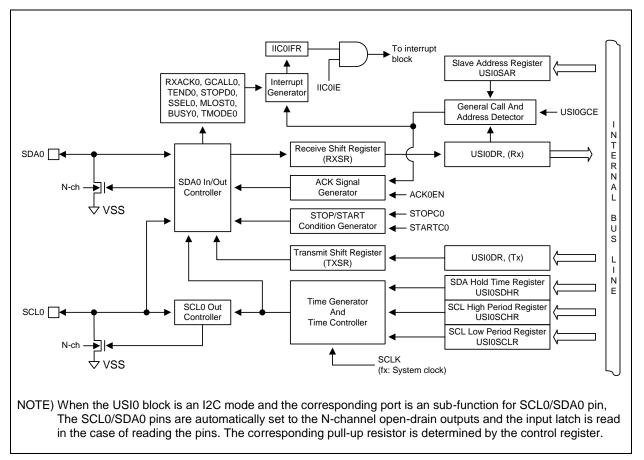

| Figure 11.57 USI0 UART Block Diagram                                        |     |

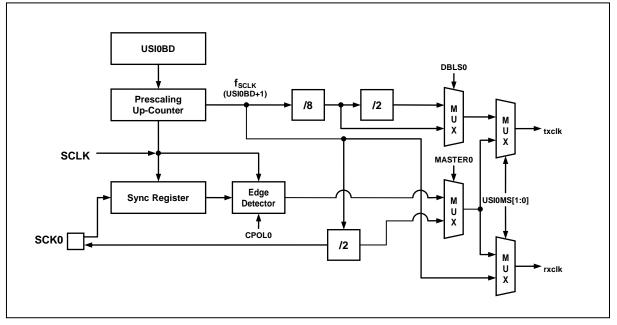

| Figure 11.58 Clock Generation Block Diagram (USI0)                          |     |

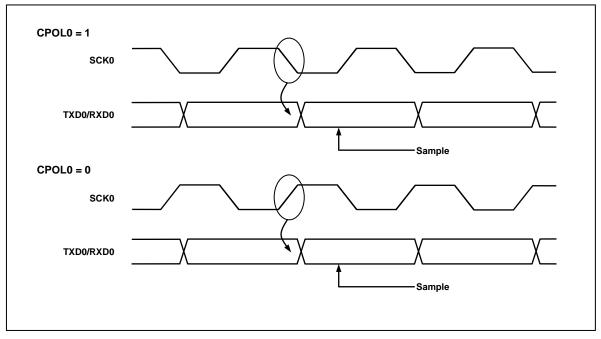

| Figure 11.59 Synchronous Mode SCK0 Timing (USI0)                            |     |

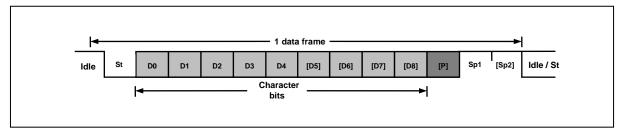

| Figure 11.60 Frame Format (USI0)                                            |     |

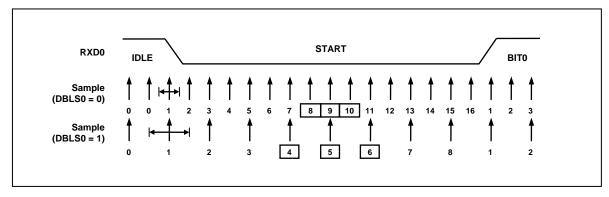

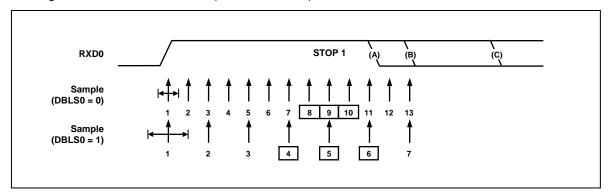

| Figure 11.61 Asynchronous Start Bit Sampling (USI0)                         |     |

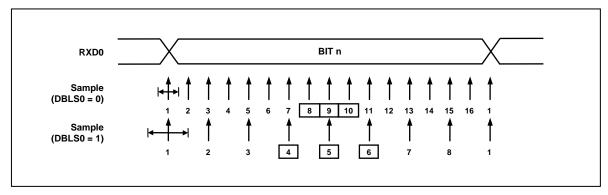

| Figure 11.62 Asynchronous Sampling of Data and Parity Bit (USI0)            |     |

| Figure 11.63 Stop Bit Sampling and Next Start Bit Sampling (USI0)           |     |

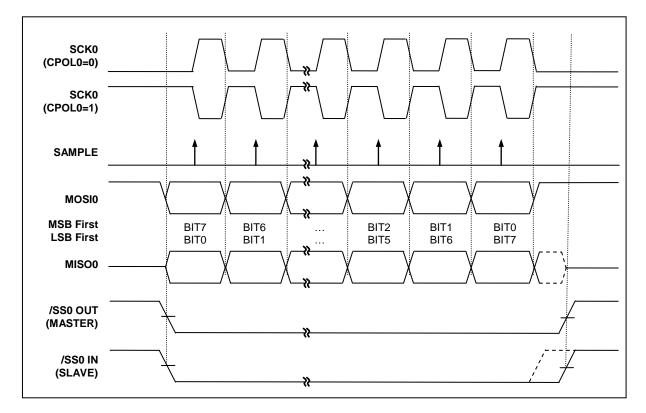

| Figure 11.64 USI0 SPI Clock Formats when CPHA0=0                            |     |

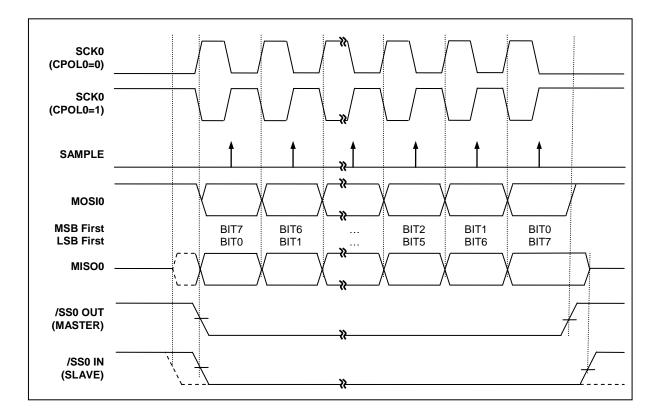

| Figure 11.65 USI0 SPI Clock Formats when CPHA0=1                            | 198 |

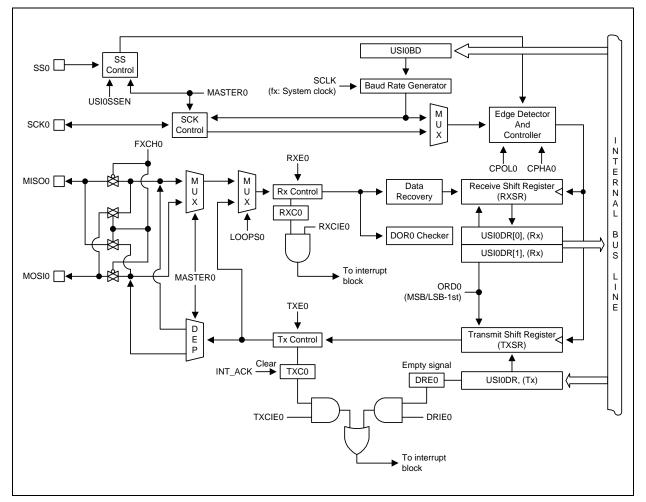

| Figure 11.66 USI0 SPI Block Diagram                                         |     |

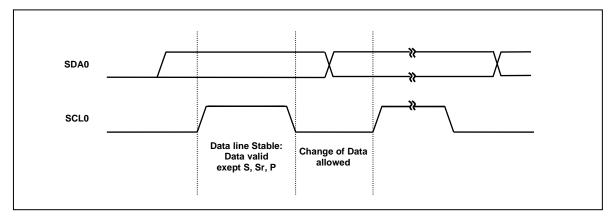

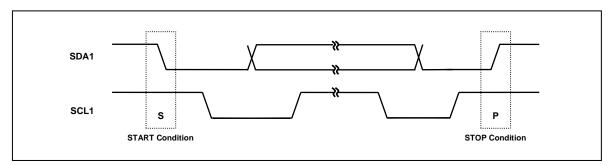

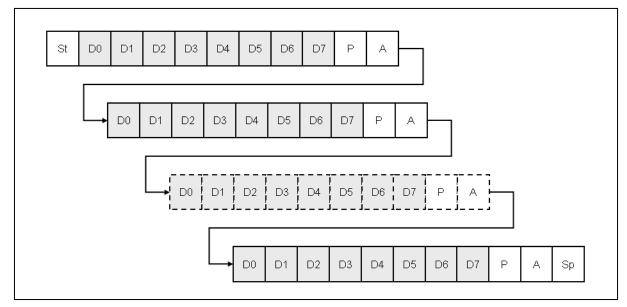

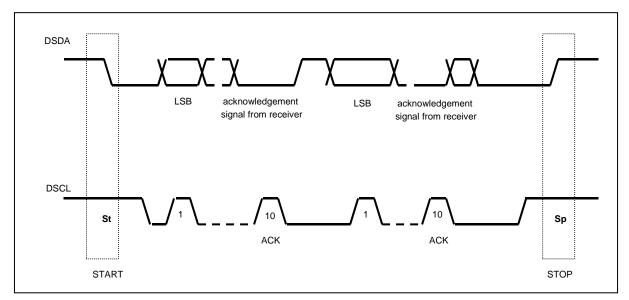

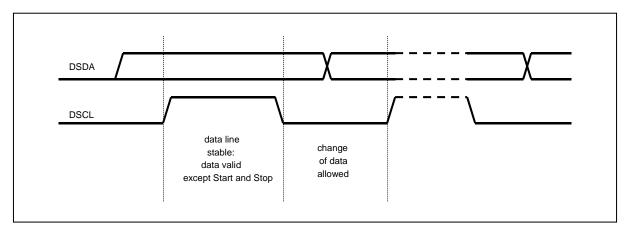

| Figure 11.67 Bit Transfer on the I2C-Bus (USI0)                             | 200 |

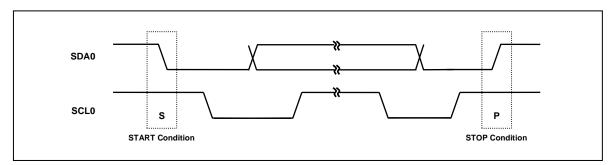

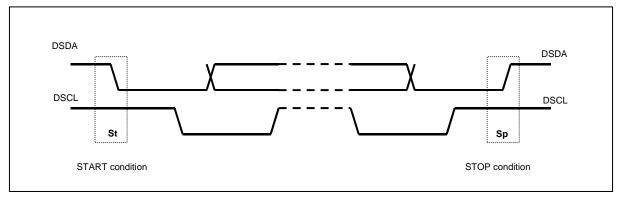

| Figure 11.68 START and STOP Condition (USI0)                                | 201 |

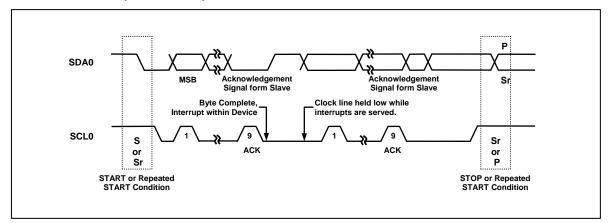

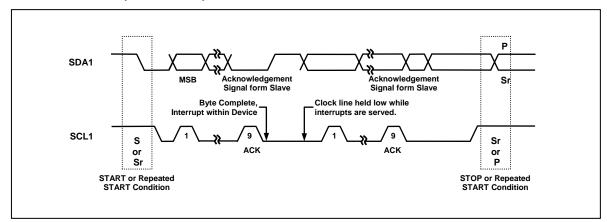

| Figure 11.69 Data Transfer on the I2C-Bus (USI0)                            | 201 |

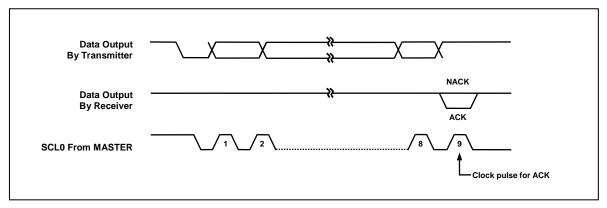

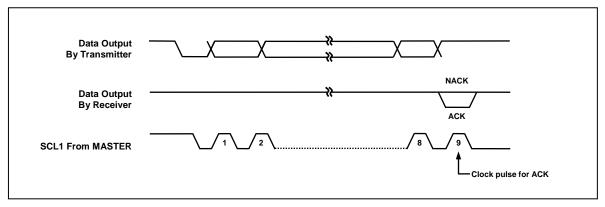

| Figure 11.70 Acknowledge on the I2C-Bus (USI0)                              |     |

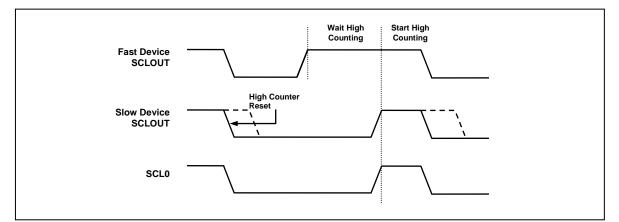

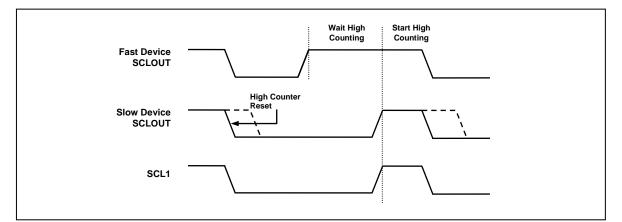

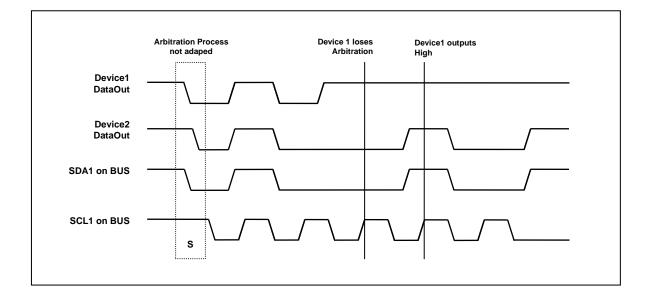

| Figure 11.71 Clock Synchronization during Arbitration Procedure (USI0)      | 203 |

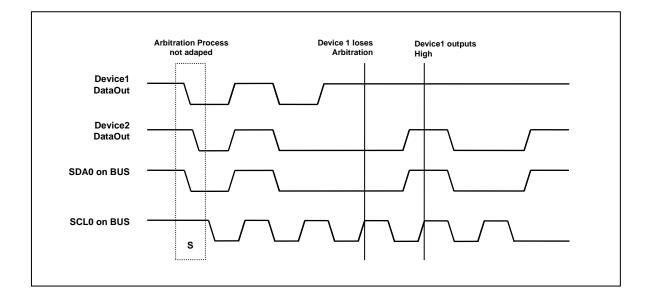

| Figure 11.72 Arbitration Procedure of Two Masters (USI0)                    | 203 |

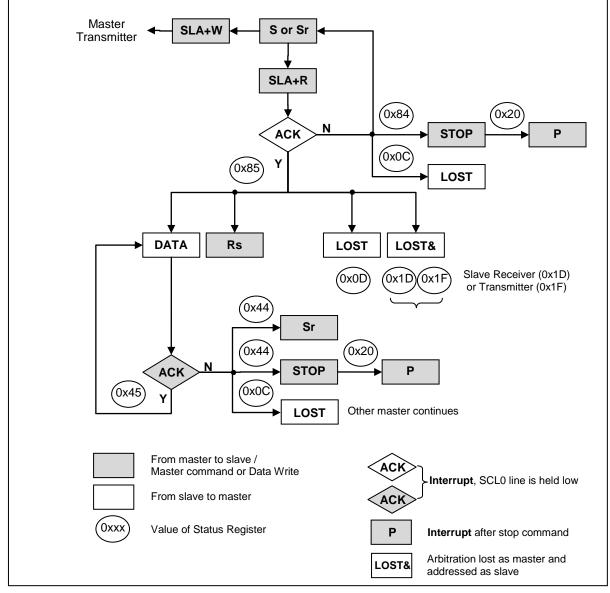

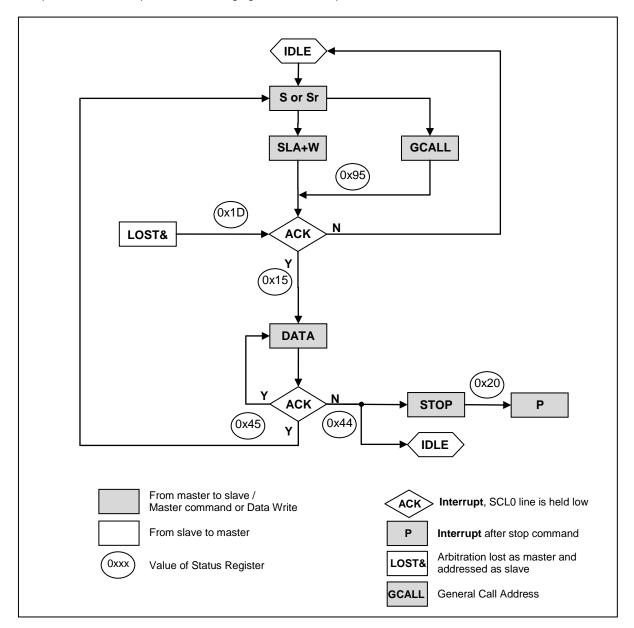

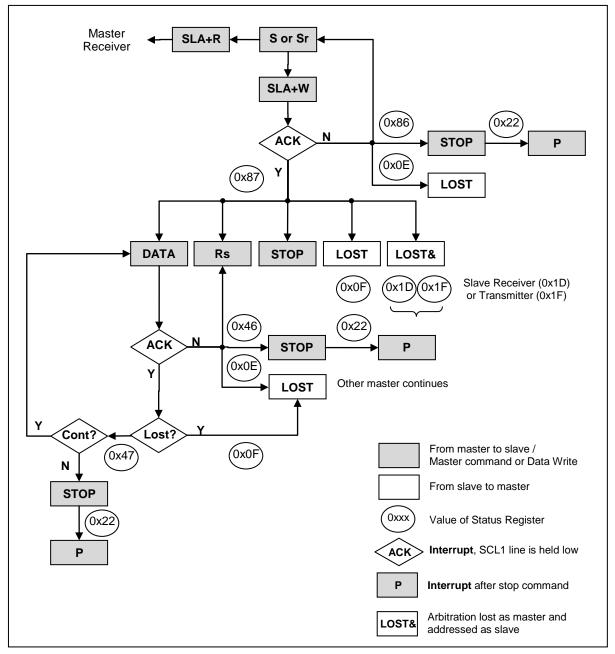

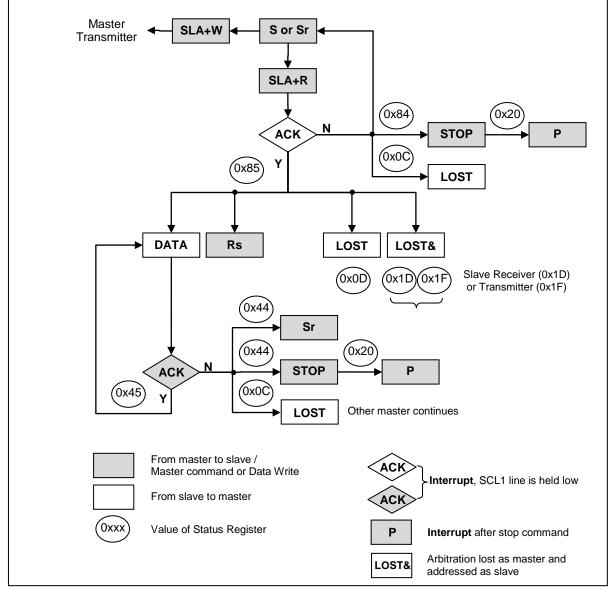

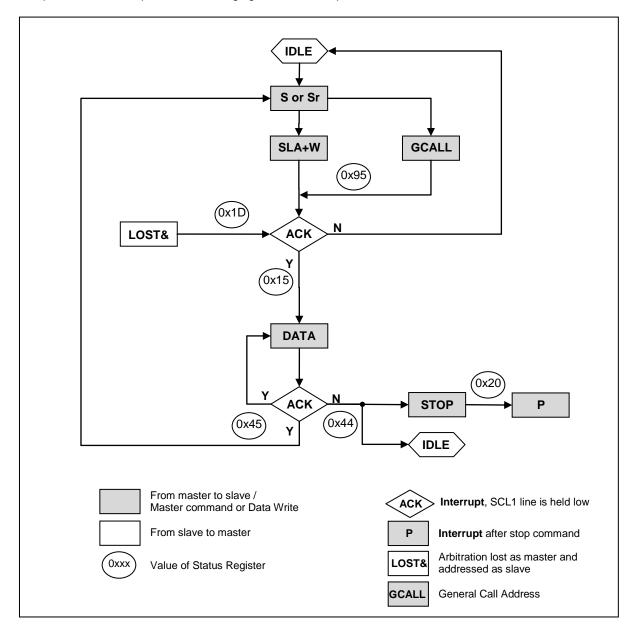

| Figure 11.73 Formats and States in the Master Transmitter Mode (USI0)       | 205 |

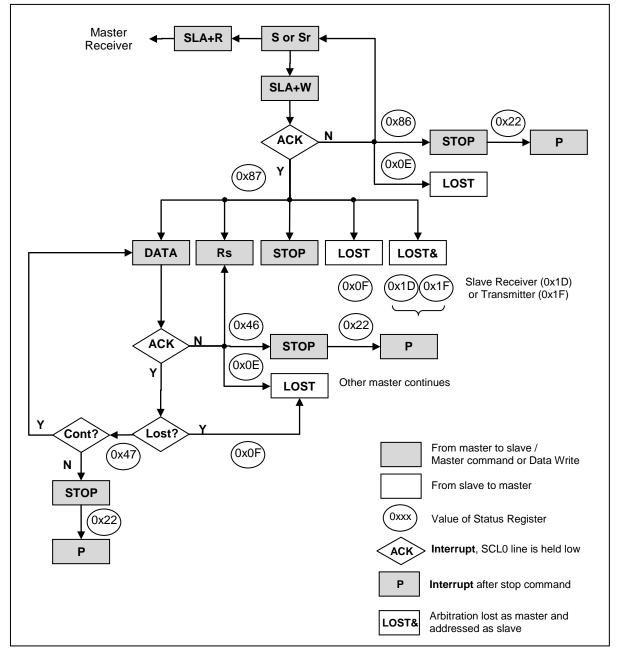

| Figure 11.74 Formats and States in the Master Receiver Mode (USI0)          | 207 |

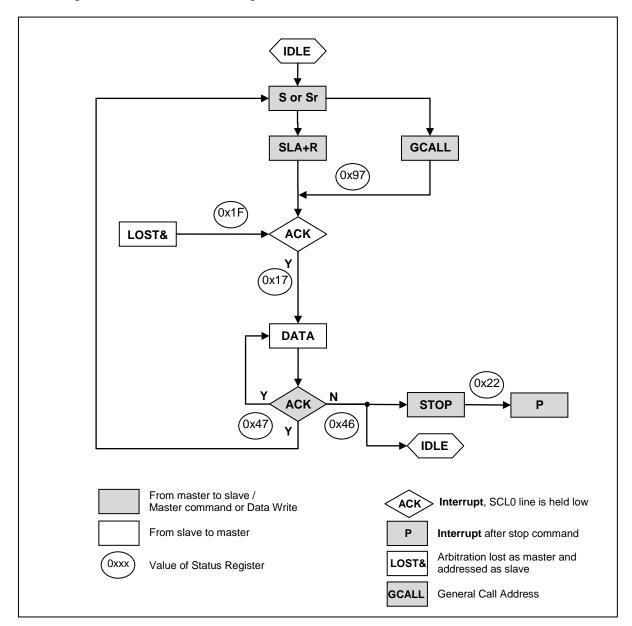

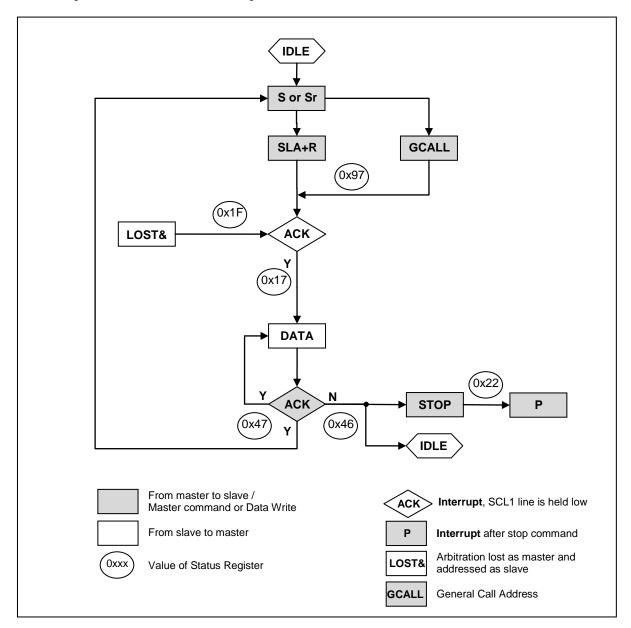

| Figure 11.75 Formats and States in the Slave Transmitter Mode (USI0)        | 209 |

| Figure 11.76 Formats and States in the Slave Receiver Mode (USI0)           |     |

| Figure 11.77 USI0 I2C Block Diagram                                         |     |

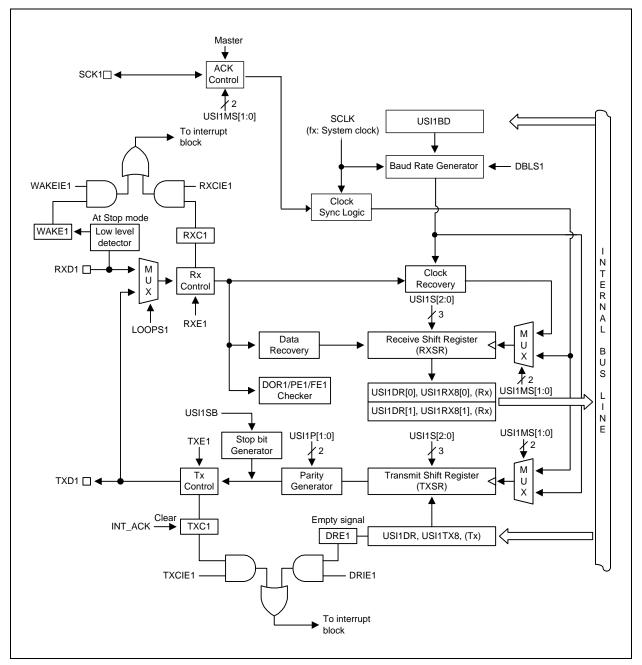

| Figure 11.78 USI1 UART Block Diagram                                        |     |

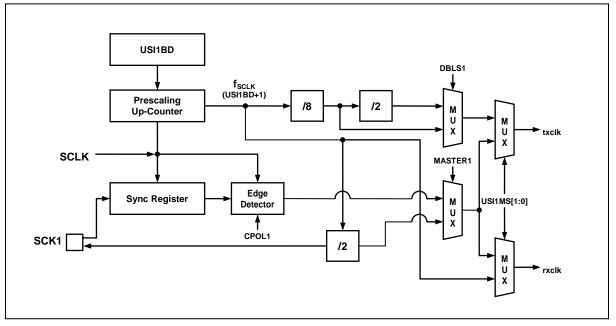

| Figure 11.79 Clock Generation Block Diagram (USI1)                          |     |

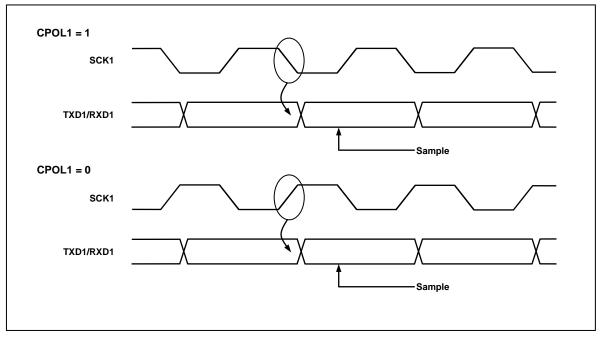

| Figure 11.80 Synchronous Mode SCK1 Timing (USI1)                            | 226 |

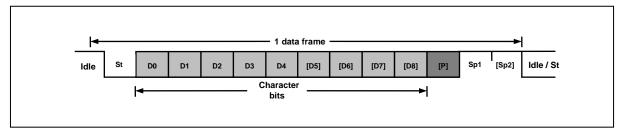

| Figure 11.81 Frame Format (USI1)                                            |     |

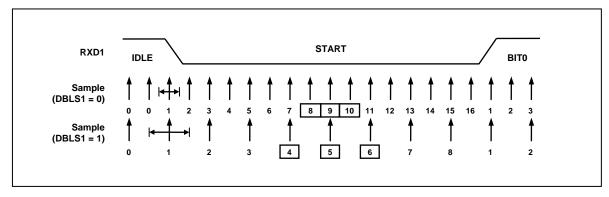

| Figure 11.82 Asynchronous Start Bit Sampling (USI1)                         |     |

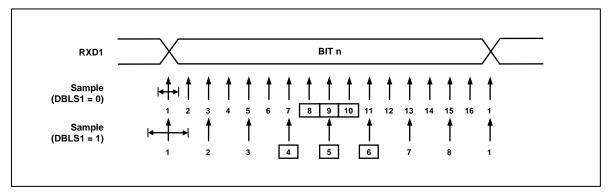

| Figure 11.83 Asynchronous Sampling of Data and Parity Bit (USI1)            | 231 |

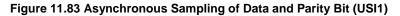

| F | igure 11.84 Stop Bit Sampling and Next Start Bit Sampling (USI1)      | 232 |

|---|-----------------------------------------------------------------------|-----|

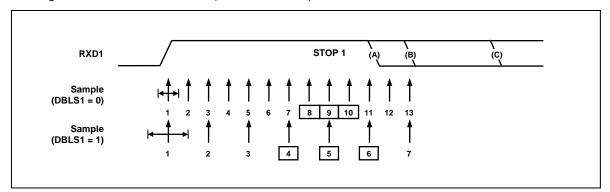

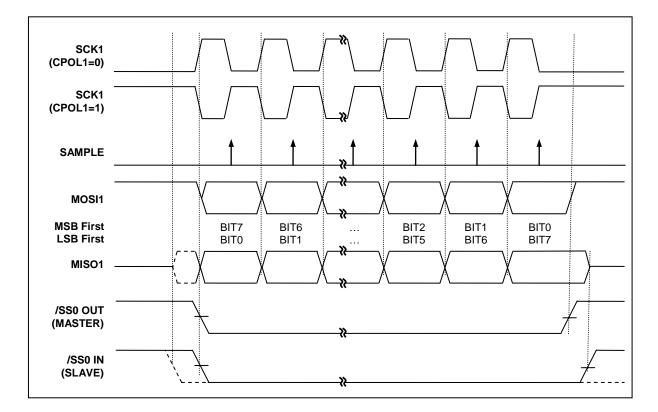

| F | igure 11.85 USI1 SPI Clock Formats when CPHA1=0                       | 234 |

| F | igure 11.86 USI1 SPI Clock Formats when CPHA1=1                       | 235 |

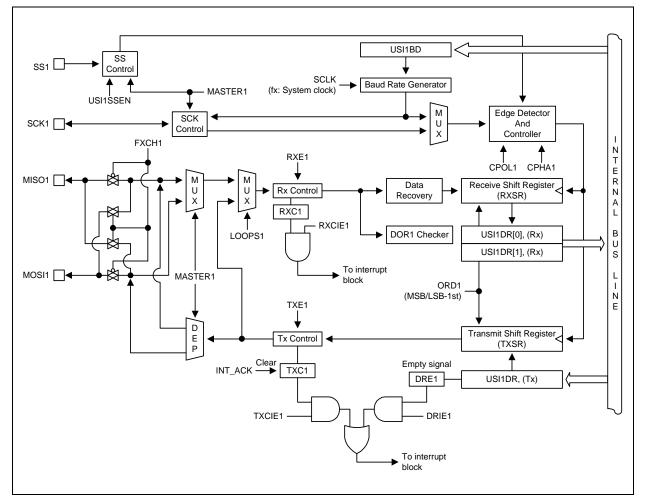

| F | igure 11.87 USI1 SPI Block Diagram                                    | 236 |

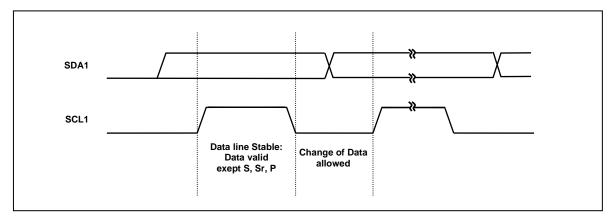

| F | igure 11.88 Bit Transfer on the I2C-Bus (USI1)                        | 237 |

| F | igure 11.89 START and STOP Condition (USI1)                           | 238 |

| F | igure 11.90 Data Transfer on the I2C-Bus (USI1)                       | 238 |

| F | igure 11.91 Acknowledge on the I2C-Bus (USI1)                         | 239 |

| F | igure 11.92 Clock Synchronization during Arbitration Procedure (USI1) | 240 |

| F | igure 11.93 Arbitration Procedure of Two Masters (USI1)               | 240 |

| F | igure 11.94 Formats and States in the Master Transmitter Mode (USI1)  | 242 |

| F | igure 11.95 Formats and States in the Master Receiver Mode (USI1)     | 244 |

| F | igure 11.96 Formats and States in the Slave Transmitter Mode (USI1)   | 246 |

| F | igure 11.97 Formats and States in the Slave Receiver Mode (USI1)      | 248 |

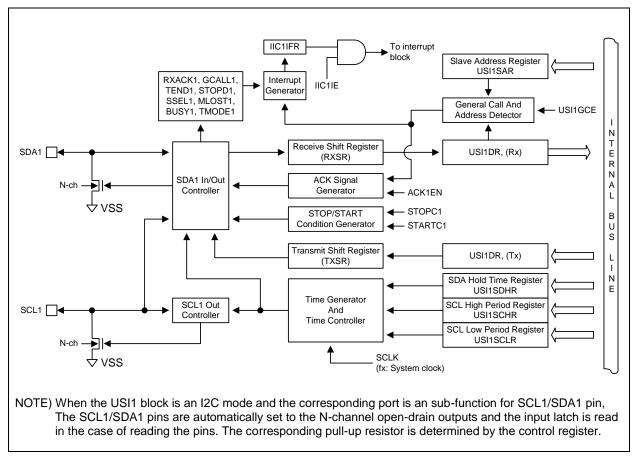

| F | igure 11.98 USI1 I2C Block Diagram                                    | 249 |

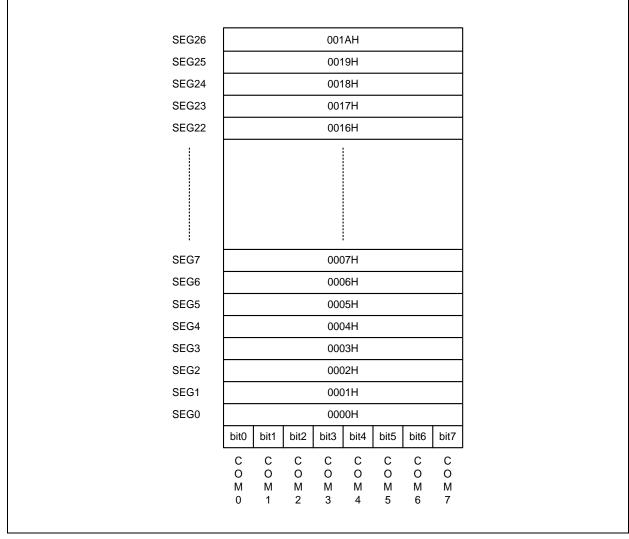

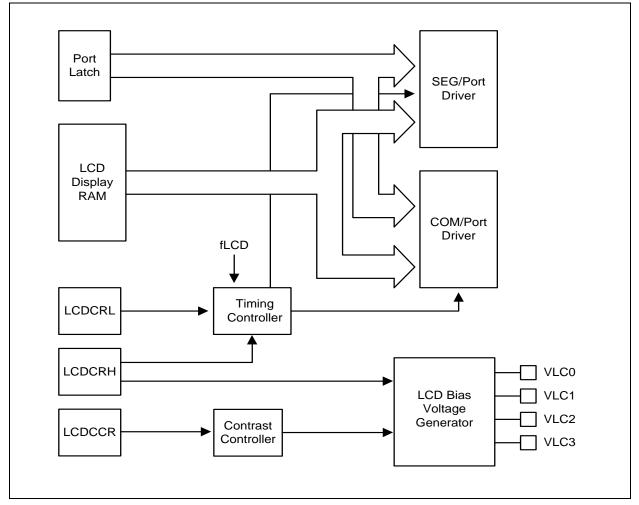

| F | igure 11.99 LCD Circuit Block Diagram                                 | 261 |

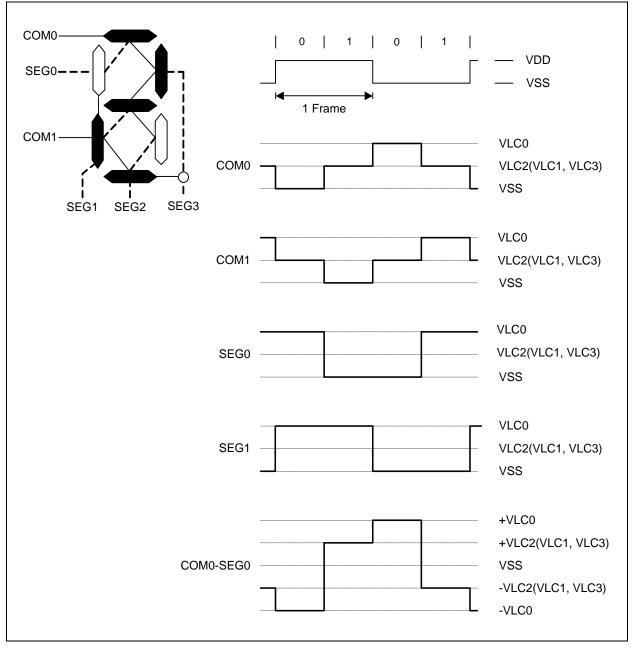

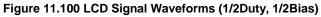

| F | igure 11.100 LCD Signal Waveforms (1/2Duty, 1/2Bias)                  | 262 |

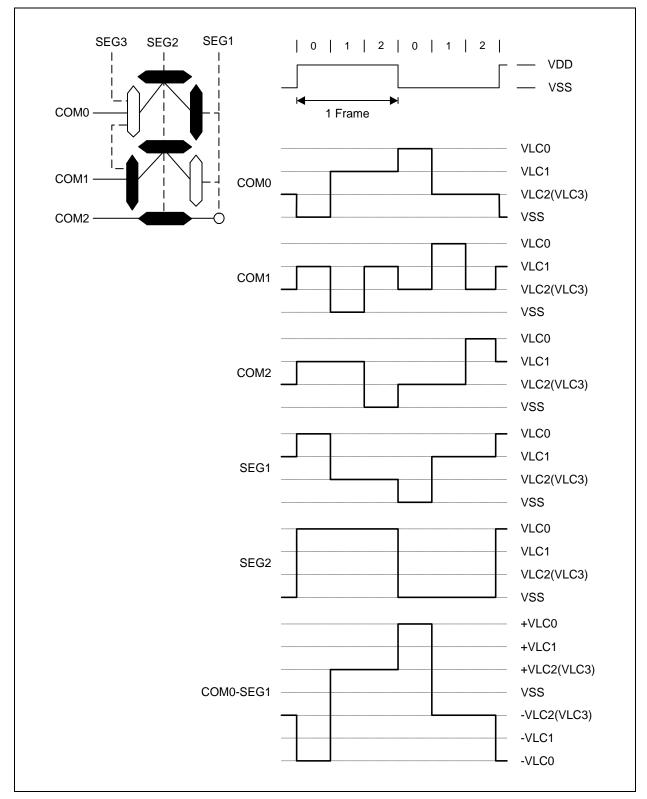

| F | igure 11.101 LCD Signal Waveforms (1/3Duty, 1/3Bias)                  | 263 |

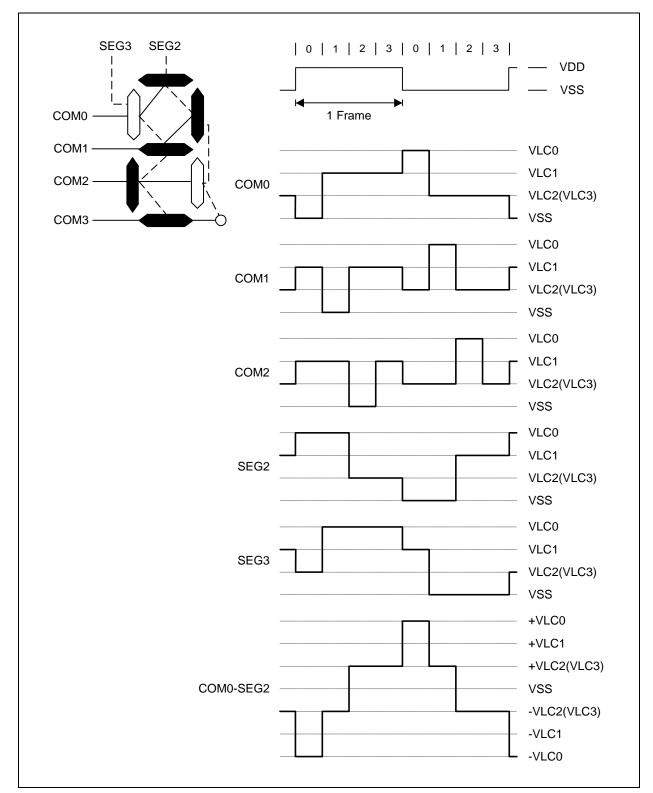

| F | igure 11.102 LCD Signal Waveforms (1/4Duty, 1/3Bias)                  | 264 |

|   | igure 11.103 LCD Signal Waveforms (1/8Duty, 1/4Bias)                  |     |

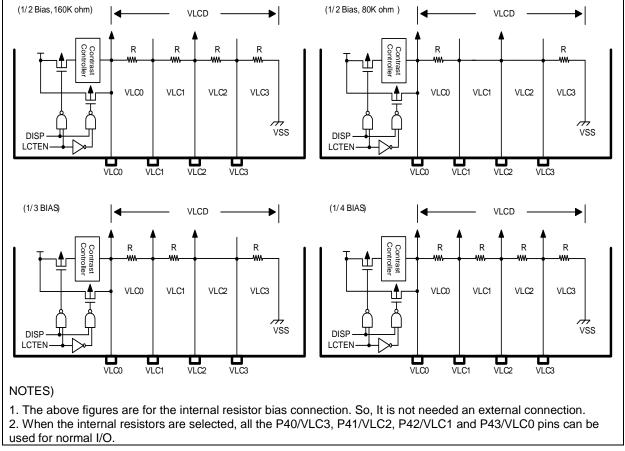

|   | igure 11.104 Internal Resistor Bias Connection                        |     |

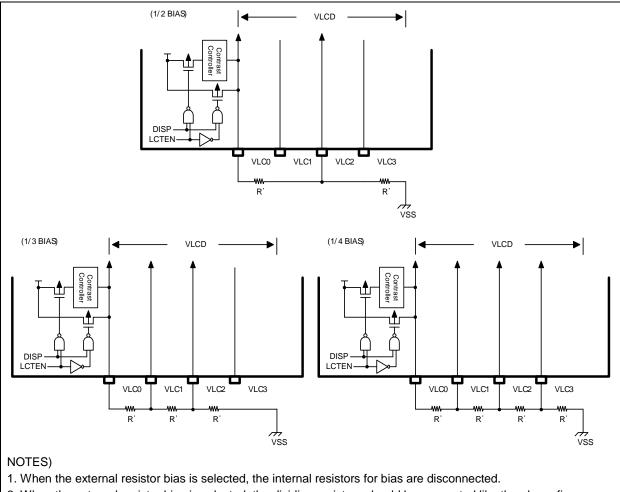

| F | igure 11.105 External Resistor Bias Connection                        | 267 |

| F | igure 11.106 LCD Circuit Block Diagram                                | 268 |

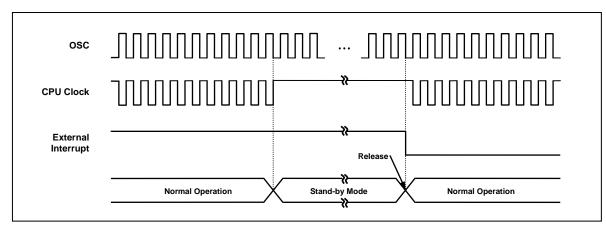

|   | igure 12.1 IDLE Mode Release Timing by External Interrupt             |     |

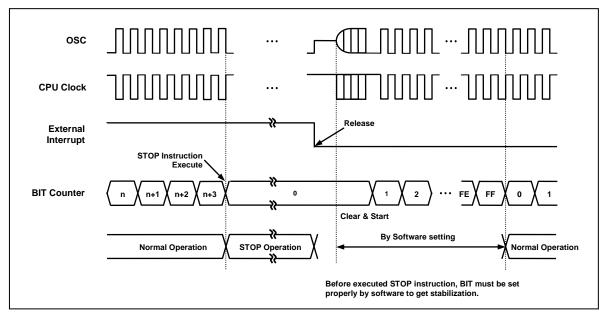

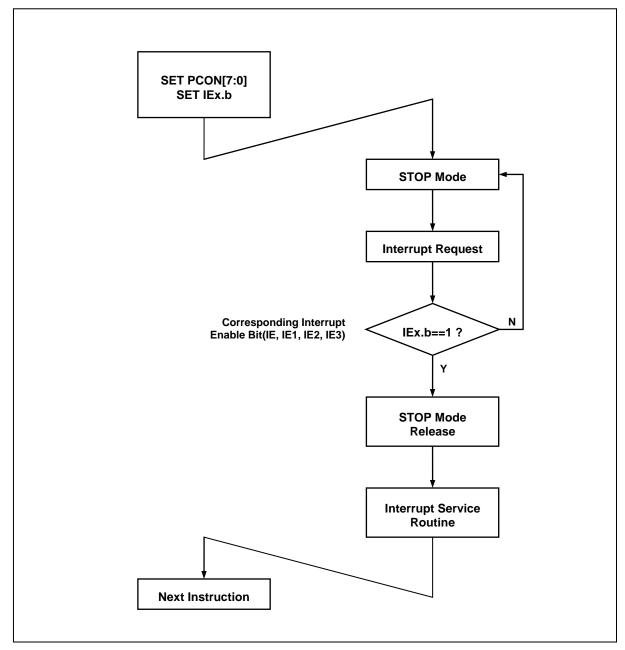

|   | igure 12.2 STOP Mode Release Timing by External Interrupt             |     |

|   | igure 12.3 STOP Mode Release Flow                                     |     |

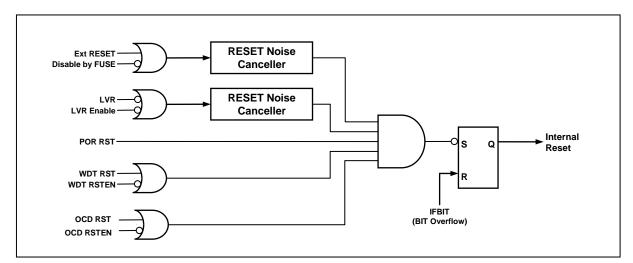

|   | igure 13.1 RESET Block Diagram                                        |     |

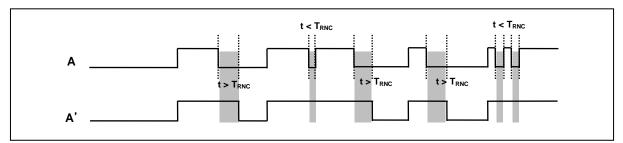

|   | igure 13.2 Reset noise canceller timer diagram                        |     |

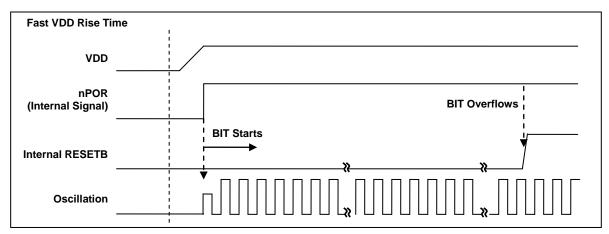

|   | igure 13.3 Fast VDD Rising Time                                       |     |

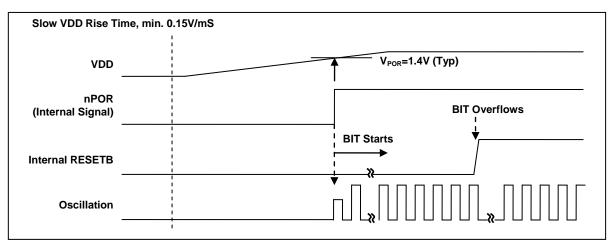

|   | igure 13.4 Internal RESET Release Timing On Power-Up                  |     |

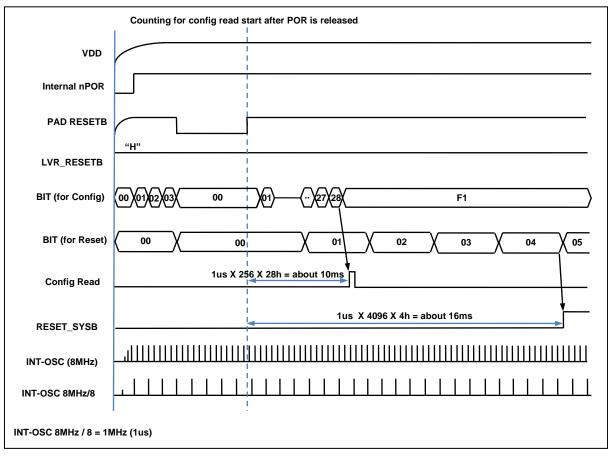

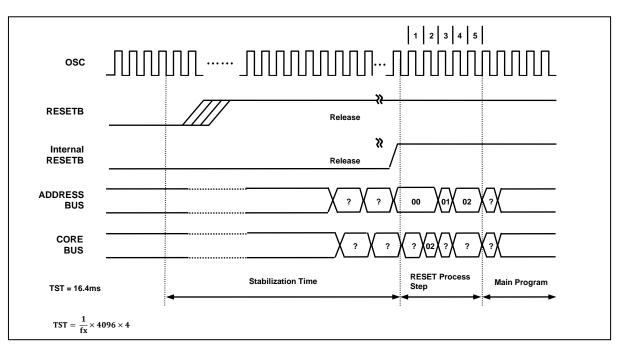

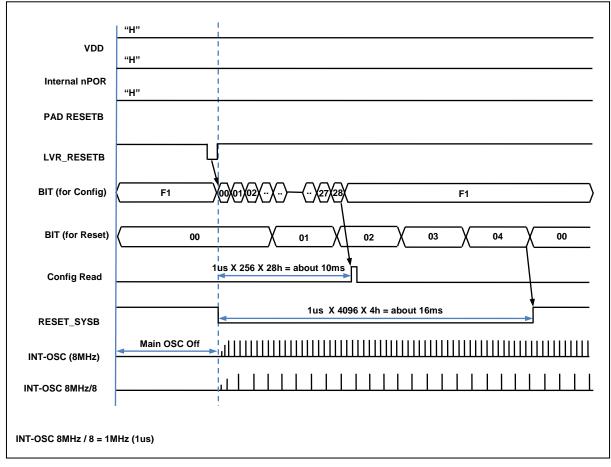

|   | igure 13.5 Configuration Timing when Power-on                         |     |

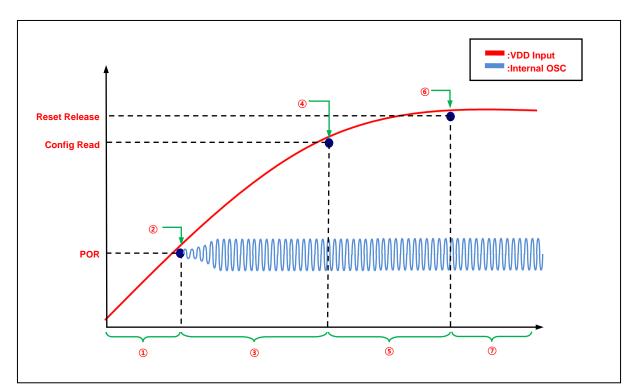

|   | igure 13.6 Boot Process WaveForm                                      |     |

|   | igure 13.7 Timing Diagram after RESET                                 |     |

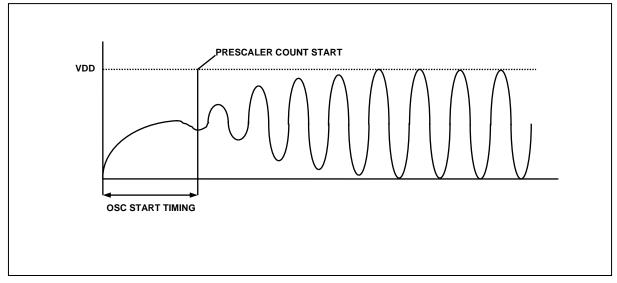

|   | igure 13.8 Oscillator generating waveform example                     |     |

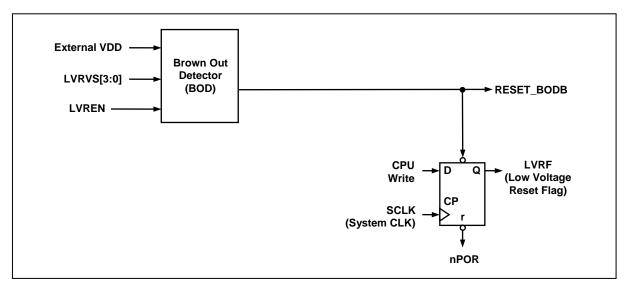

|   | igure 13.9 Block Diagram of BOD                                       |     |

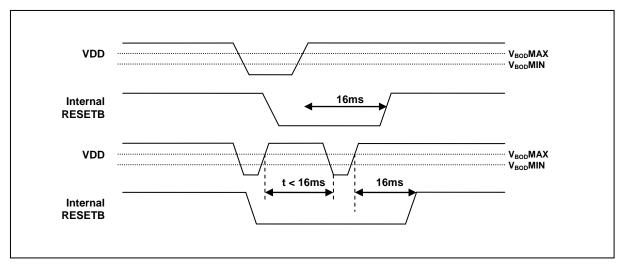

|   | igure 13.10 Internal Reset at the power fail situation                |     |

|   | igure 13.11 Configuration timing when BOD RESET                       |     |

|   | igure 13.12 LVI Diagram                                               |     |

|   | igure 14.1 Block Diagram of On-Chip Debug System                      |     |

|   | igure 14.2 10-bit Transmission Packet                                 |     |

|   | igure 14.3 Data Transfer on the Twin Bus                              |     |

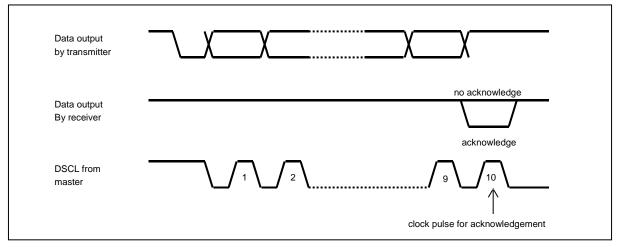

|   | igure 14.4 Bit Transfer on the Serial Bus                             |     |

|   | igure 14.5 Start and Stop Condition                                   |     |

|   | igure 14.6 Acknowledge on the Serial Bus                              |     |

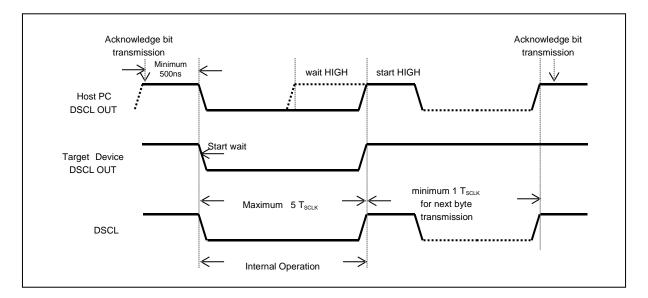

|   | igure 14.7 Clock Synchronization during Wait Procedure                |     |

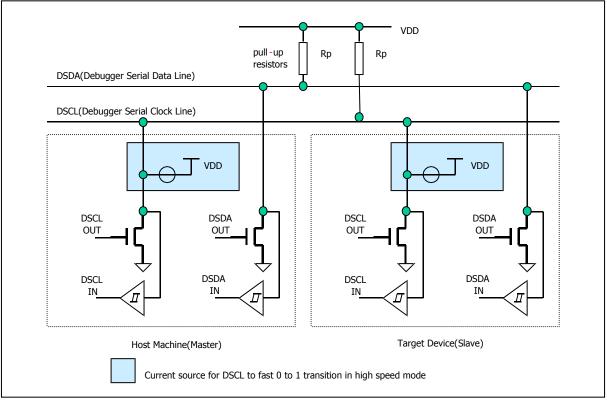

|   | igure 14.8 Connection of Transmission                                 |     |

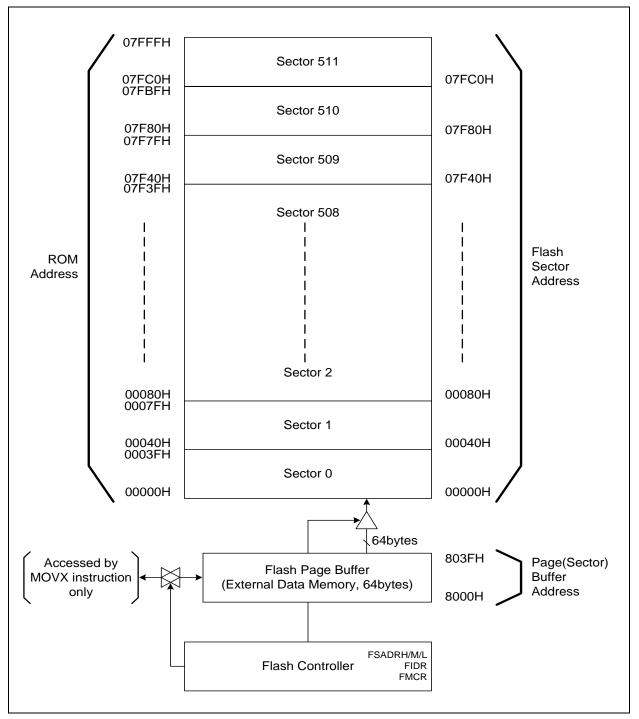

| - | igure 15.1 Flash Program ROM Structure                                | 294 |

# **List of Tables**

| Table 1-1 Ordering Information of MC96F6432                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Table 5-1 Normal Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22                                                                                                                                  |

| Table 7-1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                                                                                                  |

| Table 7-2 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                                                                                                                                  |

| Table 7-3 A/D Converter Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30                                                                                                                                  |

| Table 7-4 Power-on Reset Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30                                                                                                                                  |

| Table 7-5 LVR and LVI Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                     |

| Table 7-6 High Internal RC Oscillator Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32                                                                                                                                  |

| Table 7-7 Internal WDTRC Oscillator Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32                                                                                                                                  |

| Table 7-8 LCD Voltage Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                     |

| Table 7-9 DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34                                                                                                                                  |

| Table 7-10 AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36                                                                                                                                  |

| Table 7-11 SPI0/1/2 Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                                                                                  |

| Table 7-12 UART0/1 Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38                                                                                                                                  |

| Table 7-13 I2C0/1 Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                     |

| Table 7-14 Data Retention Voltage in Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                     |

| Table 7-15 Internal Flash Rom Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                     |

| Table 7-16 Input/Output Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                     |

| Table 7-17 Main Clock Oscillator Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                     |

| Table 7-18 Sub Clock Oscillator Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                     |

| Table 7-19 Main Oscillation Stabilization Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                     |

| Table 7-20 Sub Oscillation Stabilization Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                     |

| Table 8-1 SFR Map Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                     |

| Table 8-2 SFR Map Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56                                                                                                                                  |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56<br>57                                                                                                                            |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map         Table 9-1 Port Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56<br>57<br>65                                                                                                                      |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map         Table 9-1 Port Register Map         Table 10-1 Interrupt Group Priority Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56<br>57<br>65<br>83                                                                                                                |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map         Table 9-1 Port Register Map         Table 10-1 Interrupt Group Priority Level         Table 10-2 Interrupt Vector Address Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56<br>57<br>65<br>83<br>86                                                                                                          |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map         Table 9-1 Port Register Map         Table 10-1 Interrupt Group Priority Level         Table 10-2 Interrupt Vector Address Table         Table 10-3 Interrupt Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56<br>57<br>65<br>83<br>86<br>93                                                                                                    |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map         Table 9-1 Port Register Map         Table 10-1 Interrupt Group Priority Level         Table 10-2 Interrupt Vector Address Table         Table 10-3 Interrupt Register Map         Table 11-1 Clock Generator Register Map                                                                                                                                                                                                                                                                                                                                                                                               | 56<br>57<br>65<br>83<br>86<br>93<br>101                                                                                             |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map         Table 9-1 Port Register Map         Table 10-1 Interrupt Group Priority Level         Table 10-2 Interrupt Vector Address Table         Table 10-3 Interrupt Register Map         Table 11-1 Clock Generator Register Map         Table 11-2 Basic Interval Timer Register Map                                                                                                                                                                                                                                                                                                                                          | 56<br>57<br>65<br>83<br>86<br>93<br>101<br>104                                                                                      |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map.         Table 9-1 Port Register Map.         Table 10-1 Interrupt Group Priority Level.         Table 10-2 Interrupt Vector Address Table         Table 10-3 Interrupt Register Map.         Table 11-1 Clock Generator Register Map.         Table 11-2 Basic Interval Timer Register Map.         Table 11-3 Watch Dog Timer Register Map.                                                                                                                                                                                                                                                                                   | 56<br>57<br>83<br>93<br>93<br>101<br>104<br>107                                                                                     |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map         Table 9-1 Port Register Map         Table 10-1 Interrupt Group Priority Level         Table 10-2 Interrupt Vector Address Table         Table 10-3 Interrupt Register Map         Table 11-1 Clock Generator Register Map         Table 11-2 Basic Interval Timer Register Map         Table 11-3 Watch Dog Timer Register Map         Table 11-4 Watch Timer Register Map                                                                                                                                                                                                                                              | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>107<br>110                                                                              |

| Table 8-2 SFR Map SummaryTable 8-3 SFR MapTable 9-1 Port Register MapTable 10-1 Interrupt Group Priority LevelTable 10-2 Interrupt Vector Address TableTable 10-3 Interrupt Register MapTable 11-1 Clock Generator Register MapTable 11-2 Basic Interval Timer Register MapTable 11-3 Watch Dog Timer Register MapTable 11-4 Watch Timer Register MapTable 11-5 Timer 0 Operating Modes                                                                                                                                                                                                                                                                                             | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>107<br>110<br>112                                                                       |

| Table 8-2 SFR Map Summary         Table 8-3 SFR Map.         Table 9-1 Port Register Map.         Table 10-1 Interrupt Group Priority Level.         Table 10-2 Interrupt Vector Address Table         Table 10-3 Interrupt Register Map.         Table 11-1 Clock Generator Register Map.         Table 11-2 Basic Interval Timer Register Map.         Table 11-3 Watch Dog Timer Register Map.         Table 11-4 Watch Timer Register Map.         Table 11-5 Timer 0 Operating Modes.         Table 11-6 Timer 0 Register Map.                                                                                                                                                 | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>107<br>110<br>112<br>119                                                                |

| Table 8-2 SFR Map SummaryTable 8-3 SFR Map.Table 9-1 Port Register Map.Table 10-1 Interrupt Group Priority Level.Table 10-2 Interrupt Vector Address TableTable 10-3 Interrupt Register Map.Table 11-1 Clock Generator Register Map.Table 11-2 Basic Interval Timer Register Map.Table 11-3 Watch Dog Timer Register Map.Table 11-4 Watch Timer Register Map.Table 11-5 Timer 0 Operating Modes.Table 11-6 Timer 1 Operating Modes.                                                                                                                                                                                                                                                 | 56<br>57<br>65<br>93<br>101<br>104<br>107<br>110<br>112<br>119<br>121                                                               |

| Table 8-2 SFR Map SummaryTable 8-3 SFR Map.Table 9-1 Port Register MapTable 10-1 Interrupt Group Priority Level.Table 10-2 Interrupt Vector Address TableTable 10-3 Interrupt Register MapTable 11-1 Clock Generator Register MapTable 11-2 Basic Interval Timer Register MapTable 11-3 Watch Dog Timer Register MapTable 11-4 Watch Timer Register MapTable 11-5 Timer 0 Operating ModesTable 11-6 Timer 1 Operating ModesTable 11-8 Timer 2 Register Map                                                                                                                                                                                                                          | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>107<br>110<br>112<br>119<br>121<br>127                                                  |

| Table 8-2 SFR Map SummaryTable 8-3 SFR MapTable 9-1 Port Register MapTable 10-1 Interrupt Group Priority LevelTable 10-2 Interrupt Vector Address TableTable 10-3 Interrupt Register MapTable 11-1 Clock Generator Register MapTable 11-2 Basic Interval Timer Register MapTable 11-3 Watch Dog Timer Register MapTable 11-4 Watch Timer Register MapTable 11-5 Timer 0 Operating ModesTable 11-7 Timer 1 Operating ModesTable 11-8 Timer 2 Register Map                                                                                                                                                                                                                            | 56<br>57<br>65<br>83<br>93<br>101<br>107<br>110<br>112<br>119<br>121<br>127<br>131                                                  |

| Table 8-2 SFR Map SummaryTable 8-3 SFR MapTable 9-1 Port Register MapTable 10-1 Interrupt Group Priority LevelTable 10-2 Interrupt Vector Address TableTable 10-3 Interrupt Register MapTable 11-1 Clock Generator Register MapTable 11-2 Basic Interval Timer Register MapTable 11-3 Watch Dog Timer Register MapTable 11-4 Watch Timer Register MapTable 11-5 Timer 0 Operating ModesTable 11-6 Timer 0 Register MapTable 11-7 Timer 1 Operating ModesTable 11-8 Timer 2 Register MapTable 11-9 Timer 2 Operating ModesTable 11-10 Timer 3 Register Map                                                                                                                           | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>107<br>110<br>112<br>121<br>121<br>131<br>138                                           |

| Table 8-2 SFR Map SummaryTable 8-3 SFR MapTable 9-1 Port Register MapTable 10-1 Interrupt Group Priority LevelTable 10-2 Interrupt Vector Address TableTable 10-3 Interrupt Register MapTable 11-1 Clock Generator Register MapTable 11-2 Basic Interval Timer Register MapTable 11-3 Watch Dog Timer Register MapTable 11-4 Watch Timer Register MapTable 11-5 Timer 0 Operating ModesTable 11-7 Timer 1 Operating ModesTable 11-8 Timer 2 Register MapTable 11-9 Timer 3 Register MapTable 11-10 Timer 3, 4 Operating Modes                                                                                                                                                       | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>107<br>110<br>112<br>119<br>121<br>121<br>121<br>131<br>138<br>142                      |

| Table 8-2 SFR Map SummaryTable 8-3 SFR Map.Table 9-1 Port Register Map.Table 10-1 Interrupt Group Priority Level.Table 10-2 Interrupt Vector Address Table.Table 10-3 Interrupt Register Map.Table 11-1 Clock Generator Register Map.Table 11-2 Basic Interval Timer Register Map.Table 11-3 Watch Dog Timer Register Map.Table 11-4 Watch Timer Register Map.Table 11-5 Timer 0 Operating ModesTable 11-6 Timer 0 Register Map.Table 11-7 Timer 1 Operating ModesTable 11-9 Timer 2 Operating ModesTable 11-10 Timer 3, 4 Operating ModesTable 11-12 PWM Frequency vs. Resolution at 8 MHz                                                                                         | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>107<br>110<br>112<br>121<br>121<br>121<br>131<br>138<br>142<br>148                      |

| Table 8-2 SFR Map SummaryTable 8-3 SFR MapTable 9-1 Port Register MapTable 10-1 Interrupt Group Priority LevelTable 10-2 Interrupt Vector Address TableTable 10-3 Interrupt Register MapTable 11-1 Clock Generator Register MapTable 11-2 Basic Interval Timer Register MapTable 11-3 Watch Dog Timer Register MapTable 11-4 Watch Timer Register MapTable 11-5 Timer 0 Operating ModesTable 11-6 Timer 1 Operating ModesTable 11-9 Timer 2 Register MapTable 11-9 Timer 3 Register MapTable 11-10 Timer 3, 4 Operating ModesTable 11-12 PWM Frequency vs. Resolution at 8 MHzTable 11-13 PWM Channel Polarity                                                                      | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>104<br>110<br>112<br>112<br>121<br>121<br>121<br>138<br>148<br>148                      |

| Table 8-2 SFR Map SummaryTable 8-3 SFR MapTable 9-1 Port Register MapTable 10-1 Interrupt Group Priority LevelTable 10-2 Interrupt Vector Address TableTable 10-3 Interrupt Register MapTable 11-1 Clock Generator Register MapTable 11-2 Basic Interval Timer Register MapTable 11-3 Watch Dog Timer Register MapTable 11-4 Watch Timer Register MapTable 11-5 Timer 0 Operating ModesTable 11-6 Timer 0 Register MapTable 11-7 Timer 1 Operating ModesTable 11-8 Timer 2 Register MapTable 11-9 Timer 2 Operating ModesTable 11-10 Timer 3, 4 Operating ModesTable 11-12 PWM Frequency vs. Resolution at 8 MHzTable 11-13 PWM Channel PolarityTable 11-14 Timer 3, 4 Register Map | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>107<br>110<br>112<br>112<br>127<br>121<br>121<br>121<br>131<br>138<br>148<br>148<br>160 |

| Table 8-2 SFR Map SummaryTable 8-3 SFR MapTable 9-1 Port Register MapTable 10-1 Interrupt Group Priority LevelTable 10-2 Interrupt Vector Address TableTable 10-3 Interrupt Register MapTable 11-1 Clock Generator Register MapTable 11-2 Basic Interval Timer Register MapTable 11-3 Watch Dog Timer Register MapTable 11-4 Watch Timer Register MapTable 11-5 Timer 0 Operating ModesTable 11-6 Timer 1 Operating ModesTable 11-9 Timer 2 Register MapTable 11-9 Timer 3 Register MapTable 11-10 Timer 3, 4 Operating ModesTable 11-12 PWM Frequency vs. Resolution at 8 MHzTable 11-13 PWM Channel Polarity                                                                      | 56<br>57<br>65<br>83<br>93<br>101<br>104<br>107<br>110<br>112<br>121<br>121<br>121<br>121<br>131<br>138<br>148<br>160<br>171        |

| Table 11-17 SPI 2 Register Map                                                              | . 176 |

|---------------------------------------------------------------------------------------------|-------|

| Table 11-18 ADC Register Map                                                                | . 182 |

| Table 11-19 Equations for Calculating USI0 Baud Rate Register Setting                       | . 188 |

| Table 11-20 CPOL0 Functionality                                                             | . 196 |

| Table 11-21 USI0 Register Map                                                               | .213  |

| Table 11-22 Equations for Calculating USI1 Baud Rate Register Setting                       | . 225 |

| Table 11-23 CPOL1 Functionality                                                             | . 233 |

| Table 11-24 USI1 Register Map                                                               | .250  |

| Table 11-25 Examples of USI0BD and USI1BD Settings for Commonly Used Oscillator Frequencies | 259   |

| Table 11-26 LCD Register Map                                                                | . 268 |

| Table 12-1 Peripheral Operation during Power Down Mode                                      | . 272 |

| Table 12-2 Power Down Operation Register Map                                                | . 276 |

| Table 13-1 Reset State                                                                      | . 277 |

| Table 13-2 Boot Process Description                                                         | . 280 |

| Table 13-3 Reset Operation Register Map                                                     | . 284 |

| Table 15-1Flash Memory Register Map                                                         | . 295 |

|                                                                                             |       |

# MC96F6432

# CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER WITH 12-BIT A/D CONVERTER

#### 1. Overview

#### **1.1 Description**

The MC96F6432 is advanced CMOS 8-bit microcontroller with 32k bytes of FLASH. This is powerful microcontroller which provides a highly flexible and cost effective solution to many embedded control applications. This provides the following features : 32k bytes of FLASH, 256 bytes of IRAM, 768 bytes of XRAM, general purpose I/O, basic interval timer, watchdog timer, 8/16-bit timer/counter, 16-bit PPG output, 8-bit PWM output, 10-bit PWM output, watch timer, buzzer driving port, SPI, USI, 12-bit A/D converter, LCD driver, on-chip POR, LVR, LVI, on-chip oscillator and clock circuitry. The MC96F6432 also supports power saving modes to reduce power consumption.

| Device Name | FLASH     | XRAM      | IRAM      | ADC        | I/O PORT | Package |

|-------------|-----------|-----------|-----------|------------|----------|---------|

| MC96F6432Q  |           |           |           | 16 channel | 42       | 44 MQFP |

| MC96F6332D  | 32k bytes | 768 bytes | 256 bytes | 12 channel | 30       | 32 SOP  |

| MC96F6332M  |           |           |           | 11 channel | 26       | 28 SOP  |

#### 1.2 Features

- CPU

- 8 Bit CISC Core (8051 Compatible)

- ROM (FLASH) Capacity

- 32k Bytes

- Flash with self read/write capability

- On chip debug and In-system programming (ISP)

- Endurance : 100,000 times

- 256 Bytes IRAM

- 768 Bytes XRAM

- (27 Bytes including LCD display RAM)

- General Purpose I/O (GPIO)

- Normal I/O : 9 Ports (P0[2:0], P5[5:0])

- LCD shared I/O : 33 Ports (P0[7:3], P1, P2, P3, P4)

- Basic Interval Timer (BIT)

- 8Bit × 1ch

- Watch Dog Timer (WDT)

- 8Bit × 1ch

- 5kHz internal RC oscillator

- Timer/ Counter

- 8Bit × 1ch (T0), 16Bit × 2ch (T1/T2)

- 8Bit × 2ch (T3/T4) or 16 Bit × 1ch (T3)

- Programmable Pulse Generation

- Pulse generation (by T1/T2)

- 8Bit PWM (by T0)

- 6-ch 10Bit PWM for Motor (by T4)

- Watch Timer (WT)

- 3.91mS/0.25S/0.5S/1S/1M interval at 32.768kHz

- Buzzer

- 8Bit × 1ch

- SPI 2

- 8Bit × 1ch

- USI0/1 (UART + SPI + I2C)

- 8Bit UART × 2ch, 8Bit SPI × 2ch and I2C × 2ch

- 12 Bit A/D Converter

- 16 Input channels

- LCD Driver

- 21 Segments and 8 Common terminals

- Internal or external resistor bias

- 1/2, 1/3, 1/4, 1/5, 1/6 and 1/8 duty selectable

- Resistor Bias and 16-step contrast control

- Power On Reset

- Reset release level (1.4V)

- Low Voltage Reset

- 14 level detect (1.60V/ 2.00V/ 2.10V/ 2.20V/ 2.32V/ 2.44V/ 2.59V/ 2.75V/ 2.93V/ 3.14V/ 3.38V/ 3.67V/ 4.00V/ 4.40V)

- Low Voltage Indicator

- 13 level detect (2.00V/ 2.10V/ 2.20V/ 2.32V/ 2.44V/ 2.59V/ 2.75V/ 2.93V/ 3.14V/ 3.38V/ 3.67V/ 4.00V/ 4.40V)

- Interrupt Sources

- External Interrupts

(EXINT0~7, EINT8, EINT10, EINT11, EINT12)

(12)

- Timer(0/1/2/3/4) (5)

- WDT (1)

- BIT (1)

- WT (1)

- SPI 2 (1)

- USI0/1 (6)

- ADC (1)

- Internal RC Oscillator

- Inernal RC frequency: 16MHz ±0.5% (T<sub>A</sub>= 25°C)

- Power Down Mode

- STOP, IDLE mode

- Operating Voltage and Frequency

- 1.8V ~ 5.5V (@32 ~ 38kHz with X-tal)

- 1.8V ~ 5.5V (@0.4 ~ 4.2MHz with X-tal)

- 2.7V ~ 5.5V (@0.4 ~ 10.0MHz with X-tal)

- 3.0V ~ 5.5V (@0.4 ~ 12.0MHz with X-tal)

- 1.8V ~ 5.5V (@0.5 ~ 8.0MHz with Internal RC)

- 2.0V ~ 5.5V (@0.5 ~ 16.0MHz with Internal RC)

- Voltage dropout converter included for core

- Minimum Instruction Execution Time

- 125nS (@ 16MHz main clock)

- 61µS (@t 32.768kHz sub clock)

- Operating Temperature: -40 ~ + 85 ℃

- Oscillator Type

- 0.4-12MHz Crystal or Ceramic for main clock

- 32.768kHz Crystal for sub clock

- Package Type

- 44 MQFP-1010

- 32 SOP

- 28 SOP

- Pb-free package

# **1.3 Ordering Information**

### Table 1-1 Ordering Information of MC96F6432

| Device name | Device name ROM size |           | XRAM size | Package |

|-------------|----------------------|-----------|-----------|---------|

| MC96F6432Q  |                      |           |           | 44 MQFP |

| MC96F6332D  | 32k bytes FLASH      | 256 bytes | 768 bytes | 32 SOP  |

| MC96F6332M  |                      |           |           | 28 SOP  |

#### **1.4 Development Tools**

#### 1.4.1 Compiler

We do not provide the compiler. Please contact the third parties.

The core of MC96F6432 is Mentor 8051. And, device ROM size is smaller than 32k bytes. Developer can use all kinds of third party's standard 8051 compiler.

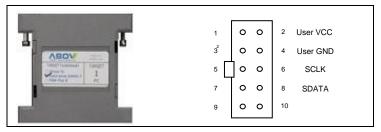

#### 1.4.2 OCD emulator and debugger

The OCD (On Chip Debug) emulator supports ABOV Semiconductor's 8051 series MCU emulation.

The OCD interface uses two-wire interfacing between PC and MCU which is attached to user's system. The OCD can read or change the value of MCU internal memory and I/O peripherals. And the OCD also controls MCU internal debugging logic, it means OCD controls emulation, step run, monitoring, etc.

The OCD Debugger program works on Microsoft-Windows NT, 2000, XP, Vista (32bit) operating system.

If you want to see more details, please refer to OCD debugger manual. You can download debugger S/W and manual from our web-site.

Connection:

- SCLK (MC96F6432 P01 port)

- SDATA (MC96F6432 P00 port)

OCD connector diagram: Connect OCD with user system

Figure 1.1 OCD Debugger and Pin Description

#### 1.4.3 Programmer

Single programmer:

PGMplus USB: It programs MCU device directly.

Figure 1.2 PGMplusUSB (Single Writer)

StandAlone PGMplus: It programs MCU device directly.

| Stand Alone PGM_Plus |  |

|----------------------|--|

|                      |  |

Figure 1.3 StandAlone PGMplus (Single Writer)

OCD emulator: It can write code in MCU device too, because OCD debugging supports ISP (In System Programming).

It does not require additional H/W, except developer's target system.

Gang programmer:

It programs 8 MCU devices at once.

So, it is mainly used in mass production line.

Gang programmer is standalone type, it means it does not require host PC, after a program is downloaded from host PC to Gang programmer.

Figure 1.4 StandAlone Gang8 (for Mass Production)

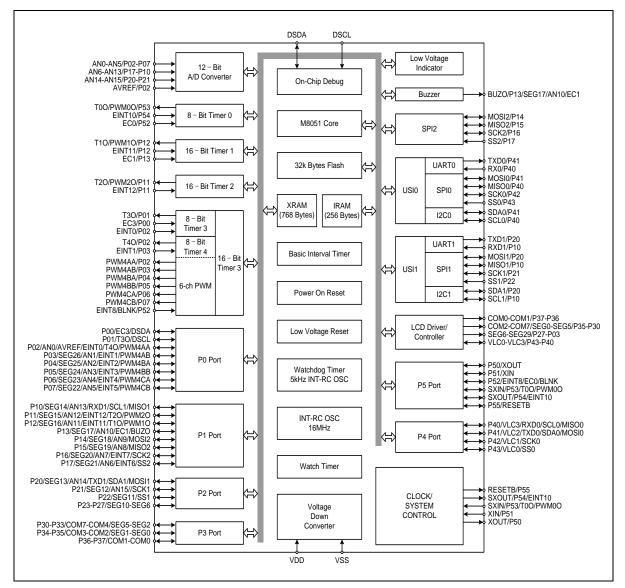

# 2. Block Diagram

#### Figure 2.1 Block Diagram

NOTES) 1. The P14–P17, P23–P25, P34–P37, and P43 are not in the 32-pin package. 2. The P13–P17, P22–P27, P34–P37, and P43 are not in the 28-pin package.

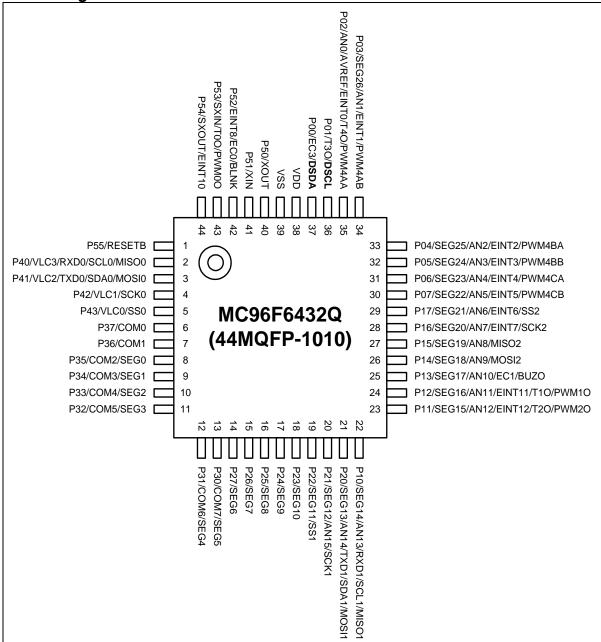

# 3. Pin Assignment

Figure 3.1 MC96F6432Q 44MQFP-1010 Pin Assignment

NOTE) On On-Chip Debugging, ISP uses P0[1:0] pin as DSDA, DSCL.

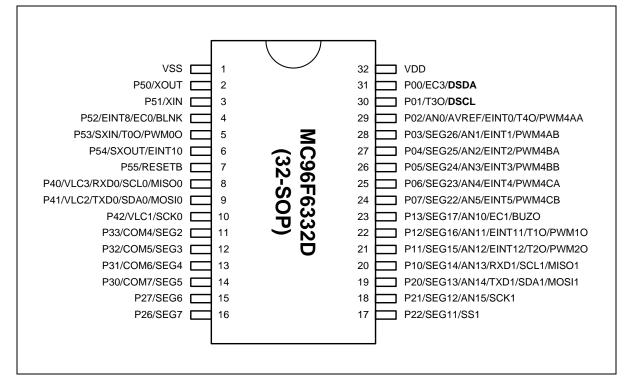

#### Figure 3.2 MC96F6332D 32SOP Pin Assignment

NOTES) 1. On On-Chip Debugging, ISP uses P0[1:0] pin as DSDA, DSCL.

2. The P14-P17, P23-P25, P34-P37 and P43 pins should be selected as a push-pull output or an input with pull-up resistor by software control when the 32-pin package is used.

#### Figure 3.3 MC96F6332M 28SOP Pin Assignment

NOTES) 1. On On-Chip Debugging, ISP uses P0[1:0] pin as DSDA, DSCL.

2. The P13-P17, P22-P27, P34-P37 and P43 pins should be selected as a push-pull output or an input with pull-up resistor by software control when the 32-pin package is used.

# 4. Package Diagram

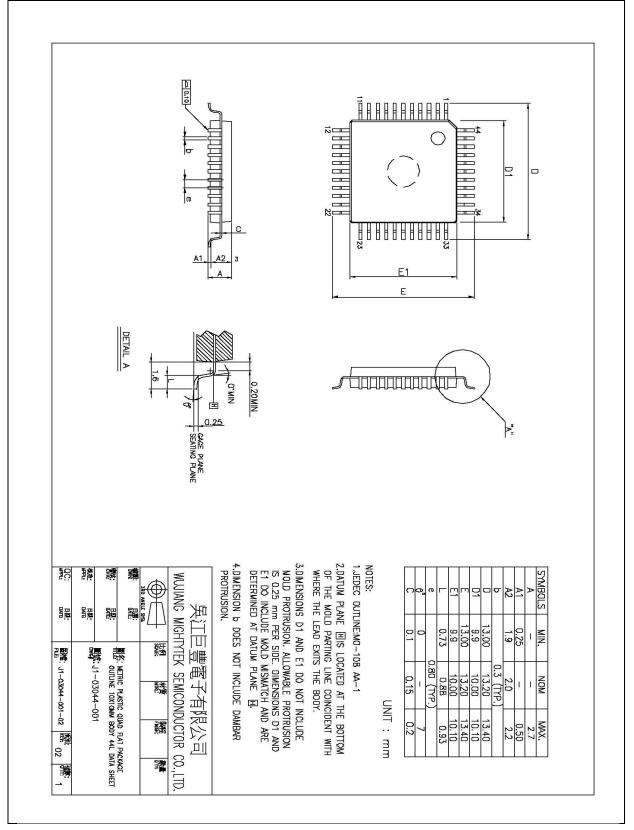

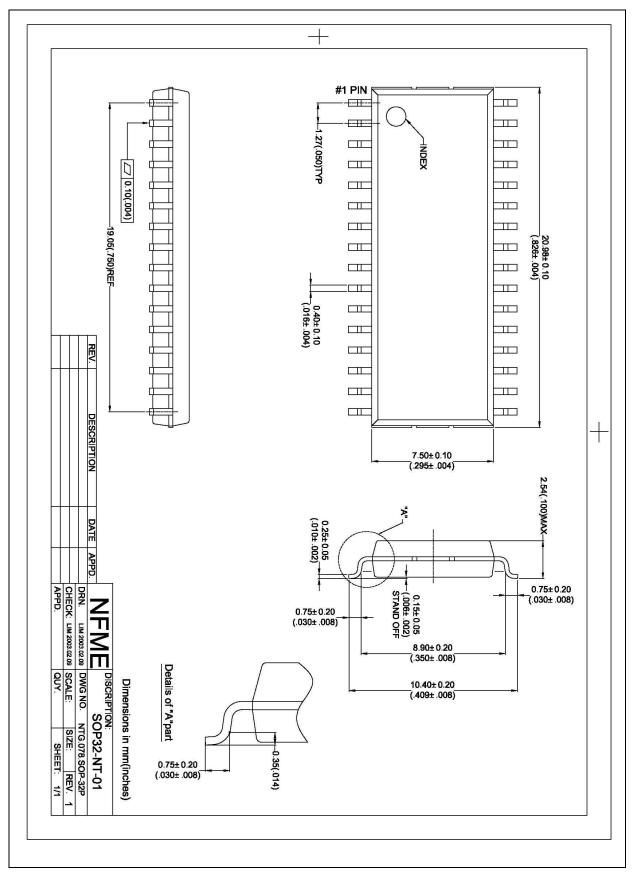

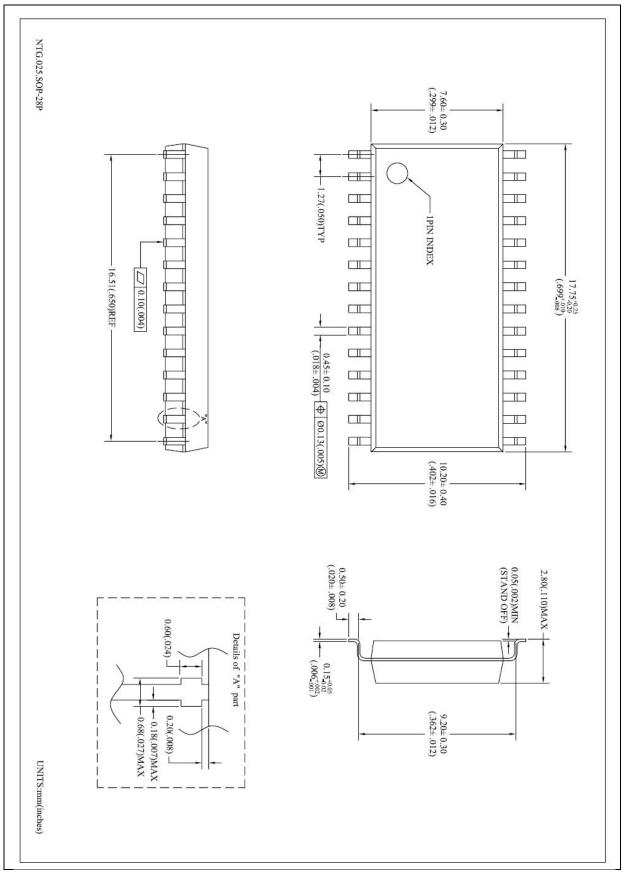

Figure 4.1 44-Pin MQFP Package

Figure 4.2 32-Pin SOP Package

Figure 4.3 28-Pin SOP Package

# 5. Pin Description

#### Table 5-1 Normal Pin Description

| PIN<br>Name | I/O | Function                                                                               | @RESET | Shared with                 |

|-------------|-----|----------------------------------------------------------------------------------------|--------|-----------------------------|

| P00         | I/O | Port 0 is a bit-programmable I/O port which can                                        | Input  | EC3/DSDA                    |

| P01         |     | be configured as a schmitt-trigger input, a                                            |        | T3O/DSCL                    |

| P02         |     | push-pull output, or an open-drain output.                                             |        | AN0/AVREF/EINT0/T4O/PWM4AA  |

| P03         |     | A pull-up resistor can be specified in 1-bit unit.                                     |        | SEG26/AN1/EINT1/PWM4AB      |

| P04         |     |                                                                                        |        | SEG25/AN2/EINT2/PWM4BA      |

| P05         |     |                                                                                        |        | SEG24/AN3/EINT3/PWM4BB      |

| P06         |     |                                                                                        |        | SEG23/AN4/EINT4/PWM4CA      |

| P07         |     |                                                                                        |        | SEG22/AN5/EINT5/PWM4CB      |

| P10         | I/O | Port 1 is a bit-programmable I/O port which can                                        | Input  | SEG14/AN13/RXD1/SCL1/MISO1  |

| P11         |     | be configured as a schmitt-trigger input, a push-pull output, or an open-drain output. |        | SEG15/AN12/EINT12/T2O/PWM2O |

| P12         |     | A pull-up resistor can be specified in 1-bit unit.                                     |        | SEG16/AN11/EINT11/T10/PWM10 |

| P13         |     | The P14 – P17 are not in the 32-pin package.                                           |        | SEG17/AN10/EC1/BUZO         |

| P14         |     | The P13 – P17 are not in the 28-pin package.                                           |        | SEG18/AN9/MOSI2             |

| P15         |     |                                                                                        |        | SEG19/AN8/MISO2             |

| P16         |     |                                                                                        |        | SEG20/AN7/EINT7/SCK2        |

| P17         |     |                                                                                        |        | SEG21/AN6/EINT6/SS2         |

| P20         | I/O | Port 2 is a bit-programmable I/O port which can                                        | Input  | SEG13/AN14/TXD1/SDA1/MOSI1  |

| P21         |     | be configured as an input, a push-pull output, or an open-drain output.                |        | SEG12/AN15/SCK1             |

| P22         |     | A pull-up resistor can be specified in 1-bit unit.                                     |        | SEG11/SS1                   |

| P23         |     | The P23 – P25 are not in the 32-pin package.                                           |        | SEG10                       |

| P24         |     | The P22 – P27 are not in the 28-pin package.                                           |        | SEG9                        |

| P25         |     |                                                                                        |        | SEG8                        |

| P26         |     |                                                                                        |        | SEG7                        |

| P27         |     |                                                                                        |        | SEG6                        |

| P30         | I/O | Port 3 is a bit-programmable I/O port which can                                        | Input  | COM7/SEG5                   |

| P31         |     | be configured as an input, a push-pull output.                                         |        | COM6/SEG4                   |

| P32         |     | A pull-up resistor can be specified in 1-bit unit.                                     |        | COM5/SEG3                   |

| P33         |     | The P34 – P37 are only in the 44-pin package.                                          |        | COM4/SEG2                   |

| P34         |     |                                                                                        |        | COM3/SEG1                   |

| P35         |     |                                                                                        |        | COM2/SEG0                   |