# セクション I. MAX II デバイス・ ファミリ・データシート

この資料は更新された最新の英語版が存在します。こちらの日本語版は参考用としてご利用ください。 設計の際には、最新の英語版で内容をご確認ください。

> このセクションでは、MAX® II デバイスのデータシートを提供します。 この章には、内部アーキテクチャの機能定義、Joint Test Action Group (JTAG)、およびイン・システム・プログラマビリティ (ISP) 情報、DC 動 作条件、AC タイミング・パラメータ、および MAX II デバイスのオー ダー情報が記載されています。

このセクションは、以下の章で構成されています。

- 第1章 概要

- 第2章 MAX II アーキテクチャ

- 第3章 JTAG およびイン・システム・プログラマビリティ

- 第4章 MAXIIデバイスのホット・ソケットおよびパワー・オン・ リセット

- 第5章 DC & スイッチング特性

- 第6章 参照および製品コード

Altera Corporation セクション I–1

# 改訂履歴

以下の表に、第1章から第6章までの改訂履歴を示します。

| 章 | 日付/バージョン     | 変更内容                                                          |

|---|--------------|---------------------------------------------------------------|

| 1 | 2005年6月 v1.3 | 表1のタイミング数値を更新。                                                |

|   | 2004年12月v1.2 | 表 1 のタイミング数値を更新。                                              |

|   | 2004年6月 v1.1 | 表1のタイミング数値を更新。                                                |

| 2 | 2004年12月v1.2 | ページ 2-15 に段落を追加。                                              |

|   | 2004年6月 v1.1 | CFM の頭文字を追加。図 2-19 を修正。                                       |

| 3 | 2004年12月v1.2 | ページ 3-5 から 3-8 のテキストを更新。                                      |

|   | 2004年6月 v1.1 | 図 3-1 を修正。CFM の頭文字を追加。                                        |

| 4 | 2004年12月v1.2 | パワー・アップ特性セクションの内容を追加。<br>図 4-5 を更新。                           |

|   | 2004年6月 v1.1 | 図 4-2 を修正。                                                    |

| 5 | 2004年12月v1.2 | タイミング表 5-2、5-4、5-12、および表 15-14 から<br>5-34 を更新。<br>表 5-31 は新規。 |

|   | 2004年6月 v1.1 | タイミング表 5-15 から 5-32 を更新。                                      |

| 6 | 2005年6月 v1.1 | 二重マーキングの項を削除。                                                 |

|   | 2004年3月v1.0  | 初回リリース                                                        |

セクション I–2 Altera Corporation

# 1. 概要

この資料は英語版を翻訳したもので、内容に相違が生じる場合には原文を優先します。こちらの日本語版は参考 用としてご利用ください。設計の際には、最新の英語版で内容をご確認ください。

MII51001-1.3

# はじめに

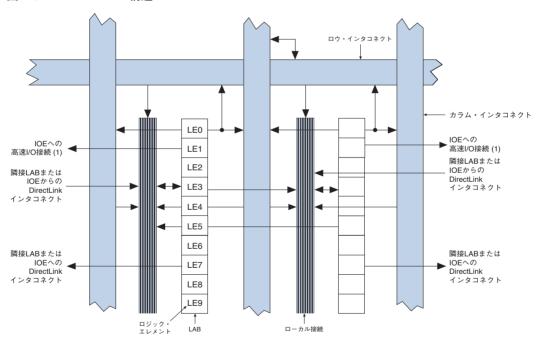

MAX®II インスタント・オン不揮発性 CPLD ファミリは、 $0.18 \, \mu m$ 、 $6 \, \bar{B}$  メタル・フラッシュ・プロセスをベースとし、 $240 \sim 2,210 \, \Box$  ロジック・エレメント(LE)( $128 \sim 2,210$  等価マクロセル数)の集積度と、8K ビットの不揮発性ストレージを備えています。 $MAX \, II$  デバイスは、9数の I/O、高速性能、および他の CPLD よりも信頼性の高いフィッティングを提供します。 $MAX \, II$  デバイスは、 $MultiVolt^{TM}$  コア、ユーザ・フラッシュ・メモリ(UFM) ブロック、および機能拡張されたイン・システム・プログラマビリティ(ISP)を備えており、バス・ブリッジ、I/O 拡張、パワー・オン・リセット(POR)、およびシーケンス・コントロール、デバイス・コンフィギュレーション・コントロールなどのアプリケーションに対するプログラマブルなソリューションを提供するとともに、コストや消費電力を低減します。

以下に、MAX II CPLD ファミリ・データシートの主なセクションを示します。

| セクション                                                                                                                       | ページ |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 特長                                                                                                                          | 1–2 |

| 機能の説明ロジック・アレイ・ブロックロジック・エレメント<br>ロジック・エレメント<br>MultiTrack インタコネクト<br>グローバル信号<br>ユーザ・フラッシュ・メモリ・ブロック<br>MultiVolt コア<br>I/O 構造 |     |

| IEEE Std.1149.1(JTAG)バウンダリ・ス・イン・システム・プログラマビリティ                                                                              |     |

| ホット・ソケット<br>パワー・オン・リセット回路                                                                                                   |     |

| 動作条件<br>消費電力<br>タイミング・モデルと仕様                                                                                                | 5–8 |

| デバイス・ピン配置<br>製品コード                                                                                                          |     |

# 特長

- 低コスト、低消費電力 CPLD

- インスタント・オン、不揮発性アーキテクチャ

- わずか2mAの待機時電流

- 高速伝播遅延および「Cock-to-Output」タイムを実現

- ロジック・アレイ・ブロック (LAB) ごとに 2 つのクロックを使用できる 4 つのグローバル・クロックを提供

- 不揮発性ストレージ用の最大8KビットUFMブロック

- 3.3 V/2.5 V または 1.8 V のデバイスへの外部電源電圧の供給を可能にする MultiVolt コア

- 3.3 V、2.5 V、1.8 V および 1.5 V のロジック・レベルをサポートする MultiVolt I/O インタフェース

- プログラマブル・スルー・レート、ドライブ強度、バス・ホールド、 およびプログラマブル・プルアップ抵抗など、バスを扱いやすいアー キテクチャ

- 耐ノイズ性に優れた入力を可能にするシュミット・トリガ (ピンごとにプログラム可能)

- 33 MHz での 3.3 V 動作を規定した PCI SIG(Peripheral Component Interconnect Special Interest Group)PCI Local Bus Specification、Revision 2.2 に完全準拠

- ホット・ソケットのサポート

- IEEE Std. 1149.1-1990 準拠の内蔵 JTAG(Joint Test Action Group)バウンダリ・スキャン・テスト(BST)回路

- IEEE Std. 1532 準拠の ISP 回路

表 1-1 に、MAX II デバイスの機能を示します。

| 表 1–1. MAX II デバイスの機能 (1/2) |           |           |             |               |  |  |  |  |  |

|-----------------------------|-----------|-----------|-------------|---------------|--|--|--|--|--|

| 機能                          | EPM240    | EPM570    | EPM1270     | EPM2210       |  |  |  |  |  |

| LE数                         | 240       | 570       | 1,270       | 2,210         |  |  |  |  |  |

| 標準等価マクロセル数                  | 192       | 440       | 980         | 1,700         |  |  |  |  |  |

| 等価マクロセルの範囲                  | 128 ~ 240 | 240 ~ 570 | 570 ~ 1,270 | 1,270 ~ 2,210 |  |  |  |  |  |

| UFM サイズ(ビット)                | 8,192     | 8,192     | 8,192       | 8,192         |  |  |  |  |  |

| 最大ユーザ I/O ピン数               | 80        | 160       | 212         | 272           |  |  |  |  |  |

| t <sub>PD1</sub> (ns) (1)   | 4.7       | 5.4       | 6.2         | 7.0           |  |  |  |  |  |

| f <sub>CNT</sub> (MHz) (2)  | 304       | 304       | 304         | 304           |  |  |  |  |  |

| t <sub>SU</sub> (ns)        | 1.7       | 1.2       | 1.2         | 1.2           |  |  |  |  |  |

| 表 1–1. MAX II デバイスの機能 (2/2)      |     |     |     |     |  |  |  |

|----------------------------------|-----|-----|-----|-----|--|--|--|

| 機能 EPM240 EPM570 EPM1270 EPM2210 |     |     |     |     |  |  |  |

| t <sub>CO</sub> (ns)             | 4.3 | 4.5 | 4.6 | 4.6 |  |  |  |

#### 表 1-1 の注:

- (1)  $t_{PDI}$  は、デバイスを対角線上に横切るパスを使用し、単一 LUT と出力ピンに隣接する LAB に組み合わせ ロジックを実装した、ワースト・ケースの I/O 配置に対するピン間遅延を表します。

- (2) 最大周波数は、クロック入力ピンに対する標準 I/O 規格によって制限されます。16 ビット・カウンタの クリティカル遅延は、この値よりも高速になります。

- 等価マクロセルの詳細については、「MAX II Logic Element to Macrocell Conversion Methodology」ホワイト・ペーパを参照してください。

MAX II デバイスは、-3 を最速とする -3、-4、-5 の 3 つのスピード・グレードで供給されます。これらのスピード・グレードは、全体的な相対性能を表すもので、特定のタイミング・パラメータを表すものであはありません。各スピード・グレードおよび集積度における伝播遅延タイミングの数値については、「DC およびスイッチング特性」の章を参照してください。表 1-2 に、MAX II デバイスのスピード・グレードを示します。

| 表 1–2. MAX II スピード・グレード |           |          |          |  |  |  |

|-------------------------|-----------|----------|----------|--|--|--|

| ニバノコ                    | スピード・グレード |          |          |  |  |  |

| デバイス                    | -3        | -4       | -5       |  |  |  |

| EPM240                  | √         | <b>V</b> | <b>V</b> |  |  |  |

| EPM570                  | √         | √        | √        |  |  |  |

| EPM1270                 | √         | √        | √        |  |  |  |

| EPM2210                 | √         | √        | √        |  |  |  |

MAX II デバイスは、省スペース型 FineLine BGA® および薄型クワッド・ フラット・パック (TOFP) パッケージで提供されます (表 1-3 および 1-4 を参照)。MAX II デバイスは、同じパッケージ・タイプでのバーティ カル・マイグレーションをサポートしています(例えば、256ピンFineLine BGA パッケージの EPM570、EPM1270、EPM2210 デバイス間でマイグ レーションが可能です)。バーティカル・マイグレーションとは、専用ピ ンおよび JTAG ピンが同じで、電源ピンが各デバイス集積度において、 特定のパッケージに対するサブセットまたはスーパセットとなるデバイ スにマイグレーションできることを意味します。どのパッケージでも、 集積度が最大のデバイスに最も多い電源ピンがあります。したがって、 マイグレーションに必要な電源ピンを提供するには、該当するパッケー ジの計画最大集積度に対応してレイアウトすることが必要です。異なる 集積度の間で I/O ピンをマイグレーションする場合は、特定のパッケー ジ・タイプに関して計画されるすべての集積度に対するピン配置を使用 して、利用可能な I/O ピンを相互参照することによって、どの I/O ピン がマイグレーション可能かを特定します。Quartus® II ソフトウェアは、 デバイス・マイグレーション・リストが指定されると、自動的に相互参 照を行ってすべてのピンをマイグレーションに対応させて配置します。

| 表 1-3. MAX II のパッケージおよびユーザ I/O ピン数                         |    |     |     |     |  |  |  |

|------------------------------------------------------------|----|-----|-----|-----|--|--|--|

| デバイス 100 ピン 144 ピン 256 ピン FineLine BGA 324 ピン FineLine BGA |    |     |     |     |  |  |  |

| EPM240                                                     | 80 |     |     |     |  |  |  |

| EPM570                                                     | 76 | 116 | 160 |     |  |  |  |

| EPM1270                                                    |    | 116 | 212 |     |  |  |  |

| EPM2210                                                    |    |     | 204 | 272 |  |  |  |

| 表 1–4. MAX II TQPF および FineLine BGA パッケージ・サイズ |             |                                                                 |         |         |  |  |  |  |  |

|-----------------------------------------------|-------------|-----------------------------------------------------------------|---------|---------|--|--|--|--|--|

| パッケージ                                         | 100 ピン TQFP | 100 ピン TQFP 144 ピン TQFP 256 ピン FineLine BGA 324 ピン FineLine BGA |         |         |  |  |  |  |  |

| ピッチ (mm)                                      | 0.5         | 0.5                                                             | 1       | 1       |  |  |  |  |  |

| 面積(mm²)                                       | 256         | 484                                                             | 289     | 361     |  |  |  |  |  |

| 長さ×幅 (mm×mm)                                  | 16 × 16     | 22 × 22                                                         | 17 × 17 | 19 × 19 |  |  |  |  |  |

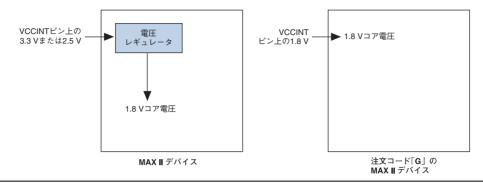

MAX II デバイスは、3.3 V または 2.5 V の外部電源電圧をサポートする内部リニア電圧レギュレータを備えており、電源電圧を 1.8 V の内部動作電圧に安定化します。MAX IIG デバイスは、1.8 V のみを外部電源電圧として受け入れます。表 1-5 に、MAX II ファミリがサポートする外部電源電圧を示します。

| 表 1–5. MAX II 外部電源電圧                               |                                        |                                            |  |  |  |  |  |

|----------------------------------------------------|----------------------------------------|--------------------------------------------|--|--|--|--|--|

| デバイス                                               | EPM240<br>EPM570<br>EPM1270<br>EPM2210 | EPM240G<br>EPM570G<br>EPM1270G<br>EPM2210G |  |  |  |  |  |

| MultiVolt コアの<br>外部電源電圧(V <sub>CCINT</sub> )(2)    | 3.3 V、2.5 V                            | 1.8 V                                      |  |  |  |  |  |

| MultiVolt I/Oインタフェースの<br>電圧レベル(V <sub>CCIO</sub> ) | 1.5 V、1.8 V、<br>2.5 V、3.3 V            | 1.5 V、1.8 V、<br>2.5 V、3.3 V                |  |  |  |  |  |

# 表 1-5 の注:

- (1) MAX II G デバイスは、内部電圧レギュレータを備えていないため、VCCINT ピンで 1.8 V のみ受け入れます。これらのデバイスの供給状況については、アルテラにお問い合わせください。

- (2) MAX II デバイスは内部では 1.8 V で動作します。

# 2. MAX II アーキテクチャ

この資料は更新された最新の英語版が存在します。こちらの日本語版は参考用としてご利用ください。 設計の際には、最新の英語版で内容をご確認ください。

MII51002-1.2

# 機能の説明

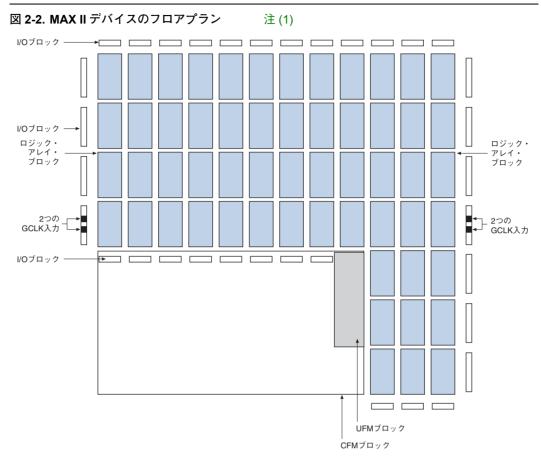

MAX®II デバイスは、カスタム・ロジックを実装する二次元のロウ / カラム・ベース・アーキテクチャを備えています。カラムおよびロウ・インタコネクトによって、ロジック・アレイ・ブロック(LAB)間での信号の相互接続が可能になります。

ロジック・アレイは、それぞれに 10 個のロジック・エレメント (LE) がある LAB によって構成されます。LE は、ユーザ・ロジック・ファンクションを効率的に実現する小さなロジックの単位です。LAB は、デバイス 全域に配置 された ロウとカラム にグループ 化されています。MultiTrackTM インタコネクトは、LAB 間に高速な精密タイミング遅延を提供します。インタコネクト構造はグローバルに配線されますが、追加ロジック・レベルに対するタイミング遅延は、LE 間の高速配線によって最小化されます。

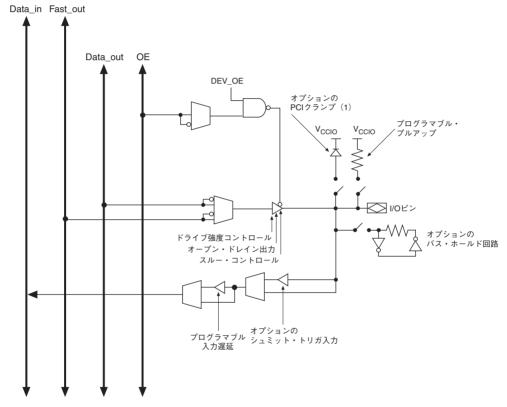

MAX II デバイスの I/O ピンには、デバイス周辺の LAB ロウおよびカラムの末端にある I/O エレメント (IOE) から信号が供給されます。各 IOE には、複数の高度な機能を備えた双方向 I/O バッファが内蔵されています。 I/O ピンは、シュミット・トリガ入力、および 33 MHz、32 ビット PCI、LVTTL などのさまざまなシングル・エンド規格をサポートしています。

MAXII デバイスはグローバル・クロック・ネットワークを提供しています。グローバル・クロック・ネットワークは、デバイス全体を通じてドライブする 4 本のグローバル・クロック・ラインで構成され、デバイス内部のすべてのリソースにクロックを供給します。グローバル・クロック・ラインは、クリア、プリセット、または出力イネーブルなどのコントロール信号に使用することもできます。

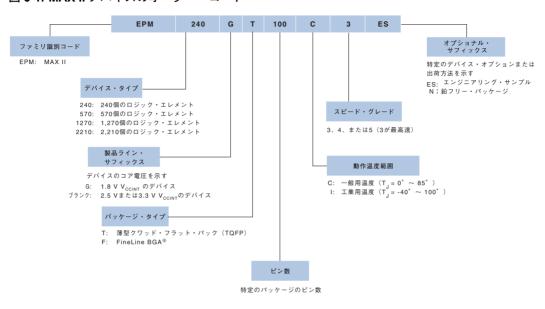

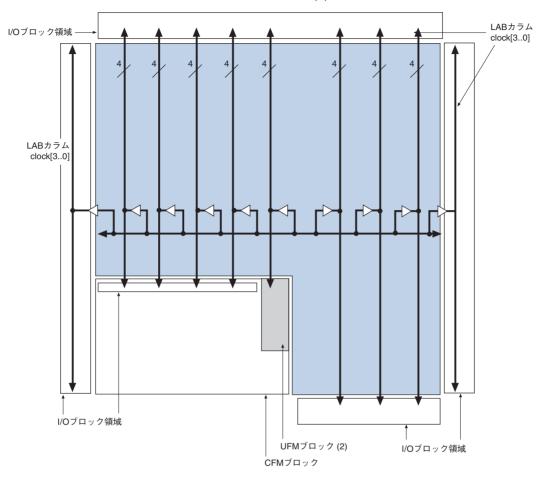

図 2-1 に MAX II デバイスの機能ブロック図を示します。

#### 図 2-1. MAX II デバイスのブロック図

各 MAX II デバイスは、フロアプラン内にフラッシュ・メモリ・ブロックを内蔵しています。EPM240 デバイスでは、このブロックはデバイスの左側に配置されています。EPM570、EPM1270、および EPM2210 デバイスの場合、フラッシュ・メモリ・ブロックはデバイスのボトム左側の領域に配置されています。このフラッシュ・メモリ・ストレージの大部分は、専用コンフィギュレーション・フラッシュ・メモリ(CFM) ブロックとして分割されます。CFM ブロックは、すべての SRAM コンフィギュレーション情報の不揮発性ストレージを提供します。CFM は、パワー・アップ時にロジックおよび I/O を自動的にダウンロードおよびコンフィギュレーションして、インスタント・オン動作を実現します。

パワー・アップ時のコンフィギュレーションの詳細については、「MAXII デバイスのホット・ソケットおよびパワー・オン・リセット」の章を参照してください。

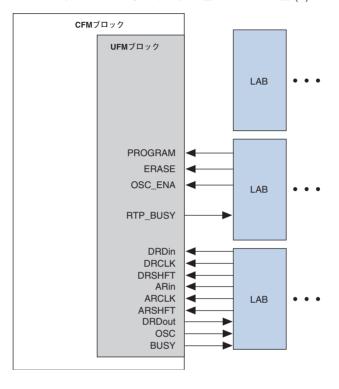

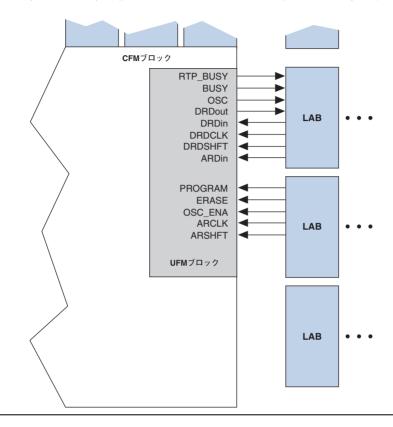

MAX II デバイス内部のフラッシュ・メモリの一部分は、ユーザ・データ用の小ブロックに分割されます。このユーザ・フラッシュ・メモリ (UFM) ブロックは、8,192 ビットの汎用ユーザ・ストレージになります。UFM は、読み出しおよび書き込み用にロジック・アレイへのプログラマブルなポート接続を提供します。このブロックには3つのLABロウが隣接していますが、カラム数はデバイスによって異なります。

表 2-1 に、各デバイスの LAB ロウおよびカラム数、EPM570、EPM1270、 および EPM2210 デバイスのフラッシュ・メモリ領域に隣接する LAB ロ ウおよびカラム数を示します。ロング LAB ロウは、ロウ I/O ブロック の一方のサイドから他方のサイドに延びる完全な LAB ロウです。ショー ト LAB ロウは、UFM ブロックに隣接する LAB ロウで、その長さは LAB カラム幅として示されます。

| 表 2-1. M | AX II ナハイスのり | ソース |  |

|----------|--------------|-----|--|

|          |              |     |  |

|         |           |          |                | LAB ロウ数                       |          |  |  |

|---------|-----------|----------|----------------|-------------------------------|----------|--|--|

| デバイス    | UFM ブロック数 | LAB カラム数 | ロング<br>LAB ロウ数 | ショート<br><b>LAB</b> ロウ(幅)数 (1) | 合計 LAB 数 |  |  |

| EPM240  | 1         | 6        | 4              | -                             | 24       |  |  |

| EPM570  | 1         | 12       | 4              | 3 (3)                         | 57       |  |  |

| EPM1270 | 1         | 16       | 7              | 3 (5)                         | 127      |  |  |

| EPM2210 | 1         | 20       | 10             | 3 (7)                         | 221      |  |  |

#### 表 2-1 の注:

(1) 幅は LAB カラム数を長さで示したものです。

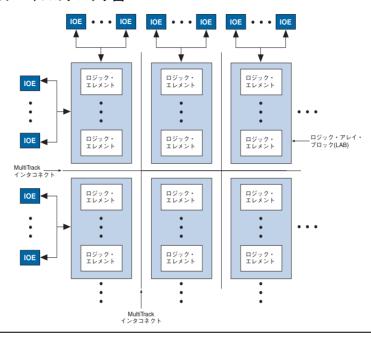

図 2-2 に MAX II デバイスのフロアプランを示します。

### 図 2-2 の注:

(1) ここに示すデバイスは、EPM570 デバイスです。EPM1270 および EPM2210 デバイスは、同様のフロアプランを備えていますがより多くの LAB で構成されます。EPM240 デバイスの場合、CFM および UFM ブロックは左に  $90^\circ$  回転してデバイスの左サイドをカバーします。

# ロジック・ アレイ・ ブロック

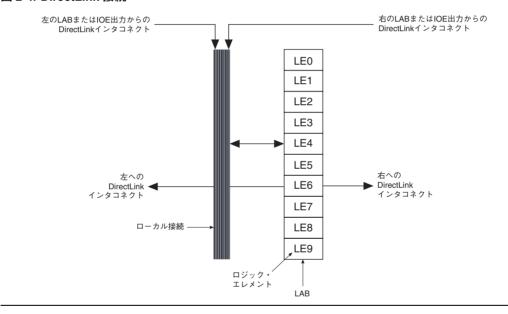

各 LAB は 10 個の LE、LE キャリー・チェイン、LAB コントロール信号、ローカル接続、ルック・アップ・テーブル(LUT)チェイン、およびレジスタ・チェイン接続ラインによって構成されています。1 つの LAB には 26 の固有入力が可能で、同じ LAB の LE 出力からさらに 10 本のローカル・フィードバック入力ラインが供給されます。ローカル接続は、同一 LAB 内で LE 間の信号を転送します。LUT チェイン接続は、1 つの LE の LUT 出力を隣接する LE に転送し、同じ LAB 内で高速シーケンシャル LUT 接続を実現します。レジスタ・チェイン接続は、1 つの LE のレジスタ出力をLAB内で隣接するLEのレジスタに転送します。Quartus® II 開発ソフトウェアは、LAB または隣接 LAB 内に関連ロジックを配置し、ローカル接続、LUT チェイン接続、およびレジスタ・チェイン接続の使用を可能にして、性能と面積効率を向上させます。図 2-3 に MAX II LABを示します。

#### 図 2-3. MAX II の LAB 構造

#### 図 2-3 の注:

(1) IOE に隣接する LAB からのみ。

### LAB インタコネクト

LAB ローカル接続は、同一 LAB 内の LE をドライブできます。LAB ローカル接続は、同一 LAB 内のカラムとロウのインタコネクトおよび LE 出力によってドライブされます。また、左側および右側で隣接する LAB は、DirectLink 接続を介して LAB のローカル接続をドライブできます。この DirectLink 接続機能によって、ロウおよびカラム・インタコネクトの使用量が最小限ですむため、さらに性能と柔軟性が向上します。各 LE は、高速ローカル接続および DirectLink 接続を介して、他の 30 個の LE をドライブすることができます。図 2-4 に DirectLink 接続を示します。

#### 図 2-4. DirectLink 接続

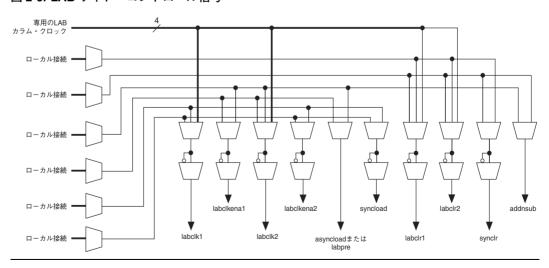

# LAB コントロール信号

各 LAB には、LE にコントロール信号をドライブするための専用ロジックが内蔵されています。このコントロール信号には、2 つのクロック、2 つのクロック・イネーブル、2 つの非同期クリア、同期クリア、非同期プリセット / ロード、同期ロード、および加算 / 減算の各コントロール信号が含まれ、最大 10 個のコントロール信号を同時に供給します。一般に同期ロード信号および同期クリア信号は、カウンタを実装する際に使用されますが、他のファンクションでも使用することができます。

各 LAB では、2 つのクロック信号と2 つのクロック・イネーブル信号を使用することができます。各 LAB のクロック信号とクロック・イネーブル信号はリンクされています。例えば、1abc1k1 信号を使用する特定のLAB の LE は、1abc1kena1 信号も使用します。クロックの立ち上がりと立ち下がりの双方のエッジを LAB 内で使用する場合、LAB ワイドの双方のクロック信号を2 つとも使用します。クロック・イネーブル信号がデアサートされると、LAB ワイドのクロック信号はオフになります。

各 LAB は 2 つの非同期クリア信号と 1 つの非同期ロード / プリセット信号を使用できます。非同期ロード信号は、非同期ロード・データ入力が High に接続されるとプリセットとして機能します。

LAB ワイドの addnsub コントロール信号により、1 つの LE で1 ビット 加算器および減算器を構成できます。これにより、LE リソースが節約され、相関器やデータに応じて加算と減算を切り替える符号付き乗算器などのロジック・ファンクションの性能が向上します。

グローバル・クロック・ネットワークによってドライブされる LAB カラム・クロック [3..0]、および LAB ローカル接続は、LAB ワイド・コントロール信号を生成します。MultiTrack 配線構造は、非グローバル・コントロール信号を生成するための LAB ローカル接続をドライブします。MultiTrack インタコネクトは本質的に低スキューなため、データの他にもクロックとコントロール信号を分配できます。図 2-5 に LAB コントロール信号の生成回路を示します。

#### 図 2-5. LAB ワイド・コントロール信号

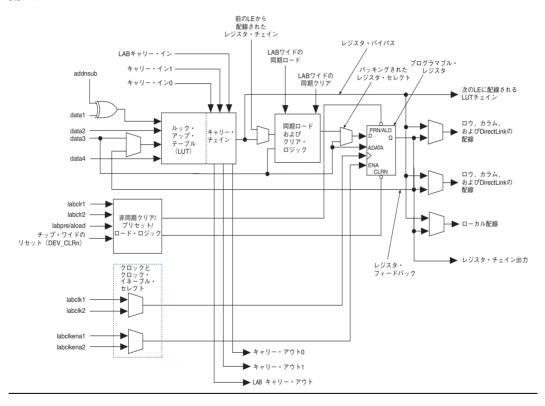

# ロジック・エレメント

MAX II アーキテクチャのロジックの最小単位である LE はコンパクトであり、ロジックを効率的に利用しながら高度な機能を提供します。各 LE には、4 入力 LUT、つまり 4 変数からなる任意の機能を実装できるファンクション・ジェネレータが搭載されています。さらに、各 LE にはプログラマブル・レジスタ、およびキャリー選択機能を備えたキャリー・チェインも内蔵されています。また、1 つの LE で、LAB ワイド・コントロール信号により選択可能なダイナミック・シングル・ビット加算または減算モードもサポートします。各 LE は、すべてのタイプのインタコネクト(ローカル、ロウ、カラム、LUT チェイン、レジスタ・チェイン、DirectLinkインタコネクト)をドライブします。図 2-6 を参照してください。

#### 図 2-6. MAX II LE

各 LE のプログラマブル・レジスタは、D、T、JK、または SR 動作にコンフィギュレーションできます。各レジスタには、データ、真の非同期ロード・データ、クロック、クロック・イネーブル、クリア、および非同期ロード / プリセット入力があります。グローバル信号、汎用 I/O ピン、または任意の LE によって、レジスタのクロック・コントロール信号とクリア・コントロール信号をドライブできます。汎用 I/O ピンまたは LE のいずれかによって、クロック・イネーブル、プリセット、非同期ロード、および非同期データをドライブできます。非同期ロード・データ入力は、LE の data3 入力から供給されます。組み合わせファンクションを実現するときには、LUT 出力はレジスタをバイパスし、LE 出力に直接ドライブします。

各 LE には、ローカル、ロウ、およびカラム配線リソースをドライブする3つの出力があります。LUT またはレジスタ出力は、これらの3つの出力を個別にドライブできます。2つの LE 出力がカラムまたはロウ、およびDirectLink配線接続をドライブし、1つの出力がローカル接続リソースをドライブします。これにより、レジスタがある出力をドライブしている状態で、LUT が別の出力をドライブすることが可能になります。このレジスタ・パッキング機能によって、デバイスはレジスタと LUT を別々の機能に使用できるため、デバイスの稼働率が向上します。別の特殊パッキング・モードでは、レジスタ出力を同じ LE の LUT にフィードバックさせて、レジスタを自身のファンアウト LUT とパッキングできます。これにより、フィッティング機能を向上させる別のメカニズムが実現します。また、LE はラッチされた出力およびラッチされていない出力の両方の LUT 出力もドライブ・アウト可能です。

# LUT チェインとレジスタ・チェイン

3つの一般配線出力に加えて、LAB内のLEにはLUTチェイン出力およびレジスタ・チェイン出力があります。LUTチェイン接続により、同一LAB内のLUTをカスケード接続して広範な入力ファンクションを実現できます。レジスタ・チェイン出力により、同一LAB内のレジスタをカスケード接続できます。レジスタ・チェイン出力により、LABはLUTを1つの組み合わせファンクションに使用したり、レジスタを別のシフト・レジスタの実装に使用することができます。これらのリソースはLAB間の接続を高速化し、同時にローカル接続リソースの節約を図ります。LUTチェイン接続およびレジスタ・チェイン接続の詳細については、2-16ページの「MultiTrackインタコネクト」を参照してください。

### addnsub 信号

LE のダイナミック加算器 / 減算器機能は、1組の LE を使用して加算器と減算器の両方を実装するため、ロジック・リソースが節約されます。この機能は、LAB ワイド・コントロール信号 addnsub によって制御されます。addnsub 信号は、A+B または A-B を実行するように LAB を設定します。LUT は加算を実行します。減算は、減算器の 2 の補数を加算して計算されます。LAB ワイドの信号は、LAB 内で B ビットを反転し、キャリー・インを 1 に設定して、最下位ビット (LSB) に 1 を加算して 2 の補数に変換されます。加算器 / 減算器の LSB は、LAB の最初の LE に配置しなければなりません。ここで、LAB ワイドの addnsub 信号が自動的にキャリー・インを 1 に設定します。Quartus II コンパイラは、加算器 / 減算器のパラメータ化機能を使用するときに、加算器 / 減算器 機能を自動的に配置して使用します。

### LE の動作モード

MAXIIのLEは、以下のいずれかのモードで動作します。

- ノーマル・モード

- ダイナミック演算モード

各モードでは、LE のリソースがそれぞれ異なる形で使用されます。各モードで、8つのLEへの入力、つまりLABローカル接続からの4つのデータ入力、前のLEからのcarry-in0 およびcarry-in1、前のキャリー・チェインLABからのLABキャリー・イン、そしてレジスタ・チェイン接続が異なるデスティネーションに転送され、目的のロジック機能が実装されます。LABワイドの信号として供給可能なものは、レジスタへのクロック、非同期クリア、非同期プリセット/ロード、同期クリア、同期ロード、およびクロック・イネーブル・コントロールの各信号です。このようなLABワイドの信号は、すべてのLEモードで使用できます。addnsubコントロール信号は演算モードで使用できます。

Quartus II 開発ソフトウェアは、LPM (Library of Parameterized Modules) などのパラメータ化されたファンクションと併用することによって、カウンタ、加算器、減算器、および演算ファンクションなどの一般的なファンクションに対して適切なモードを自動的に選択します。

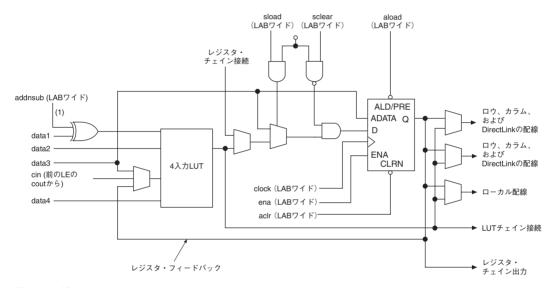

### ノーマル・モード

ノーマル・モードは、汎用ロジック・アプリケーションや組み合わせファンクションに適しています。ノーマル・モードでは、LAB ローカル接続からの4つのデータ入力が4入力 LUT の入力になります(図 2-7 を参照)。Quartus II コンパイラは、キャリー・インと data3 信号のいずれかを LUTへの入力として自動的に選択します。各 LE は、LUT チェイン接続を使用して、組み合わせ出力から LAB 内の次の LE を直接ドライブできます。レジスタの非同期ロード・データは、LE の data3 入力から供給されます。ノーマル・モードの LE は、パッキングされたレジスタをサポートします。

#### 図 2-7. ノーマル・モードの LE

#### 図 2-7 の注:

(1) LE が加算器 / 減算器チェインの最終段にある場合、この信号はノーマル・モードでのみ使用可能です。

### ダイナミック演算モード

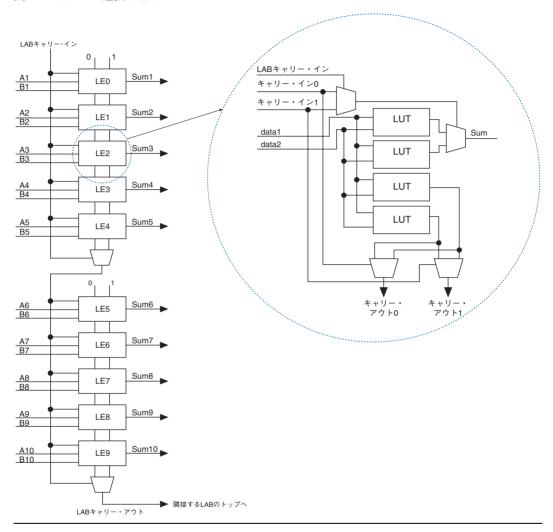

ダイナミック演算モードは、加算器、カウンタ、アキュムレータ、幅広いパリティ・ファンクション、およびコンパレータの実装に最適です。ダイナミック演算モードのLEは、ダイナミック加算器 / 減算器としてコンフィギュレーション可能な 2 入力 LUT を 4 個使用します。最初の 2 個の 2 入力 LUT は、1 または 0 のいずれかのキャリー・インに基づいて 2 つの和を計算し、他の 2 個の LUT は、キャリー選択回路の 2 つのチェインに対してキャリー出力を生成します。図 2-8 に示すように、LAB キャリー・イン信号は、carry-in0 または carry-in1 チェインのいずれかを選択します。選択されたチェインのロジック・レベルによって、どのパラレル合計を組み合わせ出力またはレジスタ出力として生成するかが決まります。例えば、加算器を実装する場合、合計出力は次の 2 とおりの計算合計を選択したものです。

data1 + data2 + carry in0

または

data1 + data2 + carry-in1

他の2つのLUT は、data1 および data2 信号を使用して、carry 1 に対するキャリー・アウト信号と carry 0 に対するキャリー・アウト信号の2つのキャリー・アウト信号を生成します。carry-in0 信号は carry-out0出力のキャリー選択として機能し、carry-in1信号はcarry-out1出力のキャリー選択として機能します。また、演算モードのLE はラッチされた出力、またはラッチされていない出力のいずれの LUT 出力もドライブ・アウト可能です。

ダイナミック演算モードでは、クロック・イネーブル、カウンタ・イネーブル、同期アップ / ダウン・コントロールの各信号と、同期クリア、同期ロード、およびダイナミック加算器 / 減算器のオプション信号も提供されています。カウンタ・イネーブルと同期アップ / ダウン・コントロール信号は、LABローカル接続からのデータ入力により生成されます。同期クリアと同期ロードのオプション信号は、LABワイドの信号であるため、LAB内のすべてのレジスタに影響を与えます。Quartus II 開発ソフトウェアは、カウンタに使用されていないレジスタを自動的に他のLABに配置します。LABワイドの信号 addnsub は、LE が加算器として動作するか、または減算器として動作するかを制御します。

#### IABキャリー・イン -キャリー・イン0 -(LABワイド) (LABワイド) (LABワイド) キャリー・イン1・ レジスタ・ addnsub チェイン接続 (LABワイド) ALD/PRE data1 ロウ、カラム、 および data2 ADATA O data3 D DirectLinkの配線 LUT ロウ、カラム ENA CLRN DirectLinkの配線 clock (LABワイド)・ LUT ena (LABワイド)・ - ローカル配線 aclr (LABワイド): LUT ■ IIITチェイン接続 レジスタ・ チェイン出力 レジスタ・フィードバック

#### 図 2-8. ダイナミック演算モードの LE

#### 図 2-8 の注:

(1) addnsub 信号は、キャリー・チェインの最初の LE でのみキャリー入力に接続されます。

アウト0

### キャリー選択チェイン

ダイナミック演算モードにおいて、キャリー選択チェインは、LE 間でのキャリー選択ファンクションを大幅に高速化します。キャリー選択チェインは、冗長キャリー計算を使用してキャリー・ファンクションを高速化します。LE は、0 のキャリー・インと1 のキャリー・インの出力を並列に計算するようにコンフィギュレーションされています。下位のビットからのcarry-in0 と carry-in1 信号は、パラレル・キャリー・チェインを介して上位ビットに転送され、LUT とキャリー・チェインの次の部分の両方に入力されます。キャリー選択チェインは LAB 内のどの LE からでも開始できます。

キャリー選択チェインの速度面での利点は、キャリー・チェインを事前に並列計算することにあります。LAB キャリー・インは事前に計算されたキャリー・チェインを選択するため、すべてのLE がクリティカル・パスに含まれるわけではありません。LAB キャリー・イン生成(LE5 およびLE10)の間の伝播遅延のみが、クリティカル・パスの一部となっています。この機能により、MAXII アーキテクチャはカウンタ、加算器、乗算器、パリティ・ファンクション、および任意の入力幅のコンパレータを高速で実行することができます。

図2-9に、10ビットの全加算器を使用した場合のLABにおけるキャリー選択回路を示します。LUTの一部は、入力信号と適切なキャリー・イン・ビットを使用して2ビットの加算を行い、この結果はLEの出力に送信されます。レジスタは、単純な加算器を構成する場合にはバイパスすることができ、アキュムレータ機能に使用することもできます。LUTの他の部分はキャリー・アウト・ビットを生成します。LABワイドのキャリー・イン・ビットは、特定の入力に対する加算処理でどのチェインを使用するかを選択します。各チェインのキャリー・イン信号、carry-in0またはcarry-in1は、次の上位ビットのキャリー・アウト信号はLEに接続され、そこでローカル、ロウ、カラムのいずれかのインタコネクトに供給されます。

#### 図 2-9. キャリー選択チェイン

キャリー・チェイン・ロジックは、デザイン処理中に Quartus II 開発ソフトウェアが自動的に作成しますが、設計者がデザインの入力時に手動で作成することもできます。LPM ファンクションなどのパラメータ化されたファンクションは、キャリー・チェインの利点を自動的に活用して、適切な機能を実現します。Quartus II 開発ソフトウェアは、同じロウ内の隣接する複数の LAB を自動的にリンクさせることにより、10 個以上のLE で構成される長いキャリー・チェインを作成します。キャリー・チェインは、1 つの LAB ロウ全体まで水平に拡張できますが、LAB ロウの間で拡張することはできません。

### クリアおよびプリセット・ロジック・コントロール

レジスタのクリアとプリセットの信号を実現するロジックは、LABワイド信号によって制御されます。LE は非同期クリアおよびプリセット機能を直接サポートします。レジスタのプリセットは、非同期ロードをロジック High レベルにすることによって達成されます。直接入力の非同期プリセットでは、NOT ゲート・プッシュバックを使用したテクニックは必要ありません。MAX II デバイスは、同時プリセット / 非同期ロードおよびクリア信号をサポートします。両方の信号が同時にアサートされた場合は、非同期クリア信号が優先されます。各 LAB は最大 2 つのクリア信号と 1 つのプリセット信号をサポートします。

MAX II デバイスは、クリアとプリセット・ポートのほかに、デバイス内のすべてのレジスタをリセットするチップ・ワイドのリセット・ピン(DEV\_CLRn)を備えています。このピンは、Quartus II 開発ソフトウェアでコンパイルを行う前に設定されたオプションによって制御されます。このチップ・ワイドのリセット信号は、他のすべてのコントロール信号よりも優先され、専用の配線リソースを使用します(つまり、4つのグローバル・リソースのいずれも使用しません)。パワー・アップ前またはパワー・アップ中にこの信号をLowにドライブすると、デザイン内でクリアが解放されません。これによって、パワー・アップ直後にデバイスでクリアが解放されるタイミングを制御できます。DEV\_CLRn ピンは、チップ・ワイドのリセット機能に設定されていない場合は、通常のI/O ピンになります。

パワー・アップ時に、MAX II デバイスの各レジスタは High または Low 状態のいずれかに設定できます。このパワー・アップ・ステートは、デザイン入力時に指定されます。デフォルトでは、すべてのレジスタがパワー・アップ時に Low に設定されます。

# MultiTrack インタコネクト

MAX II アーキテクチャでは、LE、UFM、およびデバイス I/O ピン間は、MultiTrack 配線構造によって接続されます。MultiTrack インタコネクトは、デザイン・ブロック間およびデザイン・ブロック内の接続に使用される、性能が最適化された連続配線ラインによって構成されます。Quartus II のコンパイラは、デザインのクリティカル・パスを自動的に高速ラインに配置して、デザイン・パフォーマンスを向上させます。

MultiTrack インタコネクトは、一定間隔で配置されたロウとカラムのインタコネクトで構成されています。この配線構造では、リソースの長さはすべてのデバイスに対して一定になるため、グローバル・ラインや長い配線ラインに見られる大きな遅延を生じることはなく、ロジック・レベル間の遅延は予測可能な小さなものになります。専用のロウ・インタコネクトは、同一ロウ内の LAB との間で入出力される信号を配線します。これらのロウのリソースには以下のものがあります。

- LAB 間の DirectLink 接続

- 4つの LAB を右または左に横断する R4 インタコネクト

DirectLink 接続によって、LAB は左または右に隣接するローカル接続をドライブできます。DirectLink 接続は、ロウ・インタコネクトの配線リソースを使用することなく、隣接する LAB やブロック間での高速通信を実現します。

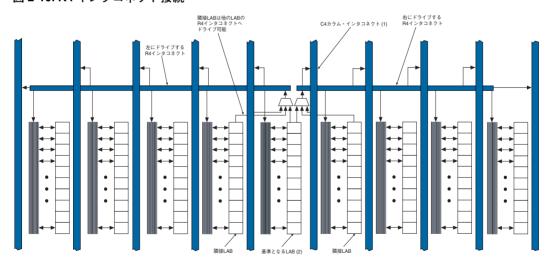

R4 インタコネクトは、4つの LAB にまたがる長さとなり、4つの LAB 領域内の高速ロウ接続に使用されます。どの LAB にも、左側または右側のいずれかにドライブする独自の R4 インタコネクトがあります。図 2-10 に LAB からの R4 インタコネクト接続を示します。R4 インタコネクトはロウ IOE をドライブでき、またロウ IOE からドライブすることができます。LAB インタフェースの場合、基準となる LAB または隣接する水平方向の LAB が、所定の R4 インタコネクトをドライブできます。右にドライブする R4 インタコネクトの場合、基準となる LAB および右の隣接 LAB がインタコネクトをドライブできます。左にドライブする R4 インタコネクトをドライブできます。方にドライブする R4 インタコネクトをドライブできます。R4 インタコネクトは、他の R4 インタコネクトをドライブすることにより、ドライブ可能な LAB の範囲を拡張することができます。R4 インタコネクトは、1 つのロウを別のロウに接続するときに C4 インタコネクトをドライブすることも可能です。

### 図 2-10. R4 インタコネクト接続

#### 図 2-10 の注:

- (1) C4 インタコネクトは R4 インタコネクトをドライブできます。

- (2) このパターンは、LABロウ内の各LABに対して繰り返されています。

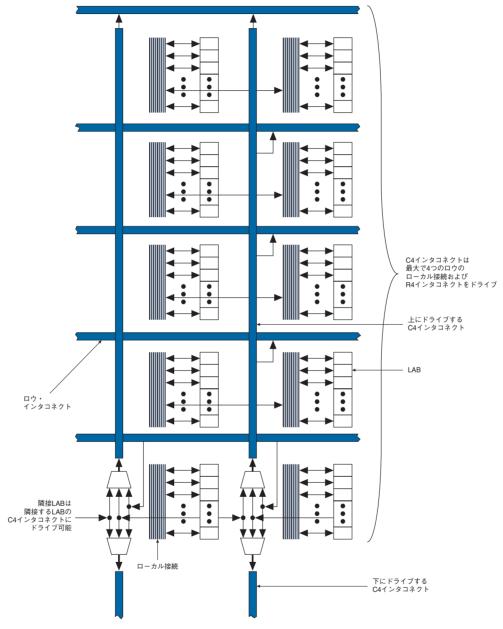

カラム・インタコネクトは、ロウ・インタコネクトと同様に動作します。 LAB の各カラムには、LAB とロウおよびカラム IOE に入出力する信号 を垂直に配線する専用のカラム・インタコネクトが使用されます。これ らのカラムのリソースには以下のものがあります。

- LAB内の LUT チェイン・インタコネクト

- LAB内のレジスタ・チェイン・インタコネクト

- 4つのLABの距離を上下方向に横断するC4インタコネクト

MAX II デバイスは、LAB内に拡張されたインタコネクト構造を搭載し、LUT チェイン接続およびレジスタ・チェイン接続を使用して、LE 出力から LE 入力への配線を高速化しています。LUT チェイン接続では、LE の組み合わせ出力がローカル接続をバイパスして、直下の LE の高速入力を直接ドライブします。これらのリソースは、同一 LAB内の LE 1から LE 10へのワイドなファン・イン機能を高速接続するのに使用できます。レジスタ・チェイン接続により、1 つの LE のレジスタ出力を LAB内の次の LE のレジスタ入力に直接接続し、高速シフト・レジスタを実現できます。Quartus II コンパイラは、自動的にこれらのリソースを活用して、利用率とパフォーマンスを向上させます。図 2-11 に LUT チェインおよびレジスタ・チェインのインタコネクトを示します。

### 図 2-11. LUT チェインおよびレジスタ・チェインのインタコネクト

C4 インタコネクトは、ソース LAB の上または下にある、4 つの LAB に対応した長さの配線ラインとなっています。各 LAB には、上または下にドライブする独自の C4 インタコネクトがあります。図 2-12 に、あるカラムの LAB からの C4 インタコネクト接続を示します。C4 インタコネクトは、カラムおよびロウ IOE をドライブでき、またカラムおよびロウ IOE からドライブすることができます。LAB インタコネクトの場合、基準となる LAB または隣接する垂直方向の LAB が C4 インタコネクトをドライブできます。C4 インタコネクトは、ロウ・インタコネクトをドライブしてカラム間接続を実現するだけでなく、互いをドライブして範囲を拡張することもできます。

# 図 2-12. C4 インタコネクト接続 注 (1)

### 図 2-12 の注:

(1) 各 C4 インタコネクトは、上または下にある 4 つのロウをドライブできます。

UFM ブロックは、LAB 間のインタフェースに類似したロジック・アレイと通信します。UFM ブロックは、ロウおよびカラム・インタコネクトに接続し、ロウおよびカラム・インタコネクトによってドライブされるローカル接続領域を備えています。このブロックは隣接する LAB との間で高速接続を実現する DirectLink 接続も提供しています。ロジック・アレイへの UFM インタフェースの詳細については、2-24 ページの「ユーザ・フラッシュ・メモリ・ブロック」を参照してください。

表 2-2 に MAX II デバイスの配線図を示します。

| 表 2–2. N         | 表 2–2. MAX II デバイスの配線図 |               |             |                    |               |          |          |                    |            |           |               |

|------------------|------------------------|---------------|-------------|--------------------|---------------|----------|----------|--------------------|------------|-----------|---------------|

| ソース              |                        | デスティネーション     |             |                    |               |          |          |                    |            |           |               |

|                  | LUT<br>チェイン            | レジスタ・<br>チェイン | ローカル<br>(1) | Direct<br>Link (1) | <b>R4</b> (1) |          | LE       | <b>UFM</b><br>ブロック | カラム<br>IOE | ロウ<br>IOE | 高速<br>I/O (1) |

| LUT<br>チェイン      |                        |               |             |                    |               |          | 1        |                    |            |           |               |

| レジスタ・<br>チェイン    |                        |               |             |                    |               |          | √        |                    |            |           |               |

| ローカル<br>接続       |                        |               |             |                    |               |          | <b>√</b> | 1                  | ٧          | 1         |               |

| DirectLink<br>接続 |                        |               | ٧           |                    |               |          |          |                    |            |           |               |

| R4インタ<br>コネクト    |                        |               | ٧           |                    | <b>√</b>      | <b>√</b> |          |                    |            |           |               |

| C4インタ<br>コネクト    |                        |               | ٧           |                    | <b>V</b>      | <b>V</b> |          |                    |            |           |               |

| LE               | √                      | 1             | <b>V</b>    | <b>√</b>           | 1             | 1        |          |                    | 1          | √         | <b>√</b>      |

| UFM<br>ブロック      |                        |               | 1           | <b>√</b>           | 7             | 7        |          |                    |            |           |               |

| カラム<br>IOE       |                        |               |             |                    |               | <b>√</b> |          |                    |            |           |               |

| ロウ IOE           |                        |               |             | <b>V</b>           | 1             | 1        |          |                    |            |           |               |

### 表 2-2 の注:

(1) これらのカテゴリはインタコネクトです。

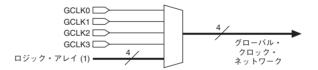

# グローバル 信号

各 MAX II デバイスは、図 2-13 に示すように、グローバル・クロック・ネットワークをクロッキングのためにドライブする 4 本の兼用クロック・ピン (GCLK[3..0]、左サイドの 2 本のピンと右サイドの 2 本のピン) を備えています。これらの 4 本のピンは、グローバル・クロック・ネットワークのドライブに使用しない場合は、汎用 I/O として使用することもできます。

グローバル・クロック・ネットワーク内の 4 本のグローバル・クロック・ラインが、デバイス全体をドライブします。グローバル・クロック・ネットワークは、LE、LAB ローカル接続、IOE、UFM ブロックなど、デバイス内のすべてのリソースにクロックを提供できます。また、グローバル・クロック・ラインは、クロック・イネーブル、同期または非同期クリア、プリセット、出力イネーブル、または PCI 用の TRDY や IRDY などのプロトコル・コントロール信号など、グローバル・コントロール信号用に使用することも可能です。内部ロジックは、内部で生成されるグローバル・クロックおよびコントロール信号用に、グローバル・クロック・ネットワークをドライブできます。図 2-13 に、グローバル・クロック・ネットワークへのさまざまなクロック・ソースを示します。

#### 図 2-13. グローバル・クロックの生成

#### 図 2-13 の注:

(1) どの I/O ピンも MultiTrack インタコネクトを使用して、ロジック・アレイで生成されたグローバル・クロック信号として配線できます。

グローバル・クロック・ネットワークは、デバイスの上から下まで LAB カラム全体に広がる個々の LAB カラム信号、LAB カラム・クロック [3..0] をドライブします。LAB カラム内の未使用のグローバル・クロックまたはコントロール信号は、 $\boxtimes$  2-14 に示す LAB カラム・クロック・バッファでオフにされます。LAB カラム・クロック [3..0] は、2 つの LAB クロック信号と1 つの LAB クリア信号に多重化されます。その他のコントロール信号タイプは、グローバル・クロック・ネットワークから LAB ローカル接続に配線されます。詳細については、2-6 ページの「LAB コントロール信号」を参照してください。

#### 図 2-14. グローバル・クロック・ネットワーク 注 (1)

### 図 2-14 の注:

- (1) I/O ブロック領域の LAB カラム・クロックは、ファン・アウトの大きい出力イネーブル信号を供給します。

- (2) LAB カラム・クロックは UFM ブロックにドライブされます。

# ユーザ・フラッ シュ・メモリ・ ブロック

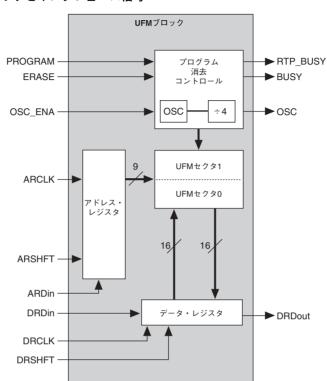

MAXII デバイスは1つの UFM ブロックを備えており、この UFM ブロックをシリアル EEPROM のように使用して、最大 8,192 ビットの不揮発性情報を格納できます。UFM ブロックは、MultiTrack インタコネクトを介してロジック・アレイに接続されるため、どの LE も UFM ブロックにインタフェースすることができます。図 2-15 に UFM ブロックとインタフェース信号を示します。ロジック・アレイは、UFM ブロック・データをデバイス外部にインタフェースするためのカスタマ・インタフェースまたはプロトコル・ロジックを作成するのに使用されます。UFM ブロックは、以下の機能を提供しています。

- 最大 16 ビット幅、合計 8,192 ビットの不揮発性ストレージ

- 分割されたセクタを消去するための2つのセクタ

- オプションによってロジック・アレイをドライブするビルトイン内 部オシレータ

- プログラム、消去、およびビジー信号

- 自動インクリメント・アドレス指定

- プログラマブル・インタフェースを備えたロジック・アレイへのシリアル・インタフェース

### 図 2-15. UFM ブロックとインタフェース信号

# UFM ストレージ

各デバイスは、UFM ブロック内に最大 8,192 ビットのデータを格納します。表 2-3 に、UFM ブロックのデータ・サイズ、セクタ数、およびアドレス・サイズを示します。

| 表 2-3. UFM アレイ・サイズ                     |        |                      |              |      |  |  |  |  |

|----------------------------------------|--------|----------------------|--------------|------|--|--|--|--|

| デバイス                                   | 合計ビット数 | セクタ数                 | アドレス・<br>ビット | データ幅 |  |  |  |  |

| EPM240<br>EPM570<br>EPM1270<br>EPM2210 | 8,192  | 2<br>(4,096 ビット/セクタ) | 9            | 16   |  |  |  |  |

512 の場所があり、 $000h \sim 1FFh$  の範囲にわたって9 ビットでアドレス指定されます。セクタ 0 のアドレス空間は  $000h \sim 0FFh$ 、セクタ 1 のアドレス空間は  $100h \sim 1FFh$  です。データ幅は最大 16 ビット・データです。Quartus II 開発ソフトウェアは、より小さなリード・データまたはプログラム・データ幅に対応するロジックを自動的に作成します。UFM を消去するには、セクタを個別に消去する必要があります(つまり、UFM ブロック全体を消去するには、セクタ 0 を消去し、セクタ 1 を消去しなければならない)。セクタ消去はプログラム前または書き込み前に必要なので、2 つのセクタを用意しておくと、一方のデータのセクタ・サイズ分は消去して新しいデータをプログラムしながら、他方のセクタはそのまま維持することが可能です。

# 内部オシレータ

図 2-15 に示すように、UFM ブロック内の専用回路にはオシレータが内蔵されています。専用回路は、このオシレータを内部で読み出しとプログラム動作に使用します。このオシレータの4分周出力は、UFM ブロックからインタフェース・ロジック・クロック・ソース用または汎用ロジック・クロッキング用のロジック・アレイにドライブ・アウトできます。OSC 出力信号の周波数の範囲は、3.3 MHz から 5.5 MHz(暫定仕様)であり、厳密な動作周波数はプログラムできません。

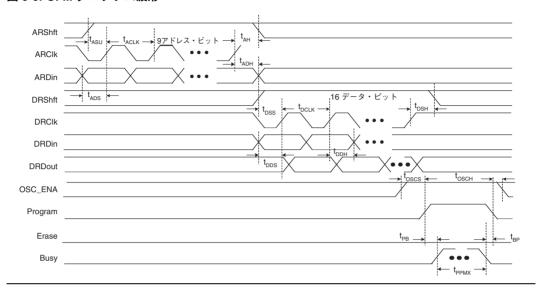

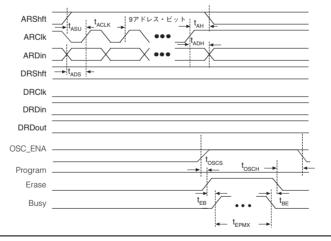

# プログラム、消去、およびビジー信号

UFM ブロックの専用回路は、PROGRAM または ERASE 入力信号がアサートされると、必要な内部プログラムおよび消去アルゴリズムを自動的に生成します。PROGRAM または ERASE 信号は、busy 信号がデアサートされてUFM内部プログラムまたは消去動作が完了したことを示すまで、アサートしておく必要があります。UFM ブロックは、JTAG をプログラミングや読み出し用のインタフェースとしてもサポートします。

UFM ブロックのプログラミングおよび消去の詳細については、「MAX II デバイスにおけるユーザ・フラッシュ・メモリの使用」の章を参照してください。

# 自動インクリメント・アドレス指定

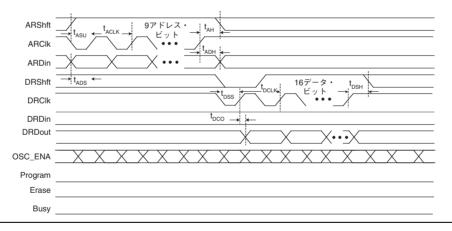

UFM ブロックは、標準的なリード動作またはストリーム・リード動作をサポートします。ストリーム・リードは、自動インクリメント・アドレス機能によりサポートされます。ARCLK 信号をクロックしている間にARSHIFT 信号をデアサートすると、アドレス・レジスタ値がインクリメントされて、UFM アレイから連続した位置が読み出されます。

### シリアル・インタフェース

UFM ブロックは、シリアル・アドレスおよびデータ信号を使用してシリアル・インタフェースをサポートします。UFM ブロック内のアドレス用およびデータ用の内部シフト・レジスタは、それぞれ9ビット幅と16ビット幅です。Quartus II 開発ソフトウェアは、LE内でパラレル・アドレスおよび UFM ブロックへのデータ・インタフェース用にインタフェース・ロジックを自動的に生成します。また、SPI などのその他の標準プロトコル・インタフェースも、Quartus II 開発ソフトウェアによって LE 内で自動的に生成されます。

UFMインタフェース信号およびQuartus II LEベースの代替インタフェースの詳細については、「MAX II デバイスにおけるユーザ・フラッシュ・メモリの使用 | を参照してください。

### UFM ブロックからロジック・アレイへのインタフェース

UFM ブロックは、図 2-1 と 2-2 に示すとおり、CFM ブロックを内蔵したフラッシュ・メモリの小さなパーティションです。EPM240 デバイスのUFM ブロックは、左端の LAB カラムに隣接するデバイスの左サイドに配置されています。EPM570、EPM1270、および EPM2210 デバイスのUFM ブロックは、デバイスの左下の部分に配置されています。UFM の入力および出力信号は、すべてのタイプのインタコネクト(R4 インタコネクト、C4 インタコネクト、および隣接 LAB ロウとの間の DirectLink インタコネクト)にインタフェースします。UFM 信号はグローバル・クロック GCLK[3..0] からもドライブできます。EPM240 デバイスのインタフェース領域を図2-16に示します。EPM570、EPM1270、およびEPM2210 デバイスのインタフェース領域を図2-17 に示します。

### 図 2-16. EPM240 UFM ブロックの LAB ロウ・インタフェース 注 (1)

#### 図 2-16 の注:

(1) UFM ブロックの入力および出力は、隣接するロウ LAB からの DirectLink 接続だけでなく、すべてのタイプのインタコネクトとの間で相互にドライブできます。

#### 図 2-17. EPM570、EPM1270、および EPM2210 の UFM ブロックの LAB ロウ・インタフェース

## MultiVolt コア

MAX II アーキテクチャは MultiVolt<sup>TM</sup> コア機能をサポートし、この機能によって MAX II デバイスは、 $V_{CCINI}$  電源で複数の  $V_{CC}$  レベルをサポートできます。内部リニア電圧レギュレータは、必要な  $1.8\,V$  の内部電源電圧をデバイスに供給します。図 2-18 に示すように、電圧レギュレータは入力で  $3.3\,V$  または  $2.5\,V$  電源をサポートし、 $1.8\,V$  の内部電圧をデバイスに供給します。電圧レギュレータは、最大推奨動作電圧  $2.5\,V$  と最小推奨動作電圧  $3.3\,V$  の間の電圧に対しては保証されません。

外部 1.8 V 電源に対しては、MAXIIG デバイスが必要です。これらのデバイス上の電圧レギュレータはバイパスされ、1.8 V 内部電源への 1.8 V V<sub>CC</sub> 外部電源パスがサポートされます。MAXIIG デバイスに関する最新情報については、アルテラにお問い合わせください。

#### 図 2-18. MAX II デバイスでの MultiVolt コア機能

## I/O 構造

IOE は以下のような多数の機能をサポートしています。

- LVTTL および LVCMOS 標準 I/O 規格

- 3.3V、32 ビット、33 MHz PCI 仕様に準拠

- Joint Test Action Group (JTAG) バウンダリ・スキャン・テスト (BST) のサポート

- プログラマブル・ドライブ強度コントロール

- パワー・アップおよびイン・システム・プログラミング時の弱いプルアップ抵抗

- スルー・レート・コントロール

- 個別出力イネーブル・コントロール付きトライ・ステート・バッファ

- バス・ホールド回路

- ユーザ・モードのプログラマブル・プルアップ抵抗

- ピンごとの固有出力イネーブル

- オープン・ドレイン出力

- シュミット・トリガ入力

- 高速 I/O 接続

- プログラム可能な入力遅延

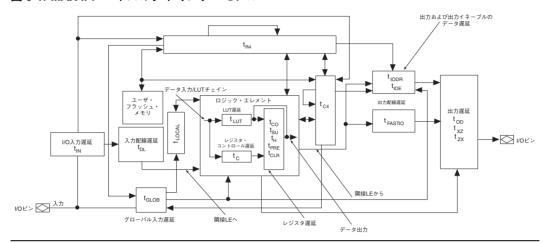

MAX II デバイスの IOE には、双方向 I/O バッファが内蔵されています。 図 2-19 に MAX II IOE 構造を示します。 隣接する LAB からのレジスタは、IOE の双方向 I/O バッファにドライブでき、またこのバッファからドライブすることもできます。 Quartus II 開発ソフトウェアは、高速 I/O 接続を使用する 隣接 LAB に自動的にレジスタを配置して、「Clock-to-Output」 およびラッチされた出力イネーブルのタイミングを可能な限り高速化します。 入力レジスタに対しては、 Quartus II 開発ソフトウェアは自動的にレジスタを配線して、ゼロ・ホールド・タイムを保証します。 Quartus II 開発ソフトウェアでは、タイミング・アサインメントを設定して目的の I/O タイミングを実現できます。

## 高速 I/O 接続

隣接する LAB から I/O ブロック内の IOEへの専用高速 I/O 接続によって、「Clock-to-Output」の出力遅延および  $t_{PD}$  伝播遅延が低減されます。この接続はデータ出力信号用であり、出力イネーブル信号や入力信号用ではありません。図 2-20、2-21 および 2-22 に、高速 I/O 接続を示します。

#### 図 2-19. MAX II の IOE 構造

図 2-19 の注:

(1) EPM1270 および EPM2210 デバイスでのみ利用可能。

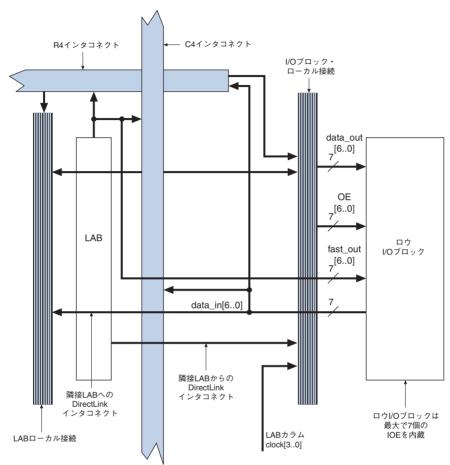

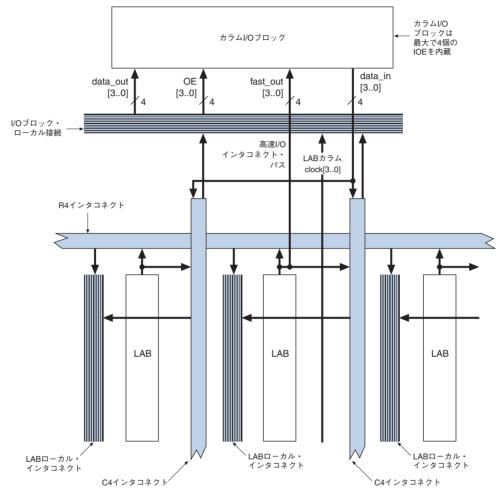

## I/O ブロック

IOE は、MAX II デバイス周辺の I/O ブロック内に配置されています。1 つのロウ I/O ブロックあたり最大 7 つの IOE (EPM240 デバイスでは最大 5 つ)、および 1 つのカラム I/O ブロックあたり最大 4 つの IOE があります。各カラムまたはロウ I/O ブロックは、隣接する LAB および MultiTrack インタコネクトにインタフェースして、デバイス全体に信号を配信します。ロウ I/O ブロックは、ロウ、カラム、または DirectLink インタコネクトをドライブします。カラム I/O ブロックは、カラム・インタコネクトをドライブします。

図 2-20 に、ロウ I/O ブロックをロジック・アレイに接続する方法を示します。

## 図 2-20. インタコネクトへのロウ I/O ブロックの接続 注 (1)

#### 図 2-20 の注:

(1) ロウ I/O ブロックの7つの IOE はそれぞれ、1つの data\_out または fast\_out 出力、1つの OE 出力、および 1つの data\_in 入力を持つことができます。

図 2-21 に、カラム I/O ブロックをロジック・アレイに接続する方法を示します。

## 図 **2-21**. インタコネクトへのカラム **I/O** ブロックの接続 注 (1)

### 図 2-21 の注:

(1) カラム I/O ブロックの 4 つの IOE はそれぞれ、1 つの data\_out または fast\_out 出力、1 つの OE 出力、および 1 つの data\_in 入力を持つことができます。

## 標準 I/O 規格およびバンク

MAX II デバイスの IOE は、以下の標準 I/O 規格をサポートしています。

- 3.3 V LVTTL/LVCMOS

- 2.5 V LVTTL/LVCMOS

- 1.8 V LVTTL/LVCMOS

- 1.5 V LVCMOS

- 3.3 V PCI

表 2–4 に、MAX II デバイスによってサポートされる標準 I/O 規格を示します。

| 表 2-4. MAX II 標準 I/O 規格 |          |                                                |  |  |

|-------------------------|----------|------------------------------------------------|--|--|

| 標準 I/O 規格               | タイプ      | 出力電源電圧( <b>V</b> <sub>CCIO</sub> )( <b>V</b> ) |  |  |

| 3.3 V LVTTL/LVCMOS      | シングル・エンド | 3.3                                            |  |  |

| 2.5 V LVTTL/LVCMOS      | シングル・エンド | 2.5                                            |  |  |

| 1.8 V LVTTL/LVCMOS      | シングル・エンド | 1.8                                            |  |  |

| 1.5 V LVCMOS            | シングル・エンド | 1.5                                            |  |  |

| 3.3 V PCI (1)           | シングル・エンド | 3.3                                            |  |  |

#### 表 2-4 の注:

(1) 3.3 V PCIは、EPM1270およびEPM2210デバイスのバンク3でサポートされます。

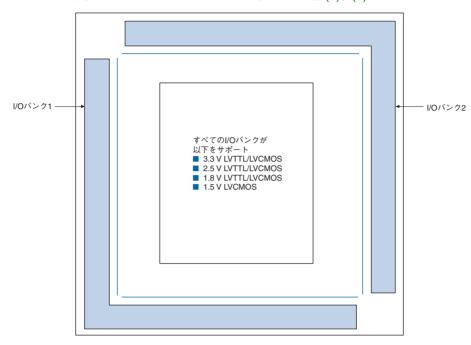

EPM240 および EPM570 デバイスは、図 2-22 に示すように、2 つの I/O バンクをサポートします。これらのバンクはそれぞれ、表 2-4 に示すすべての LVTTL および LVCMOS 規格をサポートします。PCI I/O は、これらのデバイスおよびバンクではサポートされません。

### 図 2-22. EPM240 および EPM570 の MAX II I/O バンク 注 (1)、(2)

#### 図 2-22 の注:

- (1) 図 2-22 はシリコン・ダイの上面図を示します。

- (2) 図 2-22 は説明用の図です。正確なピン配置については、ピン・リストおよび Quartus II 開発ソフトウェアを参照してください。

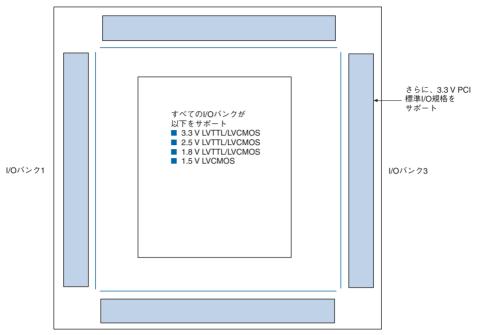

EPM1270 および EPM2210 デバイスは、図 2-23 に示すように、4 つの I/O バンクをサポートします。これらのバンクはそれぞれ、表 2-4 に示すすべての LVTTL および LVCMOS 規格をサポートします。PCI I/O はバンク 3 でサポートされます。バンク 3 は、入力の PCI クランプ・ダイオードおよび出力の PCI ドライブ準拠をサポートします。PCI 準拠の I/O ピンを必要とするデザインには、バンク 3 を使用する必要があります。Quartus II 開発ソフトウェアは、PCI I/O 規格で割り当てられた場合、このバンクに自動的に I/O ピンを配置します。

### 図 2-23. EPM1270 および EPM2210 の MAX II I/O バンク 注 (1)、(2)

I/Oバンク4

#### 図 2-23 の注:

- (1) 図 2-23 はシリコン・ダイの上面図を示します。

- (2) 図 2-23 は説明用の図です。正確なピン配置については、ピン・リストおよび Quartus II 開発ソフトウェアを参照 してください。

各 I/O バンクには専用の VCCIO ピンがあり、このピンによってバンクでの電圧規格のサポートが決定されます。1 つのデバイスで、1.5 V、1.8 V、2.5 V、3.3 V インタフェースをサポートできるので、各バンクは個別に異なる規格をサポートできます。各 I/O バンクは、入力および出力ピンに同じ VCCIO を使用する複数の標準 I/O 規格をサポートできます。例えば、VCCIO が 3.3 V の場合、バンク 3 は、LVTTL、LVCMOS、および 3.3 V PCI をサポートできます。VCCIO は、MAX II デバイスの入力バッファと出力バッファの両方に電力を供給します。

MAX II デバイスの JTAG ピンは、通常の I/O ピンとしては使用できない専用ピンです。TMS、TDI、TDO、および TCK ピンは、PCI を除いて、2–35ページの表 2–4 に示すすべての標準 I/O 規格をサポートします。すべての MAX II デバイスで、これらのピンはバンク 1 に存在し、標準 I/O 規格サポートはバンク 1 の  $V_{CCIO}$  設定によって制御されます。

#### PCI 準拠

MAX II EPM1270 および EPM2210 デバイスは、PCI アプリケーションに 準拠し、さらに PCI Local Bus Specification Revision 2.2 のすべての 3.3 V 電気的仕様に準拠しています。また、これらのデバイスは、PCI IP (Intellectual Property) コアをサポートするだけの十分なサイズがあります。表 2-5 に、PCI タイミング仕様に適合する MAX II デバイスのスピード・グレードを示します。

| 表 2-5. MAX II デバイスおよび 3.3 V PCI 電気規格をサポートし<br>PCI タイミングに適合するスピード・グレード 注 (1) |                       |  |  |  |

|-----------------------------------------------------------------------------|-----------------------|--|--|--|

| デバイス 33 MHz PCI                                                             |                       |  |  |  |

| EPM1270                                                                     | EPM1270 すべてのスピード・グレード |  |  |  |

| EPM2210                                                                     | すべてのスピード・グレード         |  |  |  |

#### 表 2-5 の注:

(1) この表には暫定的な情報が含まれています。

### シュミット・トリガ

各 MAX II デバイスの I/O ピンに対する入力バッファは、オプションで  $3.3\,\mathrm{V}$  および  $2.5\,\mathrm{V}$  規格に対応するシュミット・トリガ設定を備えています。シュミット・トリガによって、入力バッファは、高速出力エッジ・レートで低速入力エッジ・レートに応答することができます。最も重要な点は、シュミット・トリガによって入力バッファにヒステリシス特性が与えられ、立ち上がりが低速でノイズの多い入力信号が、ロジック・アレイにドライブされる入力信号上でリンギングしたり発振することを防止できることです。これによって、MAX II 入力のシステムノイズ耐性が確保されますが、入力遅延もわずかに増加します。

JTAG 入力ピン (TMS、TCK、およびTDI) には、シュミット・トリガ・バッファがあり、これらは常にイネーブルされています。

## 出力イネーブル信号

各 MAX II IOE 出力バッファは、トライ・ステート・コントロール用の出力イネーブル信号をサポートします。出力イネーブル信号は、GCLK [3..0] グローバル信号または MultiTrack インタコネクトから生成できます。MultiTrack インタコネクトは、出力イネーブル信号を配信し、各出力または双方向ピンに対する固有の出力イネーブルを可能にします。

MAX II デバイスには、チップ・ワイドの出力イネーブル・ピン(DEV\_OE)もあるため、デザインのすべての出力ピンに対して出力イネーブルを制御できます。このピンは、Quartus II 開発ソフトウェアでコンパイルを行う前に設定されたオプションによって制御されます。このチップ・ワイドの出力イネーブルは、自身の配線リソースを使用し、4 つのグローバル・リソースのいずれも使用しません。このオプションをオンにした場合は、DEV\_OE がアサートされると、チップ上のすべての出力が通常どおり動作します。ピンがデアサートされると、すべての出力がトライ・ステートになります。このオプションをオフにした場合、DEV\_OE ピンはデバイスがユーザ・モードで動作するときはディセーブルされ、ユーザ I/O ピンとして使用可能になります。

## プログラマブル・ドライブ強度

各MAXIIデバイスのI/Oピン用の出力バッファは、LVTTLおよびLVCMOS標準 I/O 規格のそれぞれに対応する、2 つのレベルのプログラマブル・ドライブ強度コントロールを備えています。プログラマブル・ドライブ強度によって、システム・ノイズ低減コントロールを提供し、高性能 I/O デザインを実現します。独立したスルー・レート・コントロール機能も存在しますが、より低いドライブ強度設定を使用すれば、スルー・レート・コントロール機能に伴う大きな遅延を追加しないで、信号のスルー・レートを制御して、システム・ノイズや信号オーバシュートを低減できます。表 2-6に、ドライブ強度コントロール付き標準 I/O 規格に対する設定を示します。PCI標準 I/O 規格は常に 20 mA に設定され、それ以外に設定されることはありません。

| 表 2-6. プログラマブル・ドライブ強度 注 (1) (1/2) |                                                         |  |  |  |  |

|-----------------------------------|---------------------------------------------------------|--|--|--|--|

| 標準 I/O 規格                         | 標準 I/O 規格 I <sub>OH</sub> /I <sub>OL</sub> の電流強度設定 (mA) |  |  |  |  |

| 3.3 V LVTTL                       | 16                                                      |  |  |  |  |

|                                   | 8                                                       |  |  |  |  |

| 3.3 V LVCMOS                      | 8                                                       |  |  |  |  |

|                                   | 4                                                       |  |  |  |  |

| 表 2-6. プログラマブル・ドライブ強度 注 (1) (2/2) |    |  |  |

|-----------------------------------|----|--|--|

| 2.5 V LVTTL/LVCMOS                | 14 |  |  |

|                                   | 7  |  |  |

| 1.8 V LVTTL/LVCMOS                | 6  |  |  |

|                                   | 3  |  |  |

| 1.5 V LVCMOS                      | 4  |  |  |

|                                   | 2  |  |  |

#### 表 2-6 の注:

(1) ここに示す電流強度の値  $I_{OH}$  は、 $V_{OUT}$  = 最小  $V_{OH}$  の条件に対するもので、最小  $V_{OH}$  は標準 I/O 規格によって規定されます。ここに示す電流強度の値  $I_{OL}$  は、 $V_{OUT}$  = 最大  $V_{OL}$  の条件に対するもので、最大  $V_{OL}$  は標準 I/O 規格によって規定されます。2.5 V LVTTL/LVCMOS の場合、 $I_{OH}$  の条件は  $V_{OUT}$  = 1.7 V で、 $I_{OL}$  の条件は  $V_{OUT}$  = 0.7 V です。

#### スルー・レート・コントロール

各 MAX II デバイスの I/O ピン用の出力バッファは、プログラム可能なスルー・レート・コントロール機能を備えており、この機能は低ノイズまたは高速性能を実現するようにコンフィギュレーションできます。高速スルー・レートを指定した場合は、高性能システムに対応した高速転送が行われます。ただし、このような高速転送によりシステムにノイズ・トランジェントが発生する可能性があります。低速スルー・レートを指定した場合は、システム・ノイズが低減しますが、立ち上がりおよび立ち下がりエッジにわずかな出力遅延が追加されます。電圧規格が低い電圧(1.8 V LVTTL など)になるほど、低速スルーがイネーブルされたときの出力遅延が増大します。各 I/O ピンには個別にスルー・レート・コントロール機能が提供されているため、設計者はピン単位でスルー・レートを指定することができます。スルー・レート・コントロールは、立ち上がりと立ち下がりエッジの両方に影響を与えます。

## オープン・ドレイン出力

MAX II デバイスは、各 I/O ピンに対しオプションでオープン・ドレイン (オープン・コレクタと同等)出力を提供します。このオープン・ドレイン出力により、複数のデバイスのいずれかでアサートできるシステム・レベルのコントロール信号 (割り込み信号やライト・イネーブル信号など)を供給することができます。この出力は追加の有線 OR プレーンも提供できます。

## プログラマブル・グランド・ピン

MAX II デバイスの未使用 I/O ピンはそれぞれ、追加グランド・ピンとして使用できます。このプログラム可能なグランド機能には、デバイス内の関連 LE を使用する必要はありません。Quartus II 開発ソフトウェアでは、未使用ピンはグローバル・デフォルト・ベースでプログラマブル GNDとして設定するか、または個別に割り当てることができます。未使用ピンには、トライ・ステート入力ピンとして設定するオプションも用意されています。

### バス・ホールド

MAX II デバイスの各 I/O ピンは、オプションのバス・ホールド機能を備えています。バス・ホールド回路は、I/O ピンの信号を最後にドライブされた状態で保持します。バス・ホールド機能は、次の入力信号が現れるまで、最後にドライブされた状態にピンを保持するため、バスがトライ・ステートになったとき、信号レベルを保持するための外部プルアップまたはプルダウン抵抗が不要になります。

バス・ホールド回路は、ノイズによって予定外の高周波数スイッチングが発生しそうな場合、ドライブされていないピンを入力スレッショルド電圧から離します。この機能は、設計者が各 I/O ピンに対して個別に選択できます。バス・ホールド出力のドライブは  $V_{CCIO}$  を超えることはなく、信号のオーバドライブが防止されます。バス・ホールド機能が有効にされている場合、デバイスではプログラマブル・プルアップ・オプションを使用できません。

バス・ホールド回路は抵抗を使用して、信号レベルを最後にドライブされた状態にプルします。「DC & スイッチング特性」の章では、この抵抗を通してドライブされる各  $V_{\rm CCO}$  電圧レベルの具体的な保持電流、および次にドライブされる入力レベルの識別に使用されるオーバドライブ電流について説明しています。

バス・ホールド回路は、デバイスが完全に初期化された後にのみアクティブになります。バス・ホールド回路は、ユーザ・モードへの移行時にピンに与えられた値をキャプチャします。

## プログラマブル・プルアップ抵抗

MAX II デバイスの各 I/O ピンは、ユーザ・モードで使用されるプログラマブル・プルアップ抵抗をオプションで提供します。設計者が 1つの I/O ピンに対してこの機能を有効にすると、プルアップ抵抗が出力を出力ピンのバンクの  $V_{CCIO}$  レベルに保持します。

I プログラマブル・プルアップ抵抗機能は、I/O ピンのバス・ホー ルド機能と同時に使用してはなりません。

## プログラマブル入力遅延

MAX II の IOE はプログラム可能な入力遅延を備えており、アクティブ にするとゼロ・ホールド・タイムが保証されます。ピンでレジスタを直 接ドライブするパスでは、ピンとレジスタ間の配線が最短な場合、ゼロ・ ホールド・タイムを確保するために遅延が必要なことがあります。ただ し、長い配線または組み合わせロジックを通してピンがレジスタをドラ イブするパスの場合には、ゼロ・ホールド・タイムを実現するための遅 延は必要ありません。Ouartus II 開発ソフトウェアはこの遅延を使用し、 必要に応じてゼロ・ホールド・タイムを保証します。

#### MultiVolt I/O インタフェース

MAX II アーキテクチャは MultiVolt I/O インタフェース機能をサポート しており、すべてのパッケージの MAX II デバイスは電源電圧の異なるシ ステムとのインタフェースが可能になります。このデバイスは、内部動 作用(VCCINT)に1組、入力バッファおよびI/O出力ドライバ・バッ ファ用 (VCCIO) に4組の VCC ピンを備えています。

VCCIO ピンは、要求される出力のレベルに応じて、1.5 V、1.8 V、2.5 V、 3.3 V のいずれかの電源に接続します。出力レベルは電源と同じ電圧のシ ステムと互換性を持ちます(つまり、VCCIOピンが1.5V電源に接続さ れている場合、出力レベルは1.5Vのシステムと互換性がある)。VCCIO ピンを 3.3 V 電源に接続した場合、出力の High レベルは 3.3 V になり、 3.3 V または 5.0 V システムと互換性を持つようになります。表 2-7 は、 MAX II の MultiVolt I/O サポートをまとめたものです。

| 表 2-7. N              | IAX II の | MultiVol | t I/O サホ     | <b>パート</b> | 注(    | 1)           |              |              |       |       |

|-----------------------|----------|----------|--------------|------------|-------|--------------|--------------|--------------|-------|-------|

| V <sub>CCIO</sub> (V) | 入力信号     |          |              |            |       |              |              | 出力信号         |       |       |

|                       | 1.5 V    | 1.8 V    | 2.5 V        | 3.3 V      | 5.0 V | 1.5 V        | 1.8 V        | 2.5 V        | 3.3 V | 5.0 V |

| 1.5                   | 1        | 1        | √(2)         | √ (2)      |       | 1            |              |              |       |       |

| 1.8                   |          | 1        | 1            | 1          |       | √ (3)        | 1            |              |       |       |

| 2.5                   |          |          | 1            | 1          |       | √ (4)        | √ (4)        | 1            |       |       |

| 3.3                   |          |          | <b>√</b> (5) | 1          | √ (6) | <b>√</b> (7) | <b>√</b> (7) | <b>√</b> (7) | 1     | √ (8) |

#### 表 2-7 の注:

- (1) オーバシュートを含めて、 $V_{CCIO}$  より高く 4.0~V より低い電圧に入力をドライブするには、PCI クランプ・ダイオードを無効にします。ただし、デバイスの 5.0~V 入力をドライブするには、PCI クランプ・ダイオードを有効にして、 $V_I$  が 4.0~V を超えないようにします。

- (2)  $V_{\rm CCIO}=1.5$  V で、2.5 V または 3.3 V 入力信号が入力ピンに供給される場合、ピンのリーク電流が増大すると予想されます。

- (3)  $V_{CCIO} = 1.8 \text{ V}$  のとき、MAX II デバイスは許容入力電圧が 1.8 V の 1.5 V デバイスをドライブできます。

- (4) V<sub>CCIO</sub>=2.5 Vの場合、MAX II デバイスは許容入力電圧が2.5 Vの1.5 Vまたは1.8 V デバイスをドライブできます。

- (5)  $V_{CCIO}$ =3.3 V で、2.5 V 入力信号が入力ピンに供給される場合、VCCIO 供給電流は、予想値よりわずかに高くなります。

- (6) MAX II デバイスは、EPM1270 および EPM2210 デバイス上で外部抵抗と内部 PCI クランプ・ダイオードを 使用して 5.0 V を許容できます。

- (7)  $V_{\rm CCO}$  = 3.3 V の場合、MAX II デバイスは許容入力電圧が 3.3 V の 1.5 V、1.8 V、または 2.5 V デバイスをドライブできます。

- (8)  $V_{\text{CCIO}} = 3.3 \text{ V}$  の場合、MAX II デバイスは 5.0 V TTL 入力のデバイスはドライブできますが、5.0 V CMOS 入力のデバイスはドライブできません。5.0 V CMOS の場合、PCI クランプ・ダイオード(EPM1270 および EPM2210 デバイスのみ内蔵)付きオープン・ドレイン設定と外部抵抗が必要です。

## 3. JTAG およびイン・システム・ プログラマビリティ

この資料は更新された最新の英語版が存在します。こちらの日本語版は参考用としてご利用ください。 設計の際には、最新の英語版で内容をご確認ください。

MII51003-1.2

IEEE Std. 1149.1(JTAG) バウンダリ・ スキャンの サポート すべての MAX®II デバイスは、IEEE Std.1149.1-2001 規格に準拠する JTAG (Joint Test Action Group) バウンダリ・スキャン・テスト (BST) 回路を提供します。JTAG バウンダリ・スキャン・テストは、V<sub>CCINI</sub> およびすべての V<sub>CCIO</sub> バンクに完全に給電され、t<sub>CONFIG</sub> 時間が経過すれば、いつでも実行できます。MAX II デバイスは JTAG ポートを、Programming Objectファイル (.pof)、Jam™ STAPL (Standard Test and Programming Language)ファイル (.jam) 、または Jam Byte-Code ファイル (.jbc) を使用するQuartus® II 開発ソフトウェアまたはハードウェアとともに、イン・システム・プログラミングに使用することもできます。

JTAG ピンは、1.5 V、1.8 V、2.5 V、または 3.3 V 標準 I/O 規格をサポートします。サポートされる電圧レベルと規格は、そのピンが存在するバンクの  $V_{CCIO}$  によって決まります。専用 JTAG ピンは、MAX II デバイスのバンク 1 内に存在します。

MAX II デバイスは、表 3–1 に示す JTAG インストラクションをサポートします。

| 表 3–1. MAX II の JTAG インストラクション (1/2) |              |                                                                                                                                                      |  |  |

|--------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| JTAG インストラクション                       | 命令コード        | 説明                                                                                                                                                   |  |  |

| SAMPLE/PRELOAD                       | 00 0000 0101 | 通常動作中のデバイスのピンから信号を取り込んでテストすることができる。また、最初のデータ・パターンをデバイス・<br>ピンに出力させることができる。                                                                           |  |  |

| EXTEST (1)                           | 00 0000 1111 | 出力ピンにテスト・パターンを強制的に与え、入力ピンでテスト結果を取り込むことによって、外部回路との接続とボード・レベルの配線をテストできる。                                                                               |  |  |

| BYPASS                               | 11 1111 1111 | TDIピンとTDOピンの間に1ビットのバイパス・レジスタを配置して、デバイスの通常動作時にバウンダリ・スキャン・データが選択されたデバイスをバイパスして隣接するデバイスに同期転送されるようにする。                                                   |  |  |

| USERCODE                             | 00 0000 0111 | 32 ビットの USERCODE レジスタを選択して、TDI ピンと TDO ピンの間に配置することによって、USERCODE を TDO からシリアルにシフト・アウトできるようにする。このレジスタは、Quartus II 開発ソフトウェアで指定されていない場合、デフォルトですべて 1 になる。 |  |  |

| 表 3–1. MAX II の JTAG イ | 表 3–1. MAX II の JTAG インストラクション (2/2) |                                                                                                                                           |  |  |  |

|------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JTAG インストラクション         | 命令コード                                | 説明                                                                                                                                        |  |  |  |

| IDCODE                 | 00 0000 0110                         | IDCODEレジスタを選択してTDIとTDOの間に配置することによって、IDCODE を TDO からシリアルにシフト・アウトできるようにする。                                                                  |  |  |  |

| HIGHZ (1)              | 00 0000 1011                         | TDI ピンとTDO ピンの間に1ビットのバイパス・レジスタを配置することによって、すべての I/O ピンをトライ・ステートにした状態で、デバイスの通常動作時にバウンダリ・スキャン・データが選択されたデバイスをバイパスして、隣接するデバイスに同期転送されるようにする。    |  |  |  |

| CLAMP (1)              | 00 0000 1010                         | TDIピンとTDOピンの間に1ビットのバイパス・レジスタを配置して、I/Oピンをバウンダリ・スキャン・レジスタ内のデータで定義される状態に保持し、デバイスの通常動作時にバウンダリ・スキャン・データが指定したデバイスをバイパスして、隣接するデバイスに同期転送されるようにする。 |  |  |  |

| USER0                  | 00 0000 1100                         | この命令によって、ユーザは MAX II ロジック・アレイの TDI と TDO の間に独自のスキャン・チェインを定義できる。この命令はカスタム・ロジックおよび JTAG インタフェースにも使用される。                                     |  |  |  |

| USER1                  | 00 0000 1110                         | この命令によって、ユーザは MAX II ロジック・アレイの TDI と TDO の間に独自のスキャン・チェインを定義できる。この命令はカスタム・ロジックおよび JTAG インタフェースにも使用される。                                     |  |  |  |

| IEEE 1532 命令           | (2)                                  | JTAG ポートを介して MAX II デバイスをプログラムするときに使用される IEEE 1532 ISC 命令                                                                                 |  |  |  |

#### 表 3-1 の注:

- (1) HIGHZ、CLAMP、および EXTEST 命令は、弱いプルアップ抵抗やバス・ホールド機能をディセーブルすることはありません。

- (2) これらの命令は 1532 BSDL ファイルに記載されています。1532 BSDL ファイルは、アルテラの Web サイト www.altera.co.jp に適宜掲載されます。

MAX II デバイスのインストラクション・レジスタの長さは 10 ビットで、USERCODE レジスタの長さは 32 ビットです。表 3-2 と 3-3 は、各MAX II デバイスのバウンダリ・スキャン・レジスタの長さとデバイス IDCODE 情報を示したものです。

| 表 3-2. MAX II のバウンダリ・スキャン・レジスタの長さ |     |  |  |  |  |

|-----------------------------------|-----|--|--|--|--|

| デバイス バウンダリ・スキャン・レジスタの長さ           |     |  |  |  |  |

| EPM240                            | 240 |  |  |  |  |

| EPM570                            | 480 |  |  |  |  |

| EPM1270                           | 636 |  |  |  |  |

| EPM2210                           | 816 |  |  |  |  |

| 表 3-3. M | 表 3–3. MAX II デバイスの 32 ビット IDCODE |                     |                                    |                    |            |  |  |

|----------|-----------------------------------|---------------------|------------------------------------|--------------------|------------|--|--|

|          |                                   |                     |                                    |                    |            |  |  |

| デバイス     | バージョン<br>(4ビット)                   | 部品番号                | メーカの <b>ID</b><br>( <b>11</b> ビット) | LSB<br>(1 ビット) (2) | HEX IDCODE |  |  |

| EPM240   | 0000                              | 0010 0000 1010 0001 | 000 0110 1110                      | 1                  | 0x020A10DD |  |  |

| EPM570   | 0000                              | 0010 0000 1010 0010 | 000 0110 1110                      | 1                  | 0x020A20DD |  |  |

| EPM1270  | 0000                              | 0010 0000 1010 0011 | 000 0110 1110                      | 1                  | 0x020A30DD |  |  |

| EPM2210  | 0000                              | 0010 0000 1010 0100 | 000 0110 1110                      | 1                  | 0x020A40DD |  |  |

#### 表 3-2 の注:

- (1) 左側が最上位ビット (MSB) です。

- (2) IDCODE の最下位ビット (LSB) は常に1です。

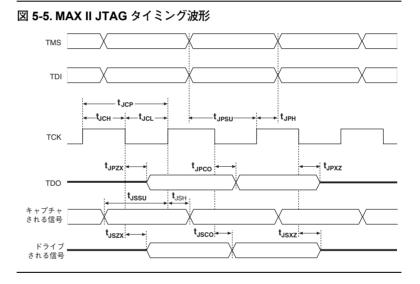

JTAG AC 特性については、「DC & スイッチング特性」の章を参照してください。JTAG BST の詳細については、「MAX II デバイスの IEEE 1149.1 (JTAG) バウンダリ・スキャン・テスト」の章を参照してください。

## JTAG トランスレータ

JTAGトランスレータ機能を使用すると、JTAG TAPに USERO 命令または USER1 命令が発行されたときに、JTAG TAP およびステート信号にアクセスすることができます。 USERO 命令および USER1 命令は、MAX II デバイスのバウンダリ・スキャン・セルではなくユーザ・ロジックを介して、JTAG バウンダリ・スキャン・チェイン(TDI)を伝達します。各USER 命令によって、ロジック・アレイに対して独自のユーザ定義 JTAGチェインが1つ許容されます。

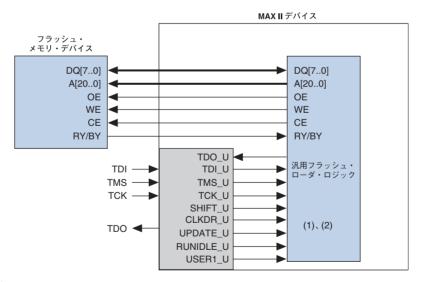

### パラレル・フラッシュ・ローダ

ITAG トランスレータは ITAG デバイスを非 ITAG デバイスにインタ フェースできるため、イン・サーキット・テスト中にプログラミングを 必要とする汎用フラッシュ・メモリ・デバイス (Intel または Fuiitsu ベー スのデバイス) に最適です。フラッシュ・メモリ・デバイスは、FPGA コ ンフィギュレーション用またはシステム・メモリのパーツとして使用で きます。多くの場合、MAXIIデバイスは、FPGAとフラッシュ・デバイ ス間のコンフィギュレーション・コントロール・ロジックとして、これ らのデバイスに接続済みです。ISP 対応の CPLD デバイスとは異なり、バ ルク・フラッシュ・デバイスには ITAG TAP ピンや ITAG TAP 接続はあ りません。小型フラッシュ・デバイスの場合、接続されたデバイスのシ リアル ITAG スキャン・チェインを使用して、非 ITAG フラッシュ・デ バイスをプログラムするのが一般的です。この方法は、ほとんどの場合 は低速かつ非効率であり、また大型パラレル・フラッシュ・デバイスに 対しては実用的ではありません。MAX II デバイスの ITAG トランスレー タをパラレル・フラッシュ・ローダとして使用して、フラッシュの内容 をプログラムおよび検証すると、テスト中にイン・システム・プログラ ミングを高速かつ経済的に実行できます。図 3-1 に、パラレル・フラッ シュ・ローダとして使用される MAX II を示します。

### 図 3-1. 汎用フラッシュ・ローダとしての MAX II JTAG トランスレータ

#### 図 3-1 の注:

- (1) このブロックは LE に実装されています。

- (2) この機能は Quartus II 開発ソフトウェアの将来のバージョンでサポートされます。

# イン・システ ム・プログラ マビリティ

MAX II デバイスは、業界標準の 4 ピン IEEE Std. 1149.1 (JTAG) インタフェースを介して、イン・システムでプログラムできます。ISP (In-System Programmability) によって、デザイン開発およびデバッグ・サイクル中に迅速で効率的な繰り返し作業が可能です。MAX II アーキテクチャのロジック、回路、およびインタコネクトは、フラッシュ・ベースの SRAM コンフィギュレーション・エレメントでコンフィギュレーションされます。これらの SRAM エレメントでは、デバイスに電源が供給されるたびにコンフィギュレーション・データをロードする必要があります。SRAM データをロードするプロセスをコンフィギュレーションと呼びます。オン・チップ・コンフィギュレーション・フラッシュ・メモリ(CFM)ブロックは、SRAM エレメントのコンフィギュレーション・データを格納します。CFM ブロックは、再プログラム可能なフラッシュ・アレイにデザインのコンフィギュレーション・パターンを格納します。ISP の間に、MAX II JTAG および ISP 回路は、CFM ブロックの不揮発性フラッシュ・メモリにデザイン・パターンをプログラムします。

MAX II JTAG および ISP コントローラは、内部で CFM セルのプログラムに要求される高いプログラミング電圧を生成するため、どの推奨動作外部供給電圧(つまり、MAX IIG デバイスの場合は、 $3.3\,\mathrm{V}/2.5\,\mathrm{V}$  または  $1.8\,\mathrm{V}$ ) でもイン・システム・プログラミングが可能です。 $\mathrm{V}_{\mathrm{CCIO}}$  がよびすべての $\mathrm{V}_{\mathrm{CCIO}}$  バンクに完全に給電され、コンフィギュレーション・パワー・アップ・タイムが経過した後は、いつでも ISP を実行することができます。デフォルトでは、イン・システム・プログラミング中に、I/O ピンはトライ・ステートになり、 $\mathrm{V}_{\mathrm{CCIO}}$  に弱くプルアップされて、ボードの競合を回避します。イン・システム・プログラミング・クランプおよびリアル・タイム ISP 機能によって、ISP 中にユーザが I/O の状態や動作を制御することができます。

詳細については、3-8 ページの「イン・システム・プログラミング・クランプ | および 3-8 ページの「リアルタイム ISP | を参照してください。

これらのデバイスは、イン・システム・プログラミングが中断されたときに安全に動作させる ISP\_DONE ビットも提供します。ISP\_DONE ビットはプログラムされる最終ビットで、このビットがプログラムされるまで、すべての I/O ピンのドライブを防止します。

## IEEE 1532 サポート

MAX II デバイスの JTAG 回路および ISP 命令セットは、IEEE 1532-2002 プログラミング標準規格に準拠しています。これによって、JTAG チェイン内にある複数ベンダのプログラマブル・ロジック・デバイス (PLD) 間でのイン・システム・プログラミングに対応する業界標準ハードウェアおよびソフトウェアが実現します。

MAX II 1532 BSDL ファイルは、アルテラの Web サイトで適宜リリースされます。

## STAPL (Jam Standard Test & Programming Language)

Jam STAPL JEDEC 規格、JESD71 は、イン・サーキット・テスタ、PC、またはエンベデッド・プロセッサを搭載した MAX II デバイスをプログラムするのに使用できます。MAX II デバイスでは、Jam バイト・コードもサポートされています。これらのソフトウェア・プログラミング・プロトコルは、MAX II デバイスをプログラムするためのコンパクトなエンベデッド・ソリューションを提供します。

詳細については、「エンベデッド・プロセッサを利用したISP用JamSTAPLの使用 | の章を参照してください。

## プログラミング・シーケンス

イン・システム・プログラミング中に、1532 の命令、アドレス、および データは、TDI 入力ピンを通して MAX II デバイスにシフトされます。デー タは TDO 出力ピンを通してシフト・アウトされ、所期のデータと比較されます。デバイスにパターンをプログラムするには、以下の6つの ISP ステップが必要です。プログラムされたパターンのスタンドアロン検証には、ステージ 1、2、5 および 6 だけが必要です。これらのステップは、サードパーティ・プログラム、Quartus® II 開発ソフトウェア、または Jam STAPL および Jam Byte-Code Player によって、自動的に実行されます。

- 1. ISP への移行 ISP への移行ステージによって、I/O ピンをユーザ・モードから ISP モードにスムーズに遷移させます。

- 2. ID のチェック プログラムまたは検証プロセス前に、シリコン ID が チェックされます。このシリコン ID の読み出しに要する時間は、プログラミング時間全体と比較すれば短時間です。

- 3. セクタ消去 イン・システムでのデバイスの消去には、デバイスを消去するための命令をシフト・インして消去パルスを印加します。消去パルスは、CFM ブロックに対して指定された消去パルス時間 500 ms、そして UFM ブロックの各セクタに対して指定された消去パルス時間 500 ms の間、実行 / テスト / アイドル・ステートで待機することにより、内部で自動的に生成されます。

- 4. プログラム イン・システムでデバイスをプログラムするには、アドレス、データ、およびプログラム命令のシフト・イン、そしてフラッシュ・セルをプログラムするためのプログラム・パルスの生成が必要です。プログラム・パルスは、指定されたプログラム・パルス時間 75 μs の間、実行 / テスト / アイドル・ステートで待機することによって、内部で自動的に生成されます。このプロセスが CFM および UFM ブロックの各アドレスごとに繰り返されます。

- 5. 検証 イン・システムで MAX II デバイスを検証するには、アドレスのシフト・イン、検証命令によるリード・パルスの生成、および比較のためのデータのシフト・アウトを実行します。このプロセスは、各 CFMおよび UFM アドレスごとに繰り返されます。

- 6. ISP の終了 ISP の終了ステージによって、I/O ピンを ISP モードから ユーザ・モードにスムーズに遷移させます。

TCK 周波数が  $10\,\text{MHz}$  の場合、EPM240 およびEPM570 デバイスでは消去およびプログラミングに必要な時間は  $2\,$  秒未満です。消去およびプログラミング時間は、EPM1270 では  $3\,$  秒未満、EPM2210 デバイスでは  $4\,$  秒未満です。 TCK 周波数は、MAX II デバイスでは最大  $18\,\text{MHz}$  なので、これらの ISP 時間がいくらか短縮されます。

## UFM プログラミング

Quartus II 開発ソフトウェアは、POF、Jam、または JBC ファイルを使用することにより、CFM ブロックに格納されたロジック・アレイ・デザイン・パターンに関係なく、各ユーザ・フラッシュ・メモリ(UFM)ブロック・セクタのプログラミングをサポートします。これによって、現在のロジック・アレイ・デザインを変更することなく、ISP を経由して UFM の内容の更新または読み出し(またはその逆の処理)が可能になります。デフォルトでは、これらのプログラミング・ファイルおよび方法は、CFM ブロックと UFM の内容を含む両方のフラッシュ・メモリ全体の内容をプログラムします。スタンドアロンのエンベデッド Jam STAPL プレーヤおよび Jam Byte-Code Player は、フラッシュ・メモリ全体(UFM と CFM の両方)またはそれぞれを個別にプログラムしたり、読み出したりするための動作コマンドを提供します。

詳細については、「エンベデッド・プロセッサを利用したISP用Jam STAPL の使用」の章を参照してください。

## イン・システム・プログラミング・クランプ

デフォルトでは、ISP への移行に使用される IEEE 1532 命令は、ISP シーケンスの間、弱いプルアップ抵抗ですべての I/O ピンを自動的にトライ・ステートにします。ただし、一部のシステムでは、イン・フィールド・アップデートの間、MAX II デバイスの特定のピンで、特定の DC ロジック・レベルを維持する必要があります。これらのシステムの場合、ISP シーケンス中の I/O 動作を制御するために、MAX II 回路にオプションのイン・システム・プログラミング・クランプ命令が存在します。イン・システム・プログラミング・クランプ命令によって、デバイスは出力ピン上の値をサンプリングして保持する(サンプリングされた場合、入力ピンはトライ・ステートに維持される)か、あるいは任意のピン上でロジック High、ロジック Low、またはトライ・ステート値を明示的に設定できます。これらのオプションの設定は、Quartus II 開発ソフトウェアを使用して、個々のピンごとに制御されます。

詳細については、「MAX II デバイスのリアルタイム ISP および ISP クランプ | の章を参照してください。

### リアルタイム ISP

I/O ピンを DC ロジック・レベルより高く制御する必要があるシステムでは、リアルタイム ISP 機能を利用することにより、現在のデザインが SRAM ロジック・アレイおよび I/O ピンで動作している間に、新しいデザイン・イメージで CFM ブロックをアップデートすることができます。新しいプログラミング・ファイルは、元のデザインの動作を停止させることなくアップデートされて MAX II デバイスに転送されるため、リモートまたはフィールド・アップグレードのためのダウン・タイム・コストが節約されます。アップデートされた CFM ブロックは、次回のパワー・サイクルで新しいデザインを SRAM にコンフィギュレーションします。また、ISP コマンドの特定のシーケンスを使用することによって、パワー・サイクルなしで SRAM のコンフィギュレーションをすぐに実行することも可能です。パワー・サイクルを使用しないで SRAM をコンフィギュレーションするには、一定時間( $t_{CONFIG}$ )を要します。この期間中、I/O ピンはトライ・ステートになり、 $V_{CCIO}$  に弱くプルアップされます。

## デザイン・セキュリティ

すべての MAX II デバイスには、CFM ブロックにプログラムされたデータへのアクセスを制御するプログラム可能なセキュリティ・ビットがあります。このビットがプログラムされているときには、CFM ブロックに格納されたデザイン・プログラミング情報をコピーしたり、取り出すことはできません。フラッシュ・メモリ・セル内のプログラム済みデータが隠蔽されるため、この機能は高度なデザイン・セキュリティを提供します。この機能を制御するセキュリティ・ビット、およびその他すべてのプログラム済みデータは、デバイスが消去されたときにのみリセットされます。また、セキュリティ・ビットの設定に関係なく、SRAMも隠蔽されアクセスできません。UFM ブロック・データは、セキュリティ・ビットで保護されないため、JTAG またはロジック・アレイ接続を介してアクセスできます。

## 外部ハードウェアによるプログラミング

MAX II デバイスは、イン・サーキット・テスタ、エンベデッド・プロセッサ、アルテラの Byteblaster MV Master Blaster M Byte Blaster II 、および USB-Blaster ケーブルを介し、適切なアダプタを搭載したユニバーサル・シリアル・バス(USB)ベースのアルテラ・プログラミング・ユニット(APU)を使用して情報をダウンロードすることによってプログラムできます。

BP Microsystems、System General、およびその他のプログラミング・ハードウェア・メーカから、アルテラ・デバイスのプログラミング・サポートが提供されています。デバイスのサポート情報については、これらのメーカの Web サイトで確認してください。

## 4. MAX II デバイスのホット・ソケット およびパワー・オン・リセット

この資料は更新された最新の英語版が存在します。こちらの日本語版は参考用としてご利用ください。 設計の際には、最新の英語版で内容をご確認ください。

MII51004-1.2

## ホット・ ソケット

MAX® II デバイスは、ホット・プラグインまたはホット・スワップとしても知られるホット・ソケット(活線挿抜)およびパワー・シーケンスをサポートします。設計者は、システム・バスに影響を与えることなく、システム動作中に MAX II ボードを取り付けたり、取り外すことができます。ホット・ソケット機能によって、3.3 V、2.5 V、1.8 V、および 1.5 V デバイスが混在するプリント基板(PCB)でコンポーネントを使用する際に発生する問題の一部も解消されます。

以下に MAX II デバイスのホット・ソケット機能を示します。

- ボードまたはデバイスの挿抜

- 任意のパワー・アップ・シーケンスのサポート

- 活線挿入時にシステム・バスに影響しない I/O バッファ

### MAXIIのホット・ソケット仕様

MAX II デバイスは、外付け部品や特別なデザイン要件なしで、上記のホット・ソケットに必要な3つの機能をすべて提供します。ホット・ソケット仕様は以下のとおりです。

- デバイスを損傷させることなく、パワー・アップ前(パワー・アップ時)またはパワー・ダウン前(パワー・ダウン時)にデバイスをドライブ可能。

- パワー・アップ時に I/O ピンをトライ・ステート状態に維持。パワー・アップ前またはパワー・アップ時にデバイスがドライブ・アウトしないため、他の動作中のバスに影響しない。

- 信号ピンが $V_{CCIO}$ または $V_{CCINI}$ 電源をドライブしない。デバイスのI/O ピンへの外部入力信号が、デバイス内部でデバイスの内部パスを通して  $V_{CCIO}$ または  $V_{CCINI}$  に給電しない。

## パワー・アップ前にドライブ可能なデバイス

パワー・アップ前 (パワー・アップ時) またはパワー・ダウン前 (パワー・ダウン時) に、デバイスを損傷させずに、MAX II デバイスの I/O ピンおよび GCLK [3..0] ピンに信号をドライブすることができます。MAX II デバイスでは、システム・レベルのデザインを簡単にするために、任意のパワー・アップ・シーケンスまたはパワー・ダウン・シーケンス ( $V_{CCIO1}$ 、 $V_{CCIO2}$ 、 $V_{CCIO3}$ 、 $V_{CCIO4}$ 、 $V_{CCIO4}$ 、 $V_{CCIO4}$ 、 $V_{CCIO5}$

#### パワー・アップ時にトライ・ステートに維持される I/O ピン

ホット・ソケットをサポートしないデバイスは、パワー・アップ前またはパワー・アップ時にドライブ・アウトして、システム動作に割り込んだり衝突を引き起こすことがあります。ホット・ソケット状況では、システムのパワー・アップ時に MAXII デバイスの出力バッファがオフになります。また、MAXII デバイスは、デバイスが完全にコンフィギュレーションされて適切な動作状態になるまではドライブ・アウトしません。電圧投入の詳細については、4-6ページの「パワー・オン・リセット回路」を参照してください。

## V<sub>CCIO</sub> または V<sub>CCINT</sub> 電源をドライブしない信号ピン

MAX II デバイスには、パワー・アップ前またはパワー・アップ時に、I/O ピン、GCLK [3..0] ピンから  $V_{CCIO}$  ピンまたは  $V_{CCINI}$  ピンへの電流経路 はありません。MAX II デバイスは、システム・ボードの動作を停止させ たり妨害することなく、パワー・アップされたシステム・ボードに取り付ける (または、システム・ボードから取り外す) ことができます。MAX II デバイスは、ホット・ソケット時にバックプレーンのシグナル・インテグリティに最小限の影響しか及ぼしません。

### AC および DC 仕様

$V_{CCIO}$  ピンと  $V_{CCINIT}$  ピンは、任意のシーケンスでパワー・アップまたは パワー・ダウンできます。MAX II デバイスには、 $V_{CC}$  ランプ・レート 要件はありません。ホット・ソケット中、I/O ピンのキャパシタンスは 8 pF 未満です。MAX II デバイスは、以下のホット・ソケット仕様に適合しています。

- ホット・ソケット DC 仕様 | I<sub>IOPIN</sub> | < 300 µA

- ホット・ソケット AC 仕様は、で表されるとおり、信号電圧とボード・キャパシタンスに依存します。

$|I_{IOPIN}| < (\Delta v/\Delta t) \times capacitance$

ここで、キャパシタンスは、I/O ピン、トレース、およびコネクタ のキャパシタンスの合計です。

II MAX II デバイスは、ホット・ソケット時にラッチ・アップの影響は受けません。

TCK JTAG 入力ピンが、ホット・ソケット中に High にドライブされると、そのピンの電流が上記の仕様を超える可能性があります。

## MAX II デバイスへのホット・ソケット機能の実装

ホット・ソケット機能により、出力バッファはパワー・アップ・イベント時( $V_{CCINT}$  電源または $V_{CCIO}$  電源のいずれか)またはパワー・ダウン時にオフ(トライ・ステート)になります。ホット・ソケット回路は、 $V_{CCINT}$ または $V_{CCIO}$ がスレッショルド電圧より低くなると、内部HOTSCKT信号を生成します。HOTSCKT信号によって出力バッファが遮断されるため、ピンを通して DC 電流がリークすることはありません(ウィーク・プルアップ・リーク電流を除く)。 $V_{CC}$  が非常にゆっくり上昇する場合、パワー・オン・リセット(POR)信号が解放されて、デバイスのコンフィギュレーションが完了した後でも、 $V_{CC}$  は依然として比較的低い電圧のままです。

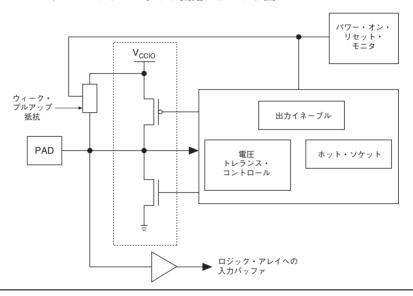

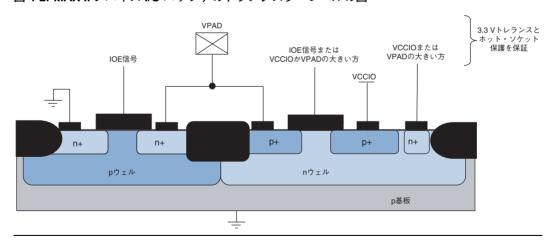

各 I/O およびクロック・ピンには、図 4-1 に示す回路があります。

#### 図 4-1. MAX II デバイスのホット・ソケット回路のブロック図

POR 回路は、 $V_{CCINT}$  および  $V_{CCIO}$  電圧レベルをモニタし、デバイスが SRAM ロジックのフラッシュ・メモリ・コンフィギュレーションを完了 するまで、I/O ピンをトライ・ステートに維持します。I/O ピンから  $V_{CCIO}$  に弱いプルアップ抵抗 (R) があり、ダウンロード中は I/O ピンがフロートしないようにイネーブルされます。  $3.3\,V$  トレランス・コントロール回路により、 $V_{CCIO}$  または  $V_{CCINT}$  (あるいはその両方) に給電される前に、I/O ピンを  $3.3\,V$  でドライブでき、デバイスに完全に給電されていない場合やデバイスが動作状態でない場合に、I/O ピンがドライブ・アウトしないようにすることができます。ホットソケット回路は、デバイスに給電される前に外部信号により I/O ピンがドライブされたときに、I/O ピンが内部で  $V_{CCIO}$  と  $V_{CCIO}$  に電源を供給するのを防止します。

5.0 V トレランスについては、「多電圧システムにおける MAX II デバイスの使用 | の章を参照してください。

図 42 に、MAX II デバイス I/O バッファのトランジスタ・レベルの断面図を示します。このデザインでは、 $V_{CCINI}$  の前に  $V_{CCIO}$  に給電されたとき、または I/O パッド電圧が  $V_{CCIO}$  より高い場合に、出力バッファがドライブしないことが保証されます。これは活線挿入時の突発的な電圧スパイクにも適用されます。 $V_{PAD}$  リーク電流によって、3.3 V トレランス回路のキャパシタンスが充電されます。

#### 図 4-2 MAX II デバイス I/O バッファのトランジスタ・レベルの図

I/Oピン内のCMOS出力ドライバは、本質的に静電気放電(ESD)保護されています。ESD電圧ストライクに対しては、正電圧ザップおよび負電圧ザップの2つのケースについて検討する必要があります。

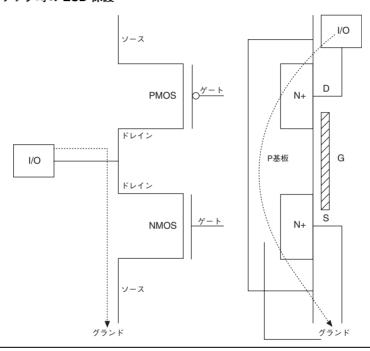

正の ESD 電圧ザップは、ESD の充電事象によって I/O ピンに正電圧が存在する場合に発生します。この正の ESD 電圧ザップは、N チャネル・ドレインの N+ (ドレイン) /P 基板接合部の破壊を引き起こす可能性があり、N+ (ドレイン) /P 基板 /N+ (ソース) 真性バイポーラ・トランジスタが導通して、I/O ピンから GND に ESD 電流が放電されます。破線(図4-3を参照)は、正の ESP ザップ時の ESD 電流放電経路を示しています。

#### 図 4-3. 正電圧ザップ時の ESD 保護

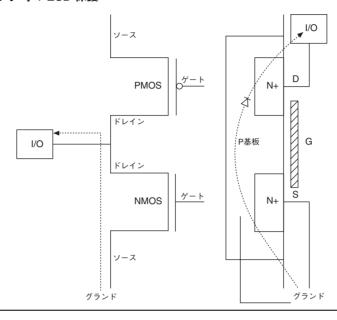

I/O ピンが -0.7 V (0.7 V はダイオード両端の電圧降下) より低い電圧の ピンで負の ESP ザップを受け取ると、真性 P 基板 /N+ ドレイン・ダイオードが順バイアスされます。したがって、放電 ESD 電流経路は、図 -4 4 に示すとおり、GND から I/O ピンになります。

#### 図 4-4. 負電圧ザップ時の ESD 保護

## パワー・オン・ リセット回路

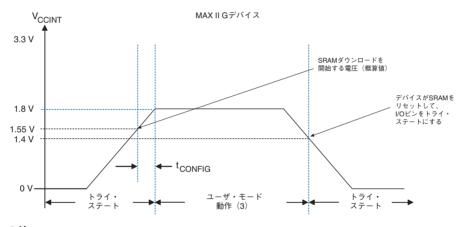

MAX II デバイスは、パワー・アップ時の  $V_{CCINI}$  および  $V_{CCIO}$  電圧レベルに対する POR 回路を備えています。POR 回路は、これらの電圧をモニタし、不揮発性コンフィギュレーション・フラッシュ・メモリ(CFM) ブロックから SRAM ロジックへのダウンロードをトリガし、このプロセスの実行前および実行中に I/O ピンを(弱いプルアップ抵抗をイネーブルして)トライ・ステートに維持します。MAX II デバイスがユーザ・モードに入ると、POR 回路は I/O ピンをユーザ機能に解放し、電圧降下状態を検知できるよう継続して、 $V_{CCINI}$  の電圧レベルをモニタします。ユーザ・モード中に、 $V_{CCINI}$  電圧が MAX II の動作レベルよりも低いレベルに降下すると、POR 回路によってデバイスがリセットされ、SRAM ダウンロードが再トリガされます。初期パワー・アップが完了し、ユーザ・モード機能に遷移した後は、I/O バンク  $V_{CCIO}$  レベルはモニタされません。

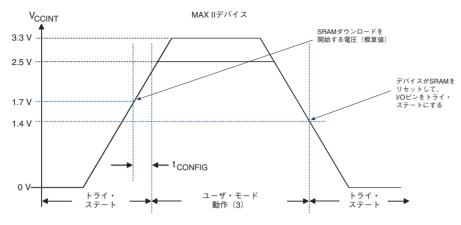

## パワー・アップ特性

MAX II デバイスに電源が投入されると、POR 回路が  $V_{CCINI}$  をモニタし、最大電圧 1.7V または MAX II G デバイスの場合は 1.55 V で SRAM ダウンロードを開始します。この電圧を基準にすると、SRAM ダウンロードおよびユーザ・モードへの移行には、デバイス集積度に応じて 200  $\mu$ s ~ 450  $\mu$ s (最大)の時間が必要です。この期間は、第 5 章「DC & スイッチング特性」のパワー・アップのタイミングのセクションに、 $t_{CONFIG}$  として規定されています。

ユーザ・モードへの移行は、すべての $V_{CCIO}$ バンクに十分な動作電圧が供給されているかどうかでゲートされます。 $V_{CCINI}$ および $V_{CCIO}$ に同時に給電された場合、デバイスは $t_{CONFIG}$  仕様以内にユーザ・モードに入ります。 $V_{CCINI}$  から $t_{CONFIG}$  以上の時間が経過した後に $V_{CCIO}$  に給電された場合、デバイスはすべての $V_{CCIO}$  バンクに給電されてから $2\mu s$  経過するまでは、ユーザ・モードに入りません。

ユーザ・モードでは、電圧降下状態を検知するために、POR 回路が継続して  $V_{CCINT}$  ( $V_{CCIO}$  は対象外)の電圧レベルをモニタします。ユーザ・モード中に、 $V_{CCINT}$  電圧が  $1.4\,V$  以下に低下した場合、POR 回路は SRAM をリセットして、I/O ピンをトライ・ステートにします。 $V_{CCINT}$  が再び  $1.7\,V$  (MAX IIG デバイスの場合は、 $1.55\,V$ ) に上昇すると、SRAM ダウンロードが再開され、 $I_{CCNFIC}$  時間が経過した後、デバイスは動作を開始します。

図 45 は、パワー・アップからユーザ・モードに遷移する間、およびユーザ・モードからパワー・ダウンまたは電圧降下状態に変化する間の MAX II および MAX II G デバイスの POR を示しています。

## 図 4-5. MAX II および MAX II G デバイスのパワー・アップ特性 注 (1)、(2)

#### 図 4-5 の注:

- (1) 時間スケールは相対的に表されています。

- (2) 図 45 では、すべての  $V_{CCIO}$  バンクが、ここに示す  $V_{CCINI}$  プロファイルと同時に給電されるものと仮定しています。 同時に給電されない場合は、すべての  $V_{CCIO}$  バンクに給電されるまで、 $t_{CONFIG}$  が延長されます。

SRAM のコンフィギュレーション後に、デバイス内のすべてのレジスタはクリアされ、I/Oのトライ・ステートが解放される前にユーザ機能に解放されます。トライ・ステートが解放された後にクリアを解放するには、DEV\_CLRn ピン・オプションを使用します。パワー・アップ・コンフィギュレーション時間を超えてトライ・ステートを維持するには、DEV OE ピン・オプションを使用します。

## 5. DC & スイッチング特性

この資料は更新された最新の英語版が存在します。こちらの日本語版は参考用としてご利用ください。 設計の際には、最新の英語版で内容をご確認ください。

MII51005-1.2

## 動作条件

表 5–1 から 5–12 に、 $MAX^{@}II$  デバイスの絶対最大定格、推奨動作条件、DC 特性、およびその他の仕様を示します。

## 絶対最大定格

表 5-1 に、MAX II デバイス・ファミリの絶対最大定格を示します。

| 表 5-1. M           | 表 <b>5–1. MAX II</b> デバイスの絶対最大定格 注 (1)、(2) |                            |                 |     |     |  |

|--------------------|--------------------------------------------|----------------------------|-----------------|-----|-----|--|

| シンボル               | パラメータ                                      | 条件                         | 最小              | 最大  | 単位  |  |

| V <sub>CCINT</sub> | 内部電源電圧 (3)                                 | GND に対して                   | -0.5            | 4.6 | V   |  |

| V <sub>CCIO</sub>  | I/O 電源電圧                                   |                            | -0.5            | 4.6 | V   |  |

| VI                 | DC 入力電圧                                    |                            | -0.5            | 4.6 | V   |  |

| I <sub>OUT</sub>   | ピンあたりのDC出力電流                               |                            | -25             | 25  | mA  |  |

| T <sub>STG</sub>   | 保存温度                                       | バイアスなし                     | <del>-</del> 65 | 150 | ° C |  |

| T <sub>AMB</sub>   | 周囲温度                                       | バイアス時                      | <del>-</del> 65 | 135 | ° C |  |

| TJ                 | 接合温度                                       | バイアス時のTQFPおよび<br>BGA パッケージ |                 | 135 | ° C |  |

#### 表 5-1 の注:

- (1)「Operating Requirements for Altera Devices Data Sheet」を参照してください。

- (2) 表 5-1 に記載された条件を超えると、デバイスに致命的な損傷を与える可能性があります。 また、デバイスを絶対最大定格で長期間動作させると、デバイスに悪影響を与える可能性があります。

- (3) 最大 V<sub>CCINT</sub> は、MAX II デバイスの場合は 4.6 V、MAX II G デバイスの場合は 2.4 V です。

## 推奨動作条件

表 5-2 に、MAX II デバイス・ファミリの推奨動作条件を示します。

| シンボル                   | パラメータ                                                | 条件          | 最小    | 最大                | 単位 |

|------------------------|------------------------------------------------------|-------------|-------|-------------------|----|

| V <sub>CCINT</sub> (1) | 内部ロジック<br>および ISP 用の<br>3.3 V 電源電圧                   |             | 3.00  | 3.60              | V  |

|                        | 内部ロジック<br>および ISP 用の<br>2.5 V 電源電圧                   |             | 2.375 | 2.625             | V  |

|                        | 内部ロジック<br>および ISP 用の<br>1.8 V 電源電圧<br>(MAX IIG デバイス) |             | 1.71  | 1.89              | V  |

| V <sub>CCIO</sub> (1)  | 3.3 V 動作の<br>I/O バッファ用<br>電源電圧                       |             | 3.00  | 3.60              | V  |

|                        | 2.5 V 動作の<br>I/O バッファ用<br>電源電圧                       |             | 2.375 | 2.625             | V  |

|                        | 1.8 V 動作の<br>I/O バッファ用<br>電源電圧                       |             | 1.71  | 1.89              | V  |

|                        | 1.5 V 動作の<br>I/O バッファ用<br>電源電圧                       |             | 1.425 | 1.575             | V  |

| V <sub>I</sub>         | 入力電圧                                                 | (2)、(3)、(4) | -0.5  | 4.0               | V  |

| V <sub>O</sub>         | 出力電圧                                                 |             | 0     | V <sub>CCIO</sub> | V  |

| 表 5–2. MAX II デバイスの推奨動作条件 (2/2) |                      |     |     |     |     |  |  |  |  |

|---------------------------------|----------------------|-----|-----|-----|-----|--|--|--|--|

| シンボル パラメータ 条件 最小 最大 単位          |                      |     |     |     |     |  |  |  |  |

| $T_J$                           | 動作接合温度 — 般用 0 85 ° C |     |     |     |     |  |  |  |  |

|                                 |                      | 工業用 | -40 | 100 | ° C |  |  |  |  |

#### 表 5-2: の注:

- (1) JTAG またはロジック・アレイを使用した MAX II デバイスのイン・システム・プログラミングや UFM プログラミングは、推奨動作条件の範囲外では保証されません(つまり、UFM に対する潜在的な書き込み / プログラム・シーケンス中に、システム内で電圧低下状態が発生した場合、ユーザは UFM の内容を再度読み込んで、書き込みデータを検証することが推奨される)。

- (2) 最小 DC 入力電圧は -0.5 V です。入力電流が 100 mA 未満で、20 ns 未満の幅の条件であれば、過渡状態の期間 に-2.0 V までアンダシュートしてもかまいません。

- (3) 過渡状態の期間には、入力デューティ・サイクルに基づいて、下表に示す電圧まで入力がオーバシュートしてもかまいません。DC の場合は 100% デューティ・サイクルと等価です。5.0 V トレランスについては、「多電圧システムにおける MAX II デバイスの使用 | の章を参照してください。

$V_{IN}$  最大デューティ・サイクル

4.0V 100% (DC)

10%

4.1 90%

4.2 50%

4.3 30%

4.4 17%

4.5

(4) クロック、I/O、JTAG ピンを含むすべてのピンは  $V_{CCINT}$  と  $V_{CCIO}$  が給電される前にドライブされる可能性があります。

## プログラミング/イレース仕様

表 5–3 に、MAX II デバイス・ファミリのプログラミング / イレース仕様を示します。

| 表 5–3. MAX II デバイスのプログラミング / イレース仕様 |         |  |  |       |  |  |  |

|-------------------------------------|---------|--|--|-------|--|--|--|

| パラメータ 最小 標準 最大 単位                   |         |  |  |       |  |  |  |

| 消去および再プログラムの<br>サイクル数               | 100 (1) |  |  | サイクル数 |  |  |  |

#### 表 5-3 の注:

(1) この仕様は、ユーザ・フラッシュ・メモリ(UFM) および CFM ブロックに適用されます。

### DC 特性

表 5-4 に、MAX II デバイス・ファミリの DC 特性を示します。

| 表 5–4. MA)                  | (Ⅱ デバイスの DC 特                        | 性 注 (1)                            |     |     |    |    |

|-----------------------------|--------------------------------------|------------------------------------|-----|-----|----|----|

| シンボル                        | パラメータ                                | 条件                                 | 最小  | 標準  | 最大 | 単位 |

| I <sub>I</sub>              | 入力ピンの<br>リーク電流                       | $V_I = V_{CCIOmax} \sim 0 V (2)$   | -10 |     | 10 | μA |

| I <sub>OZ</sub>             | トライ・ステート<br>I/O ピンの<br>リーク電流         | $V_{O} = V_{CCIOmax} \sim 0 V (2)$ | -10 |     | 10 | μА |

| I <sub>CCSTANDBY</sub>      | V <sub>CCINT</sub> 供給電流              | MAX II デバイス                        |     | 12  |    | mA |

|                             | (スタンバイ時) (3)                         | MAX II G デバイス                      |     | 2   |    | mA |

| V <sub>SCHMITT</sub> シュミット・ | 7 - 1 / 1                            | V <sub>CCIO</sub> = 3.3 V          |     | 460 |    | mV |

|                             | トリガ入力の<br>ヒステリシス                     | V <sub>CCIO</sub> = 2.5 V          |     | 170 |    | mV |

| I <sub>CCPower-up</sub>     | パワー・アップ時の                            | MAX II デバイス                        |     | 40  |    | mA |

|                             | V <sub>CCINT</sub> 供給電流 (4)          | MAX II G デバイス                      |     | 30  |    | mA |

| R <sub>PULLUP</sub>         | パワー・アップおよび                           | V <sub>CCIO</sub> = 3.3 V (5)      | 5   |     | 25 | kΩ |

|                             | イン・システム・<br>プログラミング時の                | V <sub>CCIO</sub> = 2.5 V (5)      | 10  |     | 40 | kΩ |

|                             | I/O ピン・プルアップ                         | V <sub>CCIO</sub> = 1.8 V (5)      | 25  |     | 60 | kΩ |

|                             | 抵抗の値                                 | V <sub>CCIO</sub> = 1.5 V (5)      | 45  |     | 95 | kΩ |

| C <sub>IO</sub>             | ユーザ I/O ピンの<br>入力キャパシタンス             |                                    |     |     | 8  | pF |

| C <sub>GCLK</sub>           | 兼用 GCLK/<br>ユーザ I/O ピンの<br>入力キャパシタンス |                                    |     |     | 8  | pF |

#### 表 5-4 の注:

- (1) 標準値は、 $T_A = 25$ °C、 $V_{CCINT} = 3.3$ Vまたは2.5V、および $V_{CCIO} = 1.5$ V、1.8V、1.8V、1.8V、1.8V、1.8V、1.8V 1.8V 1.8

- (2) この値は通常のデバイス動作用に指定されたものです。パワー・アップの過程では値が変わる場合があります。 これはすべての  $V_{CCIO}$  設定(3.3 V、2.5 V、1.8 V、および 1.5 V)に適用されます。

- (3)  $V_I = GND$ 、無負荷、入力のトグルなし

- (4) これはパワー・アップ時の平均電流です。MAX II デバイスの場合、標準的なピーク電流は 65 mA 未満です。 MAX II G デバイスの場合、標準的なピーク電流は 55 mA 未満です。

- (5) 外部ソースが VCCIOよりも高い電圧でピンをドライブしている場合は、ピンのプルアップ抵抗値が低下します。

## 標準 I/O 規格

表5-5から5-10に、MAXIIデバイス・ファミリの標準I/O規格を示します。

| 表 5–5. 3.3 V LVTTL 規格 |                  |                             |      |      |    |  |  |

|-----------------------|------------------|-----------------------------|------|------|----|--|--|

| シンボル                  | パラメータ            | 条件                          | 最小   | 最大   | 単位 |  |  |

| V <sub>CCIO</sub>     | I/O 電源電圧         |                             | 3.0  | 3.6  | V  |  |  |

| V <sub>IH</sub>       | 入力<br>High レベル電圧 |                             | 1.7  | 4.0  | V  |  |  |

| V <sub>IL</sub>       | 入力<br>Low レベル電圧  |                             | -0.5 | 0.8  | V  |  |  |

| V <sub>OH</sub>       | 出力<br>High レベル電圧 | I <sub>OH</sub> = -4 mA (1) | 2.4  |      | V  |  |  |

| V <sub>OL</sub>       | 出力<br>Low レベル電圧  | I <sub>OL</sub> = 4 mA (1)  |      | 0.45 | V  |  |  |

| 表 5–6. 3.3 V LVCMOS 規格 |                  |                                                    |                         |     |    |  |  |  |

|------------------------|------------------|----------------------------------------------------|-------------------------|-----|----|--|--|--|

| シンボル                   | パラメータ            | 条件                                                 | 最小                      | 最大  | 単位 |  |  |  |

| V <sub>CCIO</sub>      | I/O 電源電圧         |                                                    | 3.0                     | 3.6 | V  |  |  |  |

| V <sub>IH</sub>        | 入力<br>High レベル電圧 |                                                    | 1.7                     | 4.0 | V  |  |  |  |

| V <sub>IL</sub>        | 入力<br>Low レベル電圧  |                                                    | -0.5                    | 0.8 | V  |  |  |  |

| V <sub>OH</sub>        | 出力<br>High レベル電圧 | V <sub>CCIO</sub> = 3.0  I <sub>OH</sub> = -0.1 mA | V <sub>CCIO</sub> - 0.2 |     | V  |  |  |  |

| V <sub>OL</sub>        | 出力<br>Low レベル電圧  | V <sub>CCIO</sub> = 3.0  I <sub>OL</sub> = 0.1 mA  |                         | 0.2 | V  |  |  |  |

| 表 5-7. 2.5 V の I/O 規格 (1/2) |                  |    |       |       |    |  |  |  |

|-----------------------------|------------------|----|-------|-------|----|--|--|--|

| シンボル                        | パラメータ            | 条件 | 最小    | 最大    | 単位 |  |  |  |

| V <sub>CCIO</sub>           | I/O 電源電圧         |    | 2.375 | 2.625 | V  |  |  |  |

| V <sub>IH</sub>             | 入力<br>High レベル電圧 |    | 1.7   | 4.0   | V  |  |  |  |

| V <sub>IL</sub>             | 入力<br>Low レベル電圧  |    | -0.5  | 0.7   | V  |  |  |  |

| 表 5-7. 2.5 V の I/O 規格 (2/2) |                        |                             |     |     |    |  |  |

|-----------------------------|------------------------|-----------------------------|-----|-----|----|--|--|

| シンボル                        | パラメータ                  | 条件                          | 最小  | 最大  | 単位 |  |  |

| V <sub>OH</sub>             |                        | $I_{OH} = -0.1 \text{ mA}$  | 2.1 |     | V  |  |  |

| High レベル電                   | High レベル電圧             | I <sub>OH</sub> = -1 mA     | 2.0 |     | V  |  |  |

|                             |                        | I <sub>OH</sub> = -2 mA (1) | 1.7 |     | V  |  |  |

| V <sub>OL</sub>             | 出力                     | I <sub>OL</sub> = 0.1 mA    |     | 0.2 | V  |  |  |

| Low レベル電圧                   | I <sub>OL</sub> = 1 mA |                             | 0.4 | V   |    |  |  |

|                             |                        | I <sub>OL</sub> = 2 mA (1)  |     | 0.7 | V  |  |  |

| 表 5–8. 1.8 V の I/O 規格 |                  |                             |                          |                          |    |  |  |  |

|-----------------------|------------------|-----------------------------|--------------------------|--------------------------|----|--|--|--|

| シンボル                  | パラメータ            | 条件                          | 最小                       | 最大                       | 単位 |  |  |  |

| V <sub>CCIO</sub>     | I/O 電源電圧         |                             | 1.71                     | 1.89                     | V  |  |  |  |

| V <sub>IH</sub>       | 入力<br>High レベル電圧 |                             | 0.65 × V <sub>CCIO</sub> | 2.25                     | V  |  |  |  |

| V <sub>IL</sub>       | 入力<br>Low レベル電圧  |                             | -0.3                     | 0.35 × V <sub>CCIO</sub> | V  |  |  |  |

| V <sub>OH</sub>       | 出力<br>High レベル電圧 | I <sub>OH</sub> = -2 mA (1) | V <sub>CCIO</sub> – 0.45 |                          | V  |  |  |  |

| V <sub>OL</sub>       | 出力<br>Low レベル電圧  | I <sub>OL</sub> = 2 mA (1)  |                          | 0.45                     | V  |  |  |  |

| 表 5–9. 1.5 V の I/O 規格 |                  |                               |                          |                          |    |  |  |  |

|-----------------------|------------------|-------------------------------|--------------------------|--------------------------|----|--|--|--|

| シンボル                  | パラメータ            | 条件                            | 最小                       | 最大                       | 単位 |  |  |  |

| V <sub>CCIO</sub>     | I/O 電源電圧         |                               | 1.425                    | 1.575                    | V  |  |  |  |

| V <sub>IH</sub>       | 入力<br>High レベル電圧 |                               | 0.65 × V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3  | V  |  |  |  |