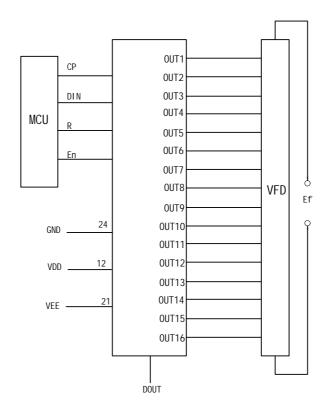

# 静态 VFD 驱动电路

#### 概述

TX16210 是一种负电源型 VFD 驱动电路,可用作 VFD 显示系统中 CPU 与 VFD 之间的接口电路,采用 16 位并行输出,使用灵活,通用性强。

### 功能特点

- 三电源供电, V<sub>DD</sub>=5V, V<sub>SS</sub>=0V。

- $V_{DISP} = -30V_{\circ}$

- 串行输入

- 16位的并行输出

- 并行输出端采用高压结构,可直接驱动 VFD。

- 串行输出端,以便扩展使用,增强其通用性。

- 采用外接时钟、清零端、输出控制,以便使用中与 CPU 相匹配。

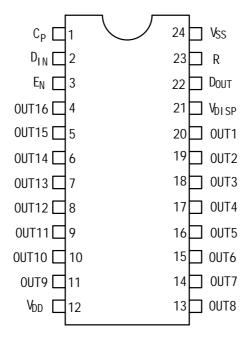

#### 管脚排列图

#### 管脚说明

| 管脚号           | 符号                          | 管脚名      | 1/0 | 说 明                                                                                                     |

|---------------|-----------------------------|----------|-----|---------------------------------------------------------------------------------------------------------|

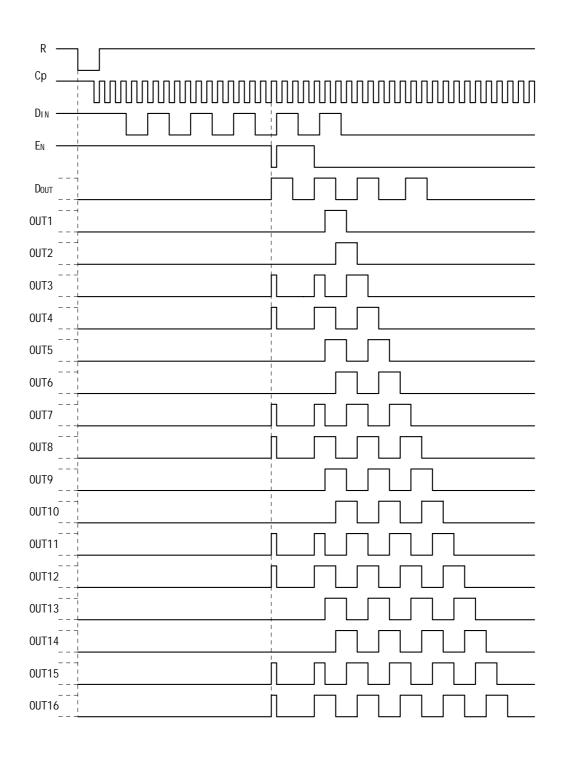

| 1             | $C_P$                       | 输入时钟     | I   | 下降沿时输入串行数据,上升沿时输出串行数据。                                                                                  |

| 2             | $\mathrm{D_{IN}}$           | 串行数据输入端  | Ι   | 时钟下降沿时输入串行数据                                                                                            |

| 3             | $\mathrm{E_{N}}$            | 数据输出控制端  | I   | 低电平有效,允许并行数据输出。低电平宽度不超过一个时钟周期,其下降沿要在时钟上升沿之后,上升沿要在时钟下降沿之前。使用中通过控制 E <sub>N</sub> 有效信号输入时间及扩展使用来实现多种并行输出。 |

| 4~11<br>13~20 | 0UT16∼0UT1                  | 并行数据输出   | 0   | 在 E <sub>N</sub> 为低电平时,并行数据输出。                                                                          |

| 12            | $V_{\mathrm{DD}}$           | 逻辑电源     |     | 5V                                                                                                      |

| 21            | $V_{\mathrm{DISP}}$         | VFD 驱动高压 | I   | 电压值可达-30V                                                                                               |

| 22            | $\mathrm{D}_{\mathrm{OUT}}$ | 串行数据输出   | 0   | 时钟上升沿时输出串行数据                                                                                            |

| 23            | R                           | 清零信号     | I   | 低电平有效, 须加10K上拉电阻                                                                                        |

| 24            | V <sub>SS</sub>             | 逻辑地      |     | 与系统地相连                                                                                                  |

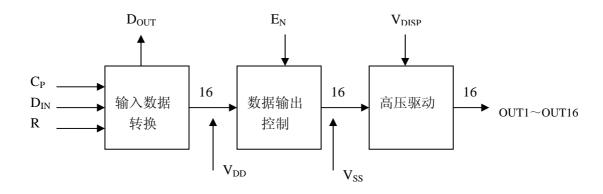

### 功能框图

该电路与 16312 属于同系列产品,电路由三部分组成,即输入数据转换部分、数据输出 控制部分、高压驱动部分。

### 功能说明

输入数据转换部分由 16 个带复位端的基本触发器组成,主要完成串行输入/并行输出转换功能,外接的复位端可以保证使用中与 CPU 同步清零。数据输出控制部分为带使能端的控制器。根据不同的的 VFD 屏,通过调节  $E_N$  与  $C_P$  的关系来控制数据的输出时间,即可以实现任意位的并行输出(即电路可以扩展)。使用中要严格控制  $E_N$  与  $C_P$  的关系。

## 时序图

#### 极限参数

#### 1. 工作条件(Ta=-20℃~+70℃, V<sub>ss</sub>=0V)

| 参 数     | 符号                | 最小值                   | 典型值 | 最大值                   | 单 位 |

|---------|-------------------|-----------------------|-----|-----------------------|-----|

| 工作电压    | $V_{DD}$          | 4.5                   | 5   | 5.5                   | V   |

| 高电平输入电压 | $V_{\mathrm{IH}}$ | $0.7~\mathrm{V_{DD}}$ | _   | $V_{ m DD}$           | V   |

| 低电平输入电压 | $V_{\mathrm{IL}}$ | 0                     |     | $0.3~\mathrm{V_{DD}}$ | V   |

| 驱动工作电压  | $ m V_{E}$        | 0                     |     | $V_{DD}$ -35          | V   |

#### 2. 极限工作范围 (Ta=25℃, V<sub>SS</sub>=0V)

| 参 数        | 符号                    | 范 围                                | 单 位          |  |

|------------|-----------------------|------------------------------------|--------------|--|

| 电源电压       | $V_{ m DD}$           | -0.5~7.0                           | V            |  |

| 驱动工作电压     | $V_{\rm E}$           | $V_{DD} + 0.5 \sim V_{DD} - 40$    | V            |  |

| 逻辑输入电压     | $V_{I1}$              | $-0.5 \sim V_{DD} + 0.5$           | V            |  |

| FIP 驱动输出电压 | $V_{O2}$              | $V_{EE}$ -0.5 $\sim$ $V_{DD}$ +0.5 | V            |  |

| FIP 驱动输出电流 | L流 I <sub>O2</sub> -8 |                                    | mA           |  |

| 消耗功率       | $P_{D}$               | 1200                               | mW           |  |

| 工作温度       | $T_{OPT}$             | -20∼+70                            | $^{\circ}$   |  |

| 存贮温度       | $T_{ST}$              | -65~+150                           | $^{\circ}$ C |  |

#### 3. 电特性(Ta=-20℃~+70℃, V<sub>DD</sub>=4.5V~5.5V, V<sub>SS</sub>=0V, V<sub>EE</sub>= V<sub>DD</sub>-35V)

| 参 数     | 符号                 | 测试条件                                            | 最小值                   | 典型值  | 最大值          | 单位 |

|---------|--------------------|-------------------------------------------------|-----------------------|------|--------------|----|

| 高电平输出电压 | $V_{OH1}$          |                                                 | $0.9~\mathrm{V_{DD}}$ |      |              | V  |

| 低电平输出电压 | $V_{OL1}$          |                                                 |                       |      | 1            | V  |

| 低电平输出电压 | $V_{OL2}$          |                                                 |                       |      | 0.4          | V  |

| 高电平输出电流 | $I_{OH21}$         | $V_O = V_{DD} - 2V$                             | -3                    |      |              | mA |

| 驱动漏电流   | I <sub>OLEAK</sub> | V <sub>O</sub> = V <sub>DD</sub> -35V,<br>驱动器关闭 |                       |      | -10          | uA |

| 输出下拉电阻  | $R_{L}$            | 驱动器输出                                           | 50                    | 100  | 150          | ΚΩ |

| 输入电流    | $I_{I}$            | $V_{I}=V_{DD}$ 或 $V_{SS}$                       |                       |      | ±1           | uA |

| 高电平输入电压 | $V_{\mathrm{IH}}$  |                                                 | $0.7~\mathrm{V_{DD}}$ |      |              | V  |

| 低电平输入电压 | $V_{\rm IL}$       |                                                 |                       |      | $0.3 V_{DD}$ | V  |

| 滞电电压    | $V_{\rm H}$        | CLK, DIN, STB                                   |                       | 0.35 |              | V  |

| 静态电流消耗  | $I_{DDdyn}$        | 无负载时,无显示                                        |                       |      | 5            | mA |

#### 4. 开关特性(Ta=-20℃~+70℃, V<sub>DD</sub>=4.5V~5.5V, V<sub>EE</sub>= -30V)

| 参数           | 符号        | 测试条件                                  | 最小值 | 典型值 | 最大值 | 单位  |

|--------------|-----------|---------------------------------------|-----|-----|-----|-----|

| 保持延迟         | $T_{PLZ}$ | $CLK \rightarrow D_{OUT}$             |     |     | 300 | ns  |

| <b>米</b> 特延迟 | $T_{PZL}$ | $C_L=15pF$ , $R_L=10 \text{ K}\Omega$ |     |     | 100 | ns  |

| 下降时间         | $T_{THZ}$ | $C_L = 300 \text{ pF}$                |     |     | 120 | us  |

| 最大时钟频率       | $F_{MAX}$ | 占空比=50%                               | 1   |     |     | MHz |

| 输入电容         | $C_{L}$   |                                       |     |     | 15  | pF  |

#### 5. 时序条件(Ta=-20℃~+70℃, V<sub>DD</sub>=4.5V~5.5V)

| h <del>.</del> |                      |              |     |     |     |    |

|----------------|----------------------|--------------|-----|-----|-----|----|

| 参 数            | 符号                   | 测试条件         | 最小值 | 典型值 | 最大值 | 单位 |

| 时钟脉冲宽度         | $PW_{CLK}$           |              | 400 |     |     | ns |

| 选通脉冲宽度         | $PW_{STB}$           |              | 1   |     |     | us |

| 数据设置时间         | t <sub>SETUP</sub>   |              | 100 |     |     | ns |

| 数据保持时间         | t <sub>HOLD</sub>    |              | 100 |     |     | ns |

| 时间一选 通时间       | t <sub>CLK-STB</sub> | CLK ↑ →STB ↑ | 1   |     |     | us |

| 等待时间           | t <sub>WAIT</sub>    | CLK ↑ →CLK ↑ | 1   |     |     | us |

# 应用图