## **High Performance Digital FM Transceiver for Portable Devices**

| General Description |

|---------------------|

|---------------------|

The QN8006 is a high performance, low power, fully integrated single-chip stereo FM transceiver designed for cell phones, PMP/PNDs, and portable radios. It integrates both FM receiving and transmitting functions, auto-seek and clear channel scan, and antenna tuning to ease matching in real applications. Advanced digital architecture enables superior receiver sensitivity, crystal clear audio, unsurpassed spectral purity, ultra-low harmonic and spurious levels, and high immunity to TDMA burst noise.

With its small footprint, minimal external component count and multiple clock frequency support, the QN8006 is easy to integrate into a variety of small form-factor low power portable applications. An integrated voltage regulator enables direct connection to a battery and provides high PSRR for superior noise suppression. A low-power Standby mode extends battery life. ESD protection is on all pins. The QN8006 is fabricated in highly reliable CMOS technology.

## Key Features

#### Worldwide FM Band Receive and Transmit

- 76 MHz ~ 108 MHz full band tuning in 50/100/200 kHz step sizes

- 50/75μs pre-emphasis and de-emphasis

#### • High Performance FM Receiver (FMR)

- Superior sensitivity:  $7.2\mu V_{EMF}$

- High SNR: 66dB Stereo

- Ultra Low THD: 0.03% High interference rejection

- Integrated adaptive noise cancellation (SNC, HC SM)

- · Auto channel seek

#### • High Performance FM Transmitter (FMT)

- 66dB Stereo SNR, 0.03% THD

- Maximum 121dBµVp RF output level with 42dB adjustable range

- Integrated Clear Channel Scan

#### • RDS/RBDS Transmit & Receive

• Supports US and European data service, including TMC (Traffic Messaging Channel)

#### • Very Low Power Consumption

- 9.2mA (Transmit Mode), 17mA (Receive Mode)

- Integrated voltage regulator, direct connect to battery

- Power saving IDLE and Standby modes

- Low shutdown leakage current

#### • Flexible Audio Interfaces

- Digital audio interface supports I<sup>2</sup>S and a variety of PCM data formats with 4 different data rates

- Programmable analog audio input/output

- Integrated audio AGC and soft clipping

#### • Ease of Integration

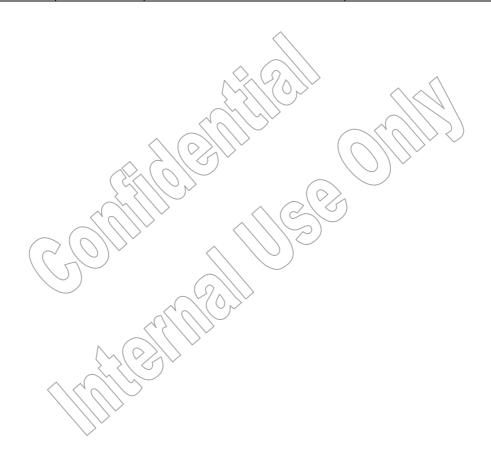

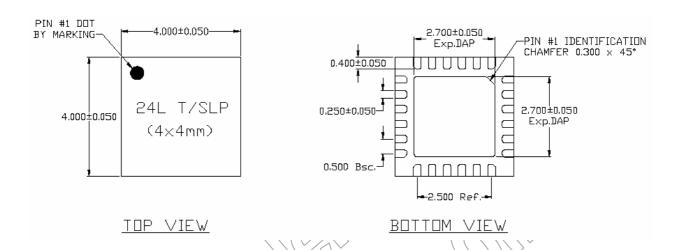

- Small footprint, 4 x 4 x 0.85mm OFN24

- Multiple crystal frequencies supported

- 2-wire and 3-wire control interfaces

#### Robust Operation

- $-25^{\circ}C$  to  $+85^{\circ}C$  operation

- ESD protection on all input and output pads

Typical Applications \_

- Cell Phones / PDAs / Smart Phones

- Portable Audio & Media Players

- GPS Personal Navigation Devices

- Automotive and Accessories

### **CONTENTS**

| 1 | Functional Block Diagram                          | 4  |

|---|---------------------------------------------------|----|

| 2 | Pin Assignments                                   | 5  |

| 3 | Electrical Specifications                         | 7  |

|   | 3.1 I <sup>2</sup> S Interface Timing             | 17 |

| 4 | Functional Description                            | 21 |

|   | 4.1 Transmit Mode                                 | 21 |

|   | 4.2 Receive Mode                                  | 21 |

|   | 4.3 Idle and Standby Mode                         | 21 |

|   | 4.4 Audio Interface                               | 21 |

|   | 4.5 Audio Processing  4.6 Channel Setting         | 22 |

|   | 4.6 Channel Setting                               | 23 |

|   | 4.7 RDS/RBDS                                      | 24 |

| 5 | Control Interface Protocol                        | 25 |

|   |                                                   | 25 |

|   | 5.2 3-Wire Serial Control Interface               |    |

| 6 | Digital Audio Interface Protocol                  |    |

| Ü | 6.1 Introduction.                                 | 27 |

|   | 6.2 I <sup>2</sup> S BUS Signal Description       | 27 |

|   | 6.3 I <sup>2</sup> S Interface Timing Description | 28 |

|   | 0.5 1 5 Interface Triming Description             | 20 |

|   | 6.3.1 MSB-Justified (Format 0)                    | 28 |

|   | 6.3.2 I <sup>2</sup> S (Format 1)                 | 28 |

|   | 6.3.3 DSP1 (Format 2)                             | 29 |

|   | 6.3.4 DSP2 (Format 3)                             | 29 |

|   | 6.3.5 LSB-Justified (Format 4)                    |    |

| _ |                                                   |    |

| 7 | User Control Registers                            | 30 |

| 8 | Package Description                               | 55 |

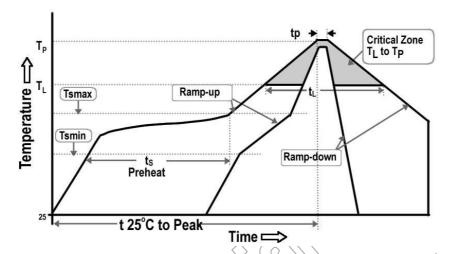

| 9 | Solder Reflow Profile                             | 57 |

|   | 9.1 Package Peak Reflow Temperature               | 57 |

|   | 9.2 Classification Reflow Profiles                | 57 |

|   | 9.3 Maximum Reflow Times                          | 58 |

#### **REVISION HISTORY**

| REVISION | CHANGE DESCRIPTION                                                                                                                                                                                                                        | DATE     |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0.11     | Initial from Qn8006/L datasheet v1.0                                                                                                                                                                                                      | 7/10/08  |

| 2.0      | B1 register set incorporated.                                                                                                                                                                                                             | 7/25/08  |

| 2.01     | Correct performance data in key feature section to accord with characteristics table                                                                                                                                                      | 8/25/08  |

| 2.01b    | Further explain PWROUT_CAL[7:0] at 0Ch;<br>Modify the CIDR1 05h 0/1/2/3 minor version<br>Modify the CIDR2 06h A/B/C/D major version;                                                                                                      | 9/18/08  |

| 2.01c    | Modify 2-wire to I <sup>2</sup> C, I2S to I <sup>2</sup> S, IDLE to IDLE, Pable 1 and format                                                                                                                                              | 02/04/09 |

| 2.02     | 1. Table 3 Vcc range:2.7~5.0 v, TYP:3.3 v; 2. In Section 4.1: Modify 124 to 121dBµVp. 3. In Section 4.5: Delete" When there is no audio signal for a pre-determined period, AGC will power down the transmitter."                         | 03/17/09 |

| 2.03     | Update the value in Section 2                                                                                                                                                                                                             | 06/15/09 |

| 2.04     | Modify the register PWROUT_CAL→ PAC_TARGET and the description                                                                                                                                                                            | 07/30/09 |

| 2.05     | Update the registers in Section 7.                                                                                                                                                                                                        | 08/05/09 |

| 2.06     | Modify the description of register PAC_TARGET                                                                                                                                                                                             | 10/12/09 |

| 2.07     | <ol> <li>Modify I<sup>2</sup>C to 2-wire;</li> <li>Table 6: Rin 75 Ω→ 5 kΩ;</li> <li>Add Reg 21h, Reg 22h, Reg 59h, Reg 5Ah.</li> <li>Update the grammar and syntax</li> <li>Modify V<sub>ain</sub> Max value; 1400 mV→2000 mV</li> </ol> | 11/23/09 |

#### **STATEMENT:**

Users are responsible for compliance with local regulatory requirements for low power unlicensed FM broadcast operation. Quintic is not responsible for any violations resulting from user's intentional or unintentional breach of regulatory requirements in personal or commercial use.

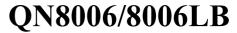

## 1 FUNCTIONAL BLOCK DIAGRAM

Figure 1: QN8006 Functional Blocks

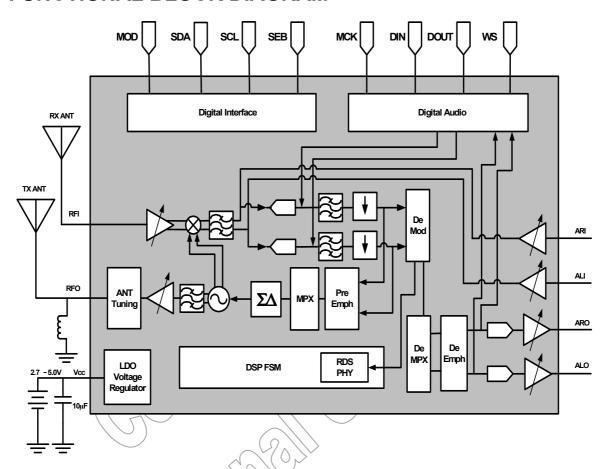

### **2 PIN ASSIGNMENTS**

#### **Table 1: Pin Descriptions**

| PINS | NAME     | DESCRIPTION                                                                                                                                                                            |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ALO      | Analog audio output – left channel (receiving mode only)                                                                                                                               |

| 2    | ARO      | Analog audio output – right channel (receiving mode only)                                                                                                                              |

| 3    | AUGND    | Audio ground                                                                                                                                                                           |

| 4    | ALI      | Analog audio input – left channel (transmitter mode only)                                                                                                                              |

| 5    | ARI      | Analog audio input – right channel (transmitter mode only)                                                                                                                             |

| 6    | AGND     | Analog ground                                                                                                                                                                          |

| 7    | RFI      | Receiver RF input                                                                                                                                                                      |

| 8    | RFGND    | RF ground                                                                                                                                                                              |

| 9    | RFO      | Transmitter RF output – connect to matched antenna.                                                                                                                                    |

| 10   | VIO      | IO voltage - specifies voltage limit for all digital pins.                                                                                                                             |

| 11   | CEN      | Chip enable: Chip power down if less than 0.6V, (see also MOD pin below) power up if voltage applied >min (0.7*VIO, 1.8V).                                                             |

| 12   | MOD      | Bus mode: HIGH = 3 wire serial operation. LOW = 2-wire serial operation Note: Both MOD=0 and CEN=0 to disable chip.                                                                    |

| 13   | MCK      | Master clock - for digital audio interface.                                                                                                                                            |

| 14   | DOUT/INT | Data out (receiving mode only), interrupt (transmitter mode only)                                                                                                                      |

| 15   | WS       | Word select (I <sup>2</sup> S mode only)                                                                                                                                               |

| 16   | XCLK (   | External clock input (register 49h, bit 4 must be HIGH)                                                                                                                                |

| 17   | XTAL1    | On-chip crystal driver port 1. If using an external clock source, connect this pin to ground.                                                                                          |

| 18   | XTAL2    | On-chip crystal driver port 2.  If using an external clock source, connect this pin to ground.                                                                                         |

| 19   | AGND     | Analog ground                                                                                                                                                                          |

| 20   | DIN/INT  | Data in (transmitter mode only), interrupt (receiving mode only)                                                                                                                       |

| 21   | SEB      | Serves as the bus enable pin in 3-wire serial mode; serves as the address select pin in 2-wire serial mode, SEB = Low for default address, SEB = High for register controlled address. |

| 22   | SCL      | Clock for 2-wire or 3-wire serial bus.                                                                                                                                                 |

| 23   | SDA      | Bi-directional data line for 2-wire or 3-wire serial bus.                                                                                                                              |

| 24   | VCC      | Voltage supply                                                                                                                                                                         |

| 25   | PAD      | Exposed pad, must be soldered to the ground on the PCB.                                                                                                                                |

## **3 ELECTRICAL SPECIFICATIONS**

**Table 2: Absolute Maximum Ratings**

| SYMBOL          | PARAMETER           | CONDITIONS                             | MIN  | MAX  | UNIT |

|-----------------|---------------------|----------------------------------------|------|------|------|

| $V_{bat}$       | Supply voltage      | VCC to GND                             | -0.3 | 5    | V    |

| V <sub>IO</sub> | Logic signals       | CEN, SEB, SCL, SDA,<br>MOD, GSL to GND | -0.3 | 3.6  | V    |

| $T_{s}$         | Storage temperature | $\langle$                              | -55  | +150 | °C   |

Table 3: Recommended Operating Conditions

| SYMBOL           | PARAMETER                      | CONDITIONS                        | MIN   | TYP  | MAX  | UNIT |

|------------------|--------------------------------|-----------------------------------|-------|------|------|------|

| Vcc              | Supply voltage                 | VCC to GND                        | 2.7   | 3.3  | 5.0  | V    |

| $T_{A}$          | Operating temperature          |                                   | (-25) |      | +85  | °C   |

| V <sub>ain</sub> | L/R channel input signal level | Single ended peak to peak voltage |       | 1000 | 2000 | mV   |

| RFin             | RF input level <sup>1</sup>    | Peak input voltage                |       |      | 0.3  | V    |

| $V_{IO}$         | Digital I/O voltage            |                                   | 1.6   |      | 3.6  | V    |

#### **Table 4: DC Characteristics**

$(\text{Vcc} = 2.7 \sim 5.0 \text{ V}, \text{ T}_{\text{A}} = -25 \sim 85 \,^{\circ}\text{C}, \text{ unless otherwise noticed}. \text{ Typical values are at Vcc} = 3.3 \text{V}, \text{ f carrier} = 88 \,\text{MHz} \text{ and } \text{T}_{\text{A}} = 25 \,^{\circ}\text{C}).$

| SYMBOL              | PARAMETER                                 | CONDITIONS              | MIN                           | TYP  | MAX                            | UNIT |

|---------------------|-------------------------------------------|-------------------------|-------------------------------|------|--------------------------------|------|

| $I_{RX}$            | Receive mode supply current <sup>1</sup>  | digital audio interface |                               | 15.3 |                                | mA   |

| 1 <sub>RX</sub>     | Receive mode supply editent               | analog audio interface  |                               | 17   |                                | mA   |

| $I_{TX}$            | Transmit mode supply current <sup>2</sup> | digital audio interface |                               | 6.8  |                                | mA   |

| 1 <sub>TX</sub>     | Transmit mode supply current              | analog audio interface  | 9.2                           |      | 12.9                           | mA   |

| $I_{\mathrm{IDLE}}$ | Idle mode supply current                  | Idle mode               |                               | 3.5  |                                | mA   |

| $I_{STBY}$          | Standby mode supply current               | Standby mode            | >                             | 350  |                                | μΑ   |

| $I_{PDN}$           | Power down leakage current                | power down              |                               | 5    | 15                             | μΑ   |

| Interface           | ^                                         |                         |                               |      | $\langle\rangle\rangle\rangle$ |      |

| $V_{\mathrm{OH}}$   | High level output voltage                 |                         | 0.9*V <sub>IQ</sub>           |      |                                | V    |

| V <sub>OL</sub>     | Low level output voltage                  |                         |                               |      | 0.1*V <sub>IO</sub>            | V    |

| $V_{\mathrm{IH}}$   | High level input voltage                  |                         | 1.7 or<br>0.7*V <sub>IO</sub> |      |                                | V    |

| $V_{IL}$            | Low level input voltage                   |                         |                               |      | 0.6                            | V    |

|                     | Type: RFI=10 dBµVp;                       |                         |                               |      |                                |      |

2. Max: RFO output level is 121dBuVp, Min. RFO=82 dBμVp..

## Table 5: AC Characteristics

$(\text{Vcc} = 2.7 \sim 5.0 \text{ V}, \text{T}_{\text{A}} = -25 \sim 85 \, ^{\circ}\text{C}, \text{unless otherwise noticed}.$  Typical values are at Vcc = 3.30 V and  $\text{T}_{\text{A}} = 25 \, ^{\circ}\text{C}$ ).

| SYMBOL                                                 | PARAMETERS                 | CONDITIONS                  | MIN                     | TYP | MAX | UNIT |  |  |

|--------------------------------------------------------|----------------------------|-----------------------------|-------------------------|-----|-----|------|--|--|

| F <sub>xtal</sub>                                      | Crystal or Clock frequency | Real-Time Clock             | 7.6 - 38.4 <sup>1</sup> |     | MHz |      |  |  |

| $F_{xtal\_err}$                                        | Crystal frequency accuracy | Over temperature, and aging | -20                     |     | 20  | ppm  |  |  |

| Notes: 1. See also XSEL[3:0] (register 03h, bits 3:0). |                            |                             |                         |     |     |      |  |  |

#### **Table 6: Transmitter Characteristics**

$(\text{Vcc} = 2.7 \sim 5.0 \text{ V}, \text{ T}_{\text{A}} = -25 \sim 85 \,^{\circ}\text{C}, \text{ unless otherwise noticed}. \text{ Typical values are at Vcc} = 3.3 \text{V}, \text{ f carrier} = 88 \,\text{MHz} \text{ and } \text{T}_{\text{A}} = 25 \,^{\circ}\text{C}).$

| SYMBOL                         | PARAMETERS                                    | CONDITIONS                                                                           | MIN  | TYP  | MAX  | UNIT  |

|--------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|------|------|------|-------|

| R <sub>audio_in</sub>          | Audio input impedance                         | At pin ALI and ARI                                                                   | 10   |      | 80   | kΩ    |

| $C_{audio\_in}$                | Audio input capacitance <sup>1</sup>          | At pin ALI and ARI                                                                   |      | 2    | 5    | pF    |

| G <sub>audio_In</sub>          | Audio input gain                              | RIN[1:0] = 01                                                                        | -1.5 |      | 15   | dB    |

| $\Delta G_{audio\_In}$         | Audio gain step                               | For any gain setting                                                                 | 0.5  | 1    | 1.5  | dB    |

| $	au_{	ext{emph}}$             | Pre-emphasis time                             | PETC = 1                                                                             | 71.3 | 75   | 78.7 | μs    |

| vempn                          | constant <sup>1</sup>                         | PETC = 0                                                                             | 47.5 | 50   | 52.5 | μο    |

|                                |                                               | MONO, $\Delta f = 22.5 \text{ kHz}$                                                  | >    | 65   |      |       |

| SNR <sub>audio_tx</sub>        | Tx audio SNR <sup>3</sup>                     | STEREO, $\Delta f = 67.5 \text{ kHz}$ , $\Delta f_{\text{pilot}} = 6.75 \text{ kHz}$ | ,    | 66   |      | dB    |

| THD <sub>audio_tx</sub>        | Tx audio THD <sup>3</sup>                     | STEREO, $\Delta t = 67.5 \text{ kHz}$ , $\Delta f_{\text{pilot}} = 6.75 \text{ kHz}$ |      | 0.03 | 0.1  | %     |

| $\alpha_{LR\_tx}$              | L/R separation <sup>2, 3</sup>                |                                                                                      | 40   | 45   |      | dB    |

| $\mathrm{B}_{\mathrm{LR\_tx}}$ | L/R channel imbalance 12                      | L and R channel gain imbalance at 1 kHz offset from DC                               |      |      | 1    | dB    |

| $M_{pilot}$                    | 19 kHz pilot modulation                       | Relative to 75 kHz deviation                                                         | 7    | 9.0  | 15   | %     |

| SUP <sub>sub</sub>             | 38 kHz sub-carrier <sup>2,3</sup> suppression |                                                                                      | 70   |      |      | dB    |

| $C_{tune}$                     | Output capacitance tuning range               |                                                                                      | 5    |      | 30   | pF    |

| P <sub>out</sub>               | RF output voltage-swing <sup>4</sup>          | RF Channel frequency = 88 MHz                                                        | 82   |      | 121  | dBμVp |

| $\Delta G_{RF\_Out}$           | Power gain step                               | Over process, temperature                                                            | 0.7  | 1.5  | 2.5  | dB    |

| $\Delta P_{out}$               | Power gain flatness                           | Over 76 MHz ~ 108 MHz                                                                | -2   |      | 2    | dB    |

|                                | PF                                            | 120 kHz to 240 kHz offset                                                            |      | -50  | -45  |       |

| $P_{\text{mask}}$              | RF output spectrum mask <sup>5</sup>          | 240 kHz to 600 kHz offset                                                            |      | -55  | -45  | dBc   |

|                                |                                               | >600 kHz offset                                                                      |      |      | -45  |       |

| $F_{rf}$                       | RF channel frequency                          |                                                                                      | 76   |      | 108  | MHz   |

| $F_{ch}$                       | Channel frequency step                        |                                                                                      | 50   | 100  | 200  | kHz   |

| F <sub>err</sub>               | Channel center frequency accuracy             |                                                                                      | -2   |      | 2    | kHz   |

| $F_{perr}$                     | Pilot Tone frequency accuracy <sup>1</sup>    |                                                                                      | -2   |      | 2    | Hz    |

| $F_{pk}$                       | Modulation peak frequency deviation           |                                                                                      |      | 75   |      | kHz   |

#### Notes:

- 1. Guaranteed by design.

- 2. Stereo ( $ST_MO_TX = 0$ ).

- 3. 1000mVp-p, 1 kHz tone at ALI pin, no input signal at ARI pin.

- 4. Into matched antenna (see application note for details).

- 5. Within operating band 76 MHz to 108 MHz.

- 6. Value set with GAIN\_TXPLT [5:0] (reg. 0Fh, bits 5:0). The user must conform to local regulatory requirements for low-power unlicensed FM broadcast operation when setting this value.

**Table 7: Receiver Characteristics**

$(Vcc = 2.7 \sim 5.0 \text{ V}, T_A = -25 \sim 85 ^{\circ}\text{C}, \text{ unless otherwise noticed}. \text{ Typical values are at } Vcc = 3.3 \text{V}, \text{ f carrier=88 MHz and } T_A = 25 ^{\circ}\text{C}).$

| SYMBOL                     | PARAMETERS                  | CONDITIONS                                                                           | MIN  | TYP   | MAX                     | UNIT                 |

|----------------------------|-----------------------------|--------------------------------------------------------------------------------------|------|-------|-------------------------|----------------------|

| $S_{RX}$                   | FM sensitivity              | (S+N)/N = 26dB                                                                       |      | 1.2   | 11/                     | $\mu V_{\text{EMF}}$ |

| $S_{RDS}$                  | RDS sensitivity             | BER≤5%, average over-2000 blocks                                                     |      | 8.9   | $\rangle\rangle\rangle$ | $\mu V_{\text{EMF}}$ |

| IP3                        | Input referred IP3          | At maximum gain                                                                      |      | ) 105 |                         | dΒμV                 |

| Rej <sub>AM</sub>          | AM suppression              |                                                                                      |      | 52    |                         | dB                   |

| $R_{in}$                   | RF input impedance          | At pin RFI                                                                           | 5)   | 5     |                         | kΩ                   |

| $S_{RX\_Adj}$              | Adjacent channel rejection  | 200 kHz offset                                                                       | )    | 40    |                         | dB                   |

| $S_{RX\_Alt}$              | Alternate channel rejection | 400 kHz offset                                                                       |      | 40    |                         | dB                   |

|                            |                             | MONO, $\Delta f = 22.5 \text{ kHz}^1$                                                |      | 65    |                         |                      |

| SNR <sub>audio_in</sub>    | Audio SNR                   | STEREO, $\Delta f = 67.5 \text{ kHz}$ , $\Delta f_{\text{pilot}} = 6.75 \text{ kHz}$ |      | 66    |                         | dB                   |

|                            |                             | MONO, $\Delta f = 22.5 \text{ kHz}$                                                  |      | 0.03  |                         | %                    |

| THD <sub>audio_in</sub>    | Audio THD                   | STEREO, $\Delta f = 67.5 \text{ kHz}$ , $\Delta f_{\text{pilot}} = 6.75 \text{ kHz}$ |      | 0.03  |                         | %                    |

| $\alpha_{LR\_in}$          | L/R separation              |                                                                                      | 40   | 47    |                         | dB                   |

| Att <sub>Pilot</sub>       | Pilot rejection             |                                                                                      |      | 65    |                         | dB                   |

| $\mathrm{B}_{\mathrm{LR}}$ | L/R channel imbalance       | L and R channel gain imbalance at 1 kHz offset from DC                               |      |       | 1                       | dB                   |

| - T                        | De-emphasis time            | PETC = 1                                                                             | 71.3 | 75    | 78.7                    | μs                   |

| $	au_{	ext{emph}}$         | constant                    | PETC = 0                                                                             | 47.5 | 50    | 52.5                    | μs                   |

| V <sub>audio_out</sub>     | Audio output voltage        | Peak-Peak, single ended                                                              | 0. 5 | 1     | 1.4                     | V                    |

| R <sub>LOAD</sub>          | Audio output impedance      |                                                                                      | 0.6  | 5     |                         | kΩ                   |

| C <sub>audio_out</sub>     | Audio output capacitance    |                                                                                      | 5    |       | 20                      | pF                   |

| RSSI <sub>err</sub>        | RSSI uncertainty            |                                                                                      | -3   |       | 3                       | dB                   |

| SYMBOL            | PARAMETERS | CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------|------------|------------|-----|-----|-----|------|

| Notes:<br>1. FORC | CE_MO=0;   |            |     |     |     |      |

#### **Table 8: Timing Characteristics**

$(Vcc = 2.7 \sim 5.0 \text{ V}, T_A = -25 \sim 85 \, ^{\circ}\text{C}, \text{ unless otherwise noticed}. \text{ Typical values are at Vcc} = 3.3 \text{V} \text{ and } T_A = 25 \, ^{\circ}\text{C}).$

| SYMBOL               | PARAMETER                             | CONDITIONS                                                                     | MIN | TYP         | MAX | UNIT |

|----------------------|---------------------------------------|--------------------------------------------------------------------------------|-----|-------------|-----|------|

| $	au_{	ext{pup}}$    | Chip power-up time <sup>1</sup>       | From rising edge of CEN to PLL settled and transmitter ready for transmission. |     |             | 0.6 | Sec  |

| $	au_{ m astby}$     | Auto Standby time <sup>2</sup>        | TMOUT [1:0] = 00  TMOUT [1:0] = 01  TMOUT [1:0] = 10  TMOUT [1:0] = 11         |     | 1 3 5 Never |     | Min  |

| $	au_{ m chsw}$      | Channel switching time <sup>1</sup>   | From any channel to any channel.                                               |     | 2)///       | 0.1 | Sec  |

| Transmitte           | r Timing                              |                                                                                |     |             |     |      |

| $	au_{ m wkup}$      | Wake-up time from standby to transmit |                                                                                |     | 25          | 200 | msec |

| $	au_{\mathrm{CCS}}$ | Clear channel scan time               | Per channel.                                                                   |     | 5           |     | msec |

| Receiver Ti          | iming                                 |                                                                                |     |             |     |      |

| $	au_{ m wkup}$      | Wake-up time from standby to receive  | Standby to RX mode.                                                            |     | 200         |     | msec |

| $	au_{ m trx}$       | Mode switch time from receive to/from | RX mode to TX mode.                                                            |     | 500         |     | μsec |

| VIIX                 | transmit                              | TX mode to RX mode.                                                            |     | 100         |     | msec |

| $	au_{	ext{tune}}$   | Tune time                             | Per channel, including Seek <sup>1,3</sup> .                                   |     | 5           |     | msec |

#### Notes:

- 1. Guaranteed by design.

- 2. Chip automatically goes from IDLE to standby mode; TMOUT = 11 equivalent to auto standby disabled.

- 3. More time is required until audio is output.

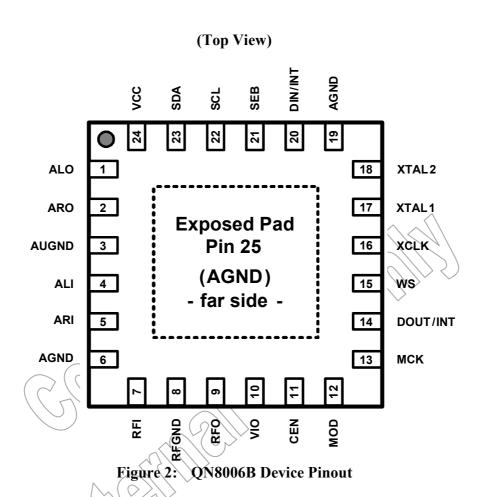

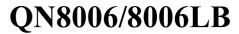

#### **Table 9: 2-Wire Interface Timing Characteristics**

$(\text{Vcc} = 2.7 \sim 5.0 \text{ V}, \text{ T}_{\text{A}} = -25 \sim 85 \, ^{\circ}\text{C}, \text{ unless otherwise noticed}. \text{ Typical values are at Vcc} = 3.3 \text{V} \text{ and } \text{T}_{\text{A}} = 25 \, ^{\circ}\text{C}).$

| SYMBOL            | PARAMETER                                               | CONDITIONS            | MIN | TYP | MAX | UNIT |

|-------------------|---------------------------------------------------------|-----------------------|-----|-----|-----|------|

| $f_{SCL}$         | 2-wire clock frequency                                  |                       |     |     | 400 | kHz  |

| $t_{LOW}$         | Clock Low time                                          |                       | 0.5 |     |     | μs   |

| $t_{ m HI}$       | Clock High time                                         |                       | 0.5 |     |     | μs   |

| $t_{\mathrm{ST}}$ | SCL input to SDA falling edge start <sup>1,3</sup>      |                       | 0.8 |     |     | μs   |

| $t_{ m STHD}$     | SDA falling edge to SCL falling edge start <sup>3</sup> | $\wedge$              | 0.6 |     |     | μs   |

| $t_{rc}$          | SCL rising edge <sup>3</sup> Level from 30% to 70%      |                       |     |     | 300 | ns   |

| $t_{ m fc}$       | SCL falling edge <sup>3</sup>                           | Level from 70% to 30% |     |     | 300 | ns   |

| t <sub>dtHD</sub> | SCL falling edge to next SDA rising edge <sup>3</sup>   |                       | 20  |     |     | ns   |

| $t_{ m dtc}$      | SDA rising edge to next SCL rising edge <sup>3</sup>    |                       |     |     | 900 | ns   |

| t <sub>stp</sub>  | SCL rising edge to SDA rising edge <sup>2,3</sup>       |                       | 0.6 |     |     | μs   |

| $t_{\mathrm{w}}$  | Duration before restart <sup>3</sup>                    | ()                    | 1.3 |     |     | μs   |

| C <sub>b</sub>    | SCL, SDA capacitive loading <sup>3</sup>                |                       | 2)  | 10  |     | pF   |

#### Notes:

- 1. Start signaling of 2-wire interface.

- 2. Stop signaling of 2-wire interface.

- 3. Guaranteed by design.

Figure 3: 2-Wire Serial Control Interface Timing Diagram

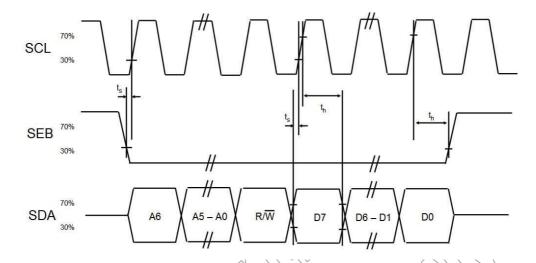

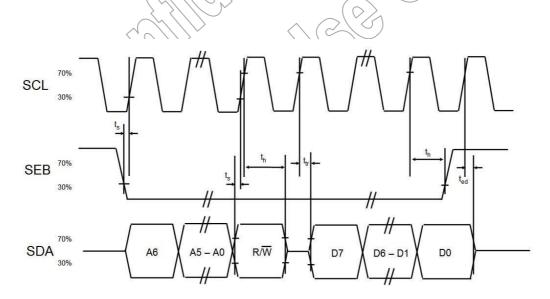

### **Table 10: 3-Wire Interface Timing Characteristics**

(  $Vcc = 2.7 \sim 5.0 \text{ V}$ ,  $T_A = -25 \sim 85$  °C, unless otherwise noticed. Typical values are at Vcc = 3.3 V and  $T_A = 25$  °C).

| SYMBOL          | PARAMETER                                                  | CONDITIONS         | MIN | TYP | MAX | UNIT |

|-----------------|------------------------------------------------------------|--------------------|-----|-----|-----|------|

| $f_{CLK}$       | Bus clock frequency                                        |                    |     |     | 2.5 | MHz  |

| $t_{ m HI}$     | SCL high time                                              |                    | 50  |     |     | ns   |

| $t_{ m LOW}$    | SCL low time                                               |                    | 25  |     |     | ns   |

| ts              | SEB and SDA falling edge to clock rising edge <sup>1</sup> |                    | 20  |     |     | ns   |

| $t_{\rm h}$     | Data holding time <sup>1</sup>                             |                    | 10  |     |     | ns   |

| t <sub>tr</sub> | SCL rising edge to SDA output valid <sup>1</sup>           | Only in read mode. | 2   | ^   | 50  | ns   |

| $t_{\rm ed}$    | SCL rising edge to SDA output high Z <sup>1</sup>          |                    | 2   |     | 25  | ns   |

| Notes:          | anteed by design.                                          |                    |     |     |     |      |

Figure 4: 3-Wire Serial Control Interface Write Timing Diagram

Figure 5: 3-Wire Serial Control Interface Read Timing Diagram

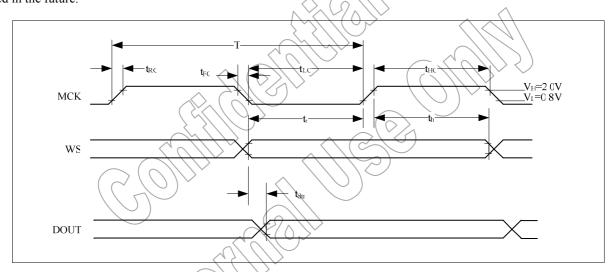

#### **Table 11: Digital Audio Interface Timing Characteristics**

#### Master Clock:

(  $Vcc = 2.7 \sim 5.0 \text{ V}$ ,  $T_A = -25 \sim 85$  °C, unless otherwise noticed. Typical values are at Vcc = 3.3 V and  $T_A = 25$  °C).

| SYMBOL                   | PARAMETER           | CONDITIONS        | MIN | TYP | MAX   | UNIT |

|--------------------------|---------------------|-------------------|-----|-----|-------|------|

| f <sub>CLK_M</sub>       | Bus clock frequency |                   |     |     | 3.072 | MHz  |

| $	au_{rise\_M}$          | Rise-time           |                   |     |     | 0.5   | ns   |

| $	au_{\mathrm{fall\_M}}$ | Fall-time           |                   |     |     | 0.5   | ns   |

| F <sub>err_M</sub>       | Frequency accuracy  | According to PLL. |     |     | 100   | ppm  |

#### Slave Clock:

(  $Vcc = 2.7 \sim 5.0 \text{ V}$ ,  $T_A = -25 \sim 85 \,^{\circ}\text{C}$ , unless otherwise noticed. Typical values are at Vcc = 3.3 V and  $T_A = 25 \,^{\circ}\text{C}$ )

| SYMBOL                   | PARAMETER           | CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------------|---------------------|------------|-----|-----|-----|------|

| $f_{CLK\_S}$             | Bus clock frequency |            |     |     | 10  | MHz  |

| $\tau_{rise\_S}$         | Rise-time           |            |     |     | 1.5 | ns   |

| $	au_{\mathrm{fall\_S}}$ | Fall-time           |            |     |     | 1.5 | ns   |

| $F_{err\_S}$             | Frequency accuracy  |            |     |     | 100 | ppm  |

## 3.1 I<sup>2</sup>S Interface Timing

Note: The terms 'transmitter' and 'receiver' as described below are from the QN8006's point of view.

Either the QN8006 or the external device can act as the system master by providing the necessary clock signals. The slave will usually derive its internal clock signal from an external clock input. This means, taking into account the propagation delay between the master clock and the data and/or word-select signals, that the total delay is simply the sum of:

- The delay between the external (master) clock and slave's internal clock;

- The delay between the internal clock and the data and/or word-select signals.

For data and word-select inputs, the external to internal clock delay is of no consequence because it only lengthens the effective set-up time (see Figure 6). The major part of the time margin is to accommodate the difference between the propagation delay of the transmitter, and the time required to set up the receiver. All timing requirements are specified relative to the clock period or to the minimum allowed clock period of a device. This means that higher data rates can be used in the future.

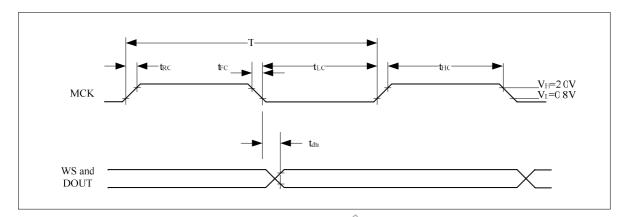

Figure 6: Timing for QN8006 as I<sup>2</sup>S Slave and Transmitter

Table 12: Timing for QN8006 as I<sup>2</sup>S Slave and Transmitter

| SYMBOL       | PARAMETER                     | CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------|-------------------------------|------------|-----|-----|-----|------|

| T            | I <sup>2</sup> S clock period |            | 100 |     |     | ns   |

| $t_{ m LC}$  | Clock low time                |            | 10  |     |     | ns   |

| $t_{ m HC}$  | Clock high time               |            | 10  |     |     | ns   |

| $t_{\rm s}$  | WS setup time                 |            | 10  |     |     | ns   |

| $t_{\rm h}$  | WS hold time                  |            | 5   |     |     | ns   |

| $t_{ m dtr}$ | SD delay time                 |            |     |     | 10  | ns   |

| $t_{RC}$     | Clock rise-time               |            |     |     | 5   | ns   |

| $t_{FC}$     | Clock fall-time               |            |     |     | 5   | ns   |

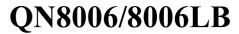

Figure 7: Timing for QN8006 as I<sup>2</sup>S Master and Transmitter

Table 13: Timing for QN8006 as I<sup>2</sup>S Master and Transmitter

| SYMBOL           | PARAMETER                     | CONDITIONS | MIN | TYP        | MAX | UNIT |

|------------------|-------------------------------|------------|-----|------------|-----|------|

| T                | I <sup>2</sup> S clock period |            | 330 |            |     | ns   |

| $t_{ m LC}$      | Clock low time                |            | 120 |            |     | ns   |

| $t_{HC}$         | Clock high time               |            | 120 | $\bigcirc$ |     | ns   |

| t <sub>dtr</sub> | WS and SD delay time          |            |     |            | 10  | ns   |

| $t_{RC}$         | Clock rise-time               |            |     |            | 5   | ns   |

| $t_{FC}$         | Clock fall-time               |            |     |            | 5   | ns   |

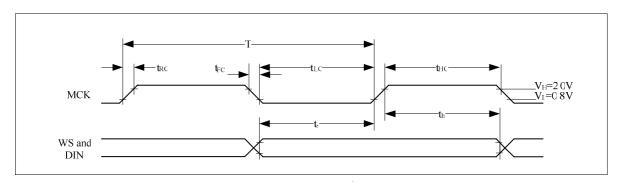

Figure 8: Timing for QN8006 as 12S Slave and Receiver

Table 14: Timing for QN8006 as I<sup>2</sup>S Slave and Receiver

| SYMBOL      | PARAMETER                        | CONDITIONS | MIN  | TYP                     | MAX | UNIT |

|-------------|----------------------------------|------------|------|-------------------------|-----|------|

| T           | I <sup>2</sup> S clock frequency |            | 100  |                         |     | ns   |

| $t_{LC}$    | Clock low time                   |            | 10   |                         |     | ns   |

| $t_{HC}$    | Clock high time                  |            | 10   | $\langle \cdot \rangle$ |     | ns   |

| $t_{\rm s}$ | WS and SD setup time             |            | 10   |                         |     | ns   |

| $t_h$       | WS and SD hold time              |            | ) \5 |                         |     | ns   |

| $t_{RC}$    | Clock rise-time                  |            |      |                         | 5   | ns   |

| $t_{FC}$    | Clock fall-time                  |            |      |                         | 5   | ns   |

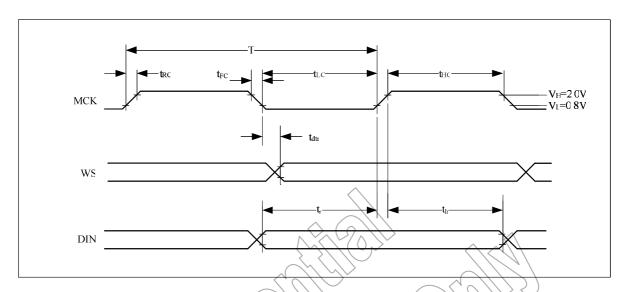

Figure 9: Timing for QN8006 as I<sup>2</sup>S Master and Receiver

Table 15: Timing for QN8006 as I<sup>2</sup>S Master and Receiver

|              | (, )                          |               | 101 |     |     |      |

|--------------|-------------------------------|---------------|-----|-----|-----|------|

| SYMBOL       | PARAMETER                     | CONDITIONS    | MIN | TYP | MAX | UNIT |

| T            | I <sup>2</sup> S clock period |               | 330 |     |     | ns   |

| $t_{ m LC}$  | Clock low time                |               | 120 |     |     | ns   |

| $t_{HC}$     | Clock high time               |               | 120 |     |     | ns   |

| $t_{\rm s}$  | SD setup time                 |               | 10  |     |     | ns   |

| $t_h$        | SD hold time                  |               | 5   |     |     | ns   |

| $t_{ m dtr}$ | WS delay time                 | $\rightarrow$ |     |     | 10  | ns   |

| $t_{RC}$     | Clock rise time               |               |     |     | 5   | ns   |

| $t_{FC}$     | Clock fall-time               |               |     |     | 5   | ns   |

#### 4 FUNCTIONAL DESCRIPTION

The QN8006 is a high performance, low power, single chip FM transceiver IC that supports worldwide FM broadcast band operation. It has transmit/receive modes for normal broadcasting/tuning as well as IDLE and standby modes for saving power. RDS/RBDS data service is also supported in both transmit and receive modes.

#### 4.1 Transmit Mode

The QN8006 transmitter uses a highly digitized architecture. The input left and right analog audio signals are first adjusted by two automatic gain controlled (AGC) amplifiers, and then digitized by two high resolution ADCs into the digital domain. If a digital audio interface is used, the analog input circuits and ADCs will be bypassed. Pre-emphasis, soft clipping and MPX encoding are then performed. If RDS mode is enabled, the RDS signal will also be mixed with the MPX signal and the combined output will be fed into a high performance digital FM modulator which generates FM signal at RF carrier frequency. The FM signal is then filtered and amplified by the PA.

The QN8006 can deliver up to  $121dB\mu Vp$  output signal to an external antenna and/or matching network. An RF VGA provides 42 dB of output power control range in 1.5dB steps and can be programmed through the serial control bus. Output power control and in-band power flatness can be easily achieved by a calibration circuit. This wide range of control allows for various antenna configurations such as loop, monopole, or meandering traces on PCB. An integrated RF bandpass filter ensures optimal output spectal purity.

#### 4.2 Receive Mode

The QN8006 receiver also uses a highly digitized low-IF architecture, allowing for the elimination of external components and factory adjustments.

The received RF signal is first amplified by an integrated LNA and then quadrature down-converted to IF. An integrated IF channel filter then rejects out-of-channel interference signals. AGC is also performed simultaneously to optimize the signal to noise ratio as well as linearity and interference rejection. The filtered signal is digitized and further processed with a digital FM demodulator and MPX decoder. Audio processing is then performed based on received signal quality and channel condition. Two high-quality audio DACs are integrated on chip and will be used if an analog interface is used and will be bypassed in case of a digital audio interface. The RDS signal will also be decoded if RDS reception is enabled.

## 4.3 Idle and Standby Mode

The QN8006 features low power IDLE and STANDBY modes for fast turn around and power saving. After power up, the QN8006 will enter IDLE mode automatically. If there is no transmitting or receiving requirement in a pre-determined time period, the QN8006 will enter STANDBY mode automatically. The auto-standby function can be enabled or disabled through the serial control interface.

#### 4.4 Audio Interface

The QN8006 supports both analog and digital audio interfaces in four different configurations, namely, analog transmit/analog receive, analog transmit/digital receive, digital transmit/analog receive and digital transmit/digital receive, thus, providing maximum flexibility in real applications.

#### **Analog Audio Interface**

The QN8006 has a highly flexible analog audio interface. In transmit mode, for audio input, the signal is AC coupled with a 3dB corner frequency less than 50Hz. It has 4 different input impedances and 16.5 dB adjustable gain range (in

1.5dB step) to optimize the SNR and linearity. The gain setting can be controlled automatically by integrated AGC or manually set through serial interface.

In receive mode, the single ended audio output level is 1V peak to peak and will be AC coupled to external audio driver.

#### **Digital Audio Interface**

With digital audio, the interface operates in slave mode and supports MSB-Justified, LSB-Justified, I<sup>2</sup>S, DSP1, and DSP2. The four interface lines are MCK, DIN, DOUT, and WS. MCK and WS can be tri-stated to allow for multiplexing.

#### 4.5 Audio Processing

The QN8006 supports both transmit and receive mode audio processing.

In transmit mode, audio AGC, programmable pre-emphasis, and soft clipping are supported. The AGC state machine will detect the signal level and control the VGA gain to optimize both SNR and THD. A saturation indicator is also integrated which will be asserted when the input signal is out of the range of AGC. A soft clipping feature provides graceful performance degradation when the signal level is higher than a pre-determined level.

Stereo signal is generated by the MPX circuit. It combines the left and right channel signals in the following way:

$$m(t) = [L(t) + R(t)] + [L(t) - R(t)] \sin(4\pi ft + 2\theta_0) + \alpha \sin(2\pi ft + \theta_0) + d(t) \sin(6\pi ft + 3\theta_0)$$

Here, L(t) and R(t) correspond to the audio signals on left and right channels respectively, f=19 kHz,  $\theta$  is the initial phase of pilot tone and  $\alpha$  is the magnitude of pilot tone, and d(t) is RDS signal. In mono mode, only the L+R portion of audio signal is transmitted. The 19 kHz pilot tone is generated by the MPX circuit which contributes 9% of peak modulation, and RDS signal will contribute 2.1% of peak modulation.

In receive mode, stereo noise cancellation (SNC), high cut control (HCC) and soft mute (SM) are supported. Stereo noise suppression is achieved by gradually combining the left and right signals to be a mono signal as the received signal quality degrades. SNC, HCC and SM are controlled by SNR and multipath channel estimation results.

Pre-emphasis and de-emphasis functions are also integrated with both 75µs and 50µs time constants. The time constant can be programmed through the serial control interface.

### 4.6 Channel Setting

The QN8006 supports both auto tuning/scan and manual channel settings.

#### **Manual Channel Setting**

By programming channel index CH[9:0], the RF channel can be set to any frequency between 76 MHz  $\sim$  108 MHz in 50 kHz steps. The channel index and RF frequency have the following relationship:

$F_{RF} = (76 + 0.05 \text{ x Channel Index})$ , where  $F_{RF}$  is the RF frequency in MHz.

The QN8006 has an integrated crystal oscillator and supports various crystal frequencies. Alternatively, the QN8006 can be driven externally by various clock frequencies.

#### **Clear Channel Scan**

The QN8006 can automatically find the clearest channel and return the channel information for FM transmission. The start, stop and frequency step of searching as well as upward or downward searching can be programmed through the serial interface.

#### **Auto Tuning**

In receive mode, the QN8006 can automatically tune to stations having good signal quality. The start, stop and frequency step of tuning as well as upward or downward tuning can be programmed through the serial interface.

#### 4.7 RDS/RBDS

The QN8006 supports RDS/RBDS data transmitting and receiving, including station ID, Meta data, TMC information, etc. The integrated RDS processor performs all symbol encoding/decoding, block synchronization, error detection and correction functions. RDS/RBDS data communicates with an external MCU through the serial control interface.

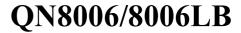

When the chip is used as an FM receiver, the internal RDS buffer (the entire RDS Group (8 bytes) is full, an Interrupt signal is generated. The signal waveform is shown in Figure 10. The user can also check the RDS buffer space by reading the RDS RXTXUPD bit in the STATUS2 register (reg. 1Bh [7]).

When the chip is used as an FM transmitter (RDS TX), ping-pong buffers are used so that the user can write into one buffer while the RDS data in the other buffer is being transmitted. When the internal RDS buffer (8 bytes) is full, an Interrupt signal is generated. The signal waveform is shown in Figure 10. The user should wait for the Interrupt signal (INT) before toggling the RDSTXRDY bit in the SYSTEM2 register (reg. 01h [2]). Alternatively, the user can also check the RDS buffer space by reading the RDS RXTXUPD bit in the STATUS2 register (reg. 1Bh [7]).

Figure 10: Interrupt Output

RDS/RSBS is not available in the QN8006LB.

#### 5 CONTROL INTERFACE PROTOCOL

The QN8006 supports 2-wire and 3-wire serial interfaces. The interface selection is controlled by the MOD pin which determines whether a 2-wire or a 3-wire serial interface will be used. MOD = HIGH selects a 3-wire bus and LOW selects a 2-wire bus. At power-on, all register bits are set to default values.

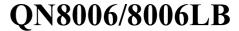

#### 5.1 2-Wire Serial Control Interface

The 2-wire bus is a simple bi-directional bus interface. The bus requires only serial data (SDA) and serial clock (SCL) signals. The bus is 8-bit oriented. Each device is recognized with a unique address. Each register is also recognized with a unique address. A third line (SEB) is used to choose the device address configuration. SEB = LOW selects the default address (0101011), SEB = HIGH selects register defined addressing. The L2 bus operates with a maximum frequency of 400 kHz. Each data put on the SDA must be 8 bits long (Byte) from MSB to LSB and each byte sent should be acknowledged by an "ACK" bit. In case a byte is not acknowledged, the transmitter should generate a stop condition or restart the transmission. If a stop condition is created before the whole transmission is completed, the remaining bytes will keep their old setting. In case a byte is not completely transferred, it will be discarded.

Data transfer to and from the QN8006 can begin when a start condition is created. This is the case if a transition from HIGH to LOW on the SDA line occurs while the SCL is HIGH. The first byte transferred represents the address of the IC plus the data direction. The default IC address is 0101011. A LOW LSB of this byte indicates data transmission (WRITE) while a HIGH LSB indicates data request (READ). This means that the first byte to be transmitted to the QN8006 should be "56" for a WRITE operation or "57" for a READ operation.

The second byte is the starting register address (N) for write/read operation. The following bytes are register data for address N, N+1, N+2, etc. There is no limit on the number of bytes in each transmission. A transmission can be terminated by generating a stop condition, which is SDA transition from LOW to HIGH while SCL is HIGH. For write operation, master stops transmission after the last byte. For read operation, master doesn't send ACK after receiving the last read back byte; then stops the transmission.

The following timing diagram is for both write and read

Figure 11: 2-wire Serial Control Interface Protocol

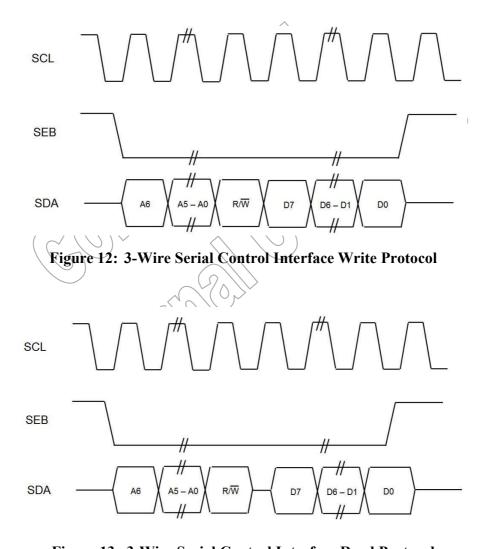

#### 5.2 3-Wire Serial Control Interface

For 3-wire serial operation, a transfer begins when the SEB pin is set LOW on a rising SCL edge. The control word is latched internally on rising SCL edges and is 8 bits in length, comprised of a 7-bit register address A6:A0, and a read/write bit (read = 1, write = 0). The ordering of the control word is A6:A0, R/W as shown in Figure 11.

For write operations, the serial control word is followed by an 8-bit data word and is latched internally on rising SCL edges. For read operations, a bus turn-around of half a cycle is followed by an 8-bit data word shifted out on rising SCL edges. The transfer ends on the rising SCL edge after SEB is set HIGH. After the 16th data bit, a full clock with both rising and falling edges is needed to shift in the control word.

Figure 13: 3-Wire Serial Control Interface Read Protocol

#### 6 DIGITAL AUDIO INTERFACE PROTOCOL

#### 6.1 Introduction

The QN8006 uses an I<sup>2</sup>S interface to transfer audio data to and from the external source.

- Master or Slave modes are supported.

- Multiple data widths are supported: 8, 16, 24, and 32 bits.

- Multiple data alignments are supported: I<sup>2</sup>S, DSP1, DSP2, MSB-Justified, and LSB-Justified modes. All the above 5 modes are supported when the QN8006 works as a receiver, and only I<sup>2</sup>S normal and DSP2 mode is supported when the QN8006 is a transmitter.

- The terms 'transmitter' and 'receiver' as described below are from the QN8006's point of view.

## 6.2 I<sup>2</sup>S BUS Signal Description

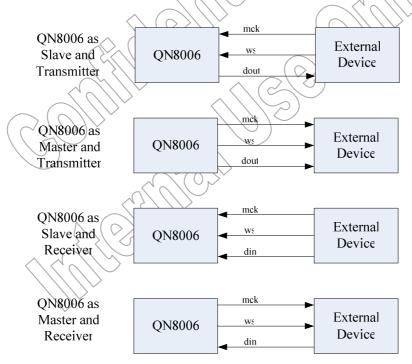

A 3-line serial bus is used consisting of a line for two time-multiplexed data channels, a word select line, and a clock line. The following figure shows how to use these three signals in the QN8006.

Figure 14: Top Level Block Diagram of I<sup>2</sup>S

In Master mode, the serial clock signal SCK and the word selection signal WS are generated by the QN8006 and are output to the external device. In Slave mode, those two signals are input signals from the external device.

As transmitter, the QN8006 sends the serial data to the external device by the SD signal. As receiver, it receives the serial data from the external device by the SD signal.

## 6.3 I<sup>2</sup>S Interface Timing Description

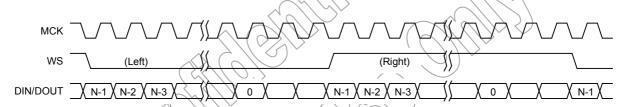

The word select line indicates the channel being transmitted:

- WS = 0; channel 1(left);

- WS = 1; channel 2(right).

WS sent by the transmitter is synchronized by the trailing (HIGH-to-LOW) edge of the serial clock signal and is latched into the receiver on the leading (LOW-to-HIGH) edge of the serial clock signal.

The serial data signal SD has the same timing requirement as the WS signal. It is sent on the trailing edge of the clock signal by the transmitter, and received on the leading edge of the clock signal by the receiver. The serial data is transmitted in two's complement with the MSB first. The MSB is transmitted first because the transmitter and the receiver may have different word lengths. There are four data word lengths supported by the QN8006; 8, 16, 24 and 32.

There are five data alignment modes supported by QN8006. The detailed timing descriptions are shown as below.

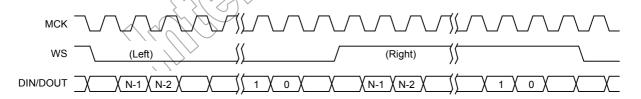

#### 6.3.1 MSB-Justified (Format 0)

The transmitter sends the MSB(N-1) bit of the next word when the WS changes and sends the second MSB bit in the next clock period. Each bit is sent by the transmitter in one clock period until the LSB (0) bit is sent. The N indicates the word length that can be 8, 16, 24, and 32.

This data alignment mode is supported by QN8006 as a receiver.

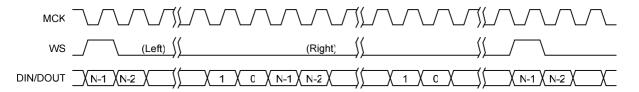

## 6.3.2 I<sup>2</sup>S (Format 1)

The transmitter sends the MSB (N-1) bit of the next word one clock period after the WS changes and sends the second MSB bit in the next clock period. Each bit is sent by the transmitter in one clock period until the LSB (0) bit is sent. In the case that the number of cycles equal the number of bits to be sent, the LSB (0) bit could be sent after the next WS change. The N indicates the word length that can be 8, 16, 24, and 32.

This data alignment mode is supported by the QN8006 as either receiver or transmitter.

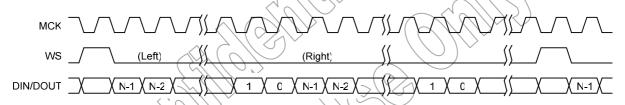

#### 6.3.3 DSP1 (Format 2)

The transmitter sends the MSB(N-1) bit of the next word when the WS pulse occurs and sends the second MSB bit in the next clock period. Each bit is sent by the transmitter in one clock period until the LSB (0) bit is sent. Following the first LSB, transmitter sends the MSB(N-1) bit of a new word and then keeps sending data until the data transmission is finished. The N indicates the word length that can be 8, 16, 24, and 32.

This data alignment mode is supported by the QN8006 as a receiver

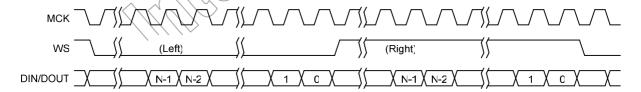

### 6.3.4 DSP2 (Format 3)

The transmitter sends the MSB(N-1) bit of the next word one clock period after the WS pulse occurs and sends the second MSB bit in the next clock period. Each bit is sent by the transmitter in one clock period until the LSB (0) bit is sent. Following the first LSB, transmitter sends the MSB (N-1) bit of a new word and then keeps sending data until the data transmission is finished. The N indicates the word length that can be 8, 16, 24, and 32.

This data alignment mode is supported by the QN8006 as either receiver or transmitter.

### 6.3.5 LSB-Justified (Format 4)

The transmitter sends the MSB(N-1) bit of the next word in the (N-1)th clock period back-counting from the next WS changes. The second MSB bit is sent in the next clock period. Finally, the LSB(0) bit is sent in the clock period that is just before the next WS changes in one clock period. The N indicates the word length that can be 8, 16, 24, and 32.

This data alignment mode is supported by the QN8006 as either receiver or transmitter.

### 7 USER CONTROL REGISTERS

----- THIS IS A PREVIEW LIST. Number and content of registers subject to change without notice ------

There are 31 user accessible control registers. All registers not listed below are for manufacturing use only.

**Table 16: Summary of User Control Registers**

| REGISTER | NAME       | USER CONTROL FUNCTIONS                                                                |

|----------|------------|---------------------------------------------------------------------------------------|

| 00h      | SYSTEM1    | Sets device modes.                                                                    |

| 01h      | SYSTEM2    | Sets device modes, resets.                                                            |

| 02h      | DEV_ADD    | Sets device address.                                                                  |

| 03h      | ANACTL1    | Analog control functions.                                                             |

| 04h      | REG_VGA    | TX mode input impedance, crystal cap load setting.                                    |

| 05h      | CIDR1      | Device ID numbers.                                                                    |

| 06h      | CIDR2      | Device ID numbers.                                                                    |

| 07h      | $I^2S$     | Sets I <sup>2</sup> S parameters.                                                     |

| 08h      | СН         | Lower 8 bits of 10-bit channel index                                                  |

| 09h      | CH_START   | Lower 8 bits of 10-bit channel scan start channel index.                              |

| 0Ah      | CH_STOP    | Lower 8 bits of 10-bit channel scan stop channel index.                               |

| 0Bh      | CH_STEP    | Channel scan frequency step. Highest 2 bits of channel indexes.                       |

| 0Ch      | PAC_TARGET | Output power calibration control.                                                     |

| 0Dh      | TXAGC GAIN | Sets TX parameters                                                                    |

| 0Eh      | TX_FDEV    | Specify total TX frequency deviation.                                                 |

| 0Fh      | GAIN_TXPLT | Gain of TX pilot frequency deviation, I <sup>2</sup> S buffer clear.                  |

| 10h      | RDSD0      | RDS data byte 0.                                                                      |

| 11h      | RDSD1      | RDS data byte 1.                                                                      |

| 12h      | RDSD2      | RDS data byte 2.                                                                      |

| 13h      | RDSD3      | RDS data byte 3.                                                                      |

| 14h      | RDSD4      | RDS data byte 4.                                                                      |

| 15h      | RDSD5      | RDS data byte 5.                                                                      |

| 16h      | RDSD6      | RDS data byte 6.                                                                      |

| 17h      | RDSD7      | RDS data byte 7.                                                                      |

| 18h      | RDSFDEV    | Specify RDS frequency deviation, RDS mode selection.                                  |

| 19h      | CCA        | Sets CCA parameters.                                                                  |

| 1Ah      | STATUS1    | Device status indicators.                                                             |

| 1Bh      | STATUS3    | RDS status indicators.                                                                |

| 1Ch      | RSSISIG    | In-band signal RSSI dBμV value.                                                       |

| 21h      | RSSIMP     | Multipath signal RSSI (Received signal strength indicator) DB value.                  |

| 22h      | SNR        | Estimated RF input CNR value from noise floor around the pilot after FM demodulation. |

| 49h      | REG_XLT3   | XCLK pin control.                                                                     |

| 4Fh      | REG_DAC    | DAC output stage gain.                                                                |

| REGISTER | NAME                                   | USER CONTROL FUNCTIONS |

|----------|----------------------------------------|------------------------|

| 59h      | 59h PAC_CAL PA tuning cap calibration. |                        |

| 5Ah      | PAG_CAL                                | PA gain calibration.   |

#### Register Bit R/W Status:

RO - Read Only: You can not program these bits.

WO - Write Only: You can write and read these bits; the value you read back will be the same as written.

R/W - Read/Write: You can write and read these bits; the value you read back can be different from the value written.

Typically, the value is set by the chip itself. This could be a calibration result, AGC FSM result, etc.

Word: SYSTEM1 Address: 00h

|   | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSB) |

|---|----------------|-------|-------|-------------|-------|-------|----------------|

|   | rxreq          | txreq | chsc  | stnby rxi2s | txi2s | rdsen | cca_ch_dis     |

| Ī | wo             | wo    | wo    | wowo        | wo (  | Wo    | > \ wo         |

| Bit | Symbol | Default    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | RXREQ  | 0 <        | Receiving request (overwrites TXREQ and STNBY):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|     |        |            | Non RX mode. Either IDLE, standby or TX mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|     |        |            | 1 Enter Receiving mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 6   | TXREQ  | $\bigcirc$ | Transmission request:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|     |        |            | 0 Non TX mode. Either IDLE, standby or RX mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|     |        |            | 1 Enter Transmit mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 5   | CHSC   | 0          | Channel Scan mode enable: Combined with TXREQ and RXREQ, chip scans for occupied channel for receiving or empty channel for transmission. After completing channel scanning, this bit will be cleared automatically. For CCS (TX Scan), the clearest channel (channel with weakest RSSI) will be selected (if TXCCAA is not equal to zero, another prior condition should be met, see description of CCA register at 19h).  For RX Scan, the FIRST valid channel will be selected. To start CCA/CCS, set CHSC (REG0 [5]) to 1. CHSH will be automatically cleared to 0 when CCA/CCS is complete. To use the scanned channel, set CCA_CH_DIS to 0. (CCA_CH_DIS can be set to 0 at the same time CHSC=1). |  |  |  |

|     |        |            | 0 Normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|     |        |            | 1 Channel Scan mode operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 4   | STNBY  | 0          | Request immediately to enter Standby mode if the chip is in IDLE and no TXREQ or RXREQ is received.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|     |        |            | 0 Non standby mode. Either IDLE, TX mode or RX mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|     |        |            | 1 Enter standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 3   | RXI2S  | 0          | I <sup>2</sup> S enable in receiving mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|   |            |   | 0 Use analog                                                                                              | output for RX audio.             |  |  |